Резервированный триггерный делитель частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТ8У

< 961153 (6l ) Дополнительное к авт. свид-sy 750743 (22) Заявлено 11. 11. 80 (21) 3001635/18-21 с присоединением заявки М (23) Приоритет— (51)М. Кл.

Н 03 К 23/02

Вкуааретеееыб квинтет

CCCP в делен нзебретеккк и открытий

ОпУбликовано 23. 09 82. Бюллетень ле 35

Дата опубликования описания 23 . 09 . 82 (53) УД К,бг1. 374. .4(088.8) (72) Авторы изобретения

А. Г. Азаров и Г. И. Цветков

1 г l !

Научно-исследова тел ьский институт à eтома тики. и электромеханики при Томском институте автоматизированных систем управления и радиоэлектроники (7I) Заявитель (54) РЕЗЕРВИРОВАННЫЙ ТРИГГЕРНЫЙ ДЕЛИТЕЛЬ

ЧАСТОТЫ

Изобретение относится к автоматике и вычислительной технике и может быть использовано, в частности, при построении надежных задающих генераторов.

Ло основному авт. св. 11 750743 известен резервированный триггерный делитель частоты, содержащий резервный триггер и каналы деления, каждый из которых включает в себя триггер, дополнительный элемент ИЛИ, элемент

ИЛИ-НЕ, две дифференцирующие цепи и элемент ИЛИ, причем вход триггера подключен к выходу элемента ИЛИ предыдущего канала деления, прямой выход триггера соединен с первым входом дополнительного элемента ИЛИ своего канала деления и с вторым входом дополнительного элемента ИЛИ последующего канала деления, инверсный выго ход упомянутого триггера соединен с первым входом элемента ИЛИ-НЕ своего канала деления и с вторым входом элемента ИЛИ-НЕ другого канала деле2 ния, выход дополнительного элемента

ИЛИ через первую дифференцирующую цепь подключен к одному из входов элемента ИЛИ, а выход элемента ИЛИНЕ через вторую дифференцирующую цепь подключен к другому входу элемента ИЛИ, при этом выходы резервного триггера и триггера последнего канала деления подключены к избирательному каскаду (1).

Недостаток известного устройства отказ делителя при одновременных отказах в двух соседних каналах деления, т. е. недостаточно высокая надежность работы.

Целью изобретения является повышение надежности работы устройства за счет устранения отказов при одновременных отказах в двух соседних каналах деления.

Для достижения цели в резервированный триггерный делитель частоты, содержащий резервный триггер и каналы деления, каждый из которых содер3 96115 жит триггер, вход которого подключен к выходу элемента ИЛИ предыдущего канала деления, вход резервного триггера подключен к выходу элемента ИЛИ последнего канала деления, а выходы через избирательный каскадк выходам триггера последнего канала деления, а каждый канал деления состоит из дифференцирующих цепей, дополнительного элемента ИЛИ и эле- 1р мента ИЛИ-НЕ, при этом в каждом- канале деления выход дополнительного элемента ИЛИ через первую дифференцирующую цепь подключен к одному из входов элемента ИЛИ, выход элемента 1<, ИЛИ-НЕ через вторую дифференцирующую цепь - к второму входу элемента ИЛИ, прямой выход триггера соединен с первым входом дополнительного элемента ИЛИ своего канала деления и с ув вторым входом дополнительного элемента ИЛИ последующего канала деления, а инверсный выход - с первым входом элемента ИЛИ-НЕ своего канала деления и с вторым входом элемента ИЛИ- д

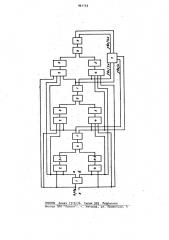

НЕ другого канала деления, первый дополнительный вход дополнительного элемента ИЛИ всех каналов деления, кроме первого, соединен с первой входной шиной, а остальные дополнительные входы дополнительного элемента ИЛИ в каналах деления, начиная с третьего, - с прямыми выходами триг. геров всех предыдущих каналов деления, первый дополнительный вход элемента ИЛИ-НЕ всех каналов деления, кроме первого, соединен с второй входной шиной, а остальные дополнительные входы элемента ИЛИ-НЕ в каналах деления, начиная с третьего, 10 с инверсными выходами триггеров всех, предыдущих каналов деления, при этом выходы триггера предпоследнего канала деления подключены к дополнительным входам избирательного каскада. 45 На чертеже представлена структурная схема резервированного триггерного делителя частоты для случая двукратного резервирования.

Устройство в каждом канале деления содержит триггер 1, элемементы ИЛИ

2 и 3, элемент ИЛИ-НЕ 4, дифференцирующие цепи 5-1 и 5-2, а также содержит резервный триггер 6, избирательный каскад 7, первую входную шину 8, на которую подается прямая импульсная последовательность, и вторую входную шину 9, на которую пода3 4 ется инвертированная импульсная последовательность.

Устройство работает следующим образом.

Прямой сигнал с каждого триггера

1 поступает одновременно на один из входов элемента ИЛИ 2 собственного канала деления и на один из входов всех элементов ИЛИ 2 последующих каналов деления. Инверсный сигнал с каждого триггера 1 поступает одновременно на один из входов элемента

ИЛИ-НЕ 4 собственного канала деления и на один из входов всех элементов

ИЛИ-НЕ 4 последующих каналов деления.

Выходные импульсы элементов ИЛИ 2 и ИЛИ-НЕ 4 поступают на дифференцирующие цепи соответственно 5-1 и 5-2 и далее на элемент ИЛИ 3, на выходе которого формируются узкие импульсы, запускающие последующий триггер 1 или

6. На вход избирательного каскада 7, который выделяет сигнал требуемой частоты, поступают сигналы с триггера

1 предпоследнего канала деления

= f!! /К, с триггера 1 последнего канала деления f = f „/2К и с резервного триггера 6 f > = f>Ä /4К, где

К вЂ” коэффициент деления, Пусть одновременно триггеры 1 в первом и втором каналах деления остановились в положении Q = 1. Тогда на выходе элементов ИЛИ 2 обоих каналов деления присутствует сигнал логической единицы, а на выходе элемента

ИЛИ-НЕ 4 присутствуют импульсы входной частоты, и делитель в целом продолжает Функционировать нормально, . так как на выходе резервного триггера 6, нагруженного на избирательный каскад 7, присутствуют импульсы требуемой частоты fe /К. Если триггеры

1 в первом и втором каналах деления одновременно остановились в положении Q = О, сигнал логической единицы будет на выходах элементов ИЛИ-НЕ 4 в обоих каналах деления, на выходе элемента ИЛИ 2 второго канала деления будут присутствовать импульсы входной частоты и делитель в целом продолжает функционировать нормально, так как на выходе резервного триггера 6 присутствуют импульсы требуемой частоты f „ /К.

Одновременный отказ двух любых элементов в соседних каналах деления также не приводит к каким-либо сбоям и переходным процессам в рассматриваемом делителе частоты. Это достига53

Формула изобретения

5 9611 ется тем, что в каждом канале деления прямой выход триггера 1 соединен не только с одним из входов элемента ИЛИ 2 собственного и следую щего каналов деления,. но и с одним из входов элемента ИЛИ 2 всех последующих каналов деления, а инверсный выход триггера соединен не только с одним из входов элемента ИЛИ-НЕ 4 собственного и следующего каналов, >6 но и с одним из входов элемента ИЛИНЕ 4 всех последующих каналов деления.

Характерной особенностью устройства является то, что повышение на- Ю дежности делителя достигается без дополнительных аппаратурных затрат.

Резервированный триггерный делитель частоты по ав. св. Й 750743, отличающийся тем, что, 1 2S с целью повышения надежности работы, первый дополнительный вход дополнительного элемента ИЛИ всех каналов деления, кроме первого, соединен с первой входной шиной, а остальные дополнительные входы дополнительного элемента ИЛИ в каналах деления, начиная с третьего, - с прямыми выходами триггеров всех предыдущих каналов деления, первый дополнительный вход элемента ИЛИ-НЕ всех каналов деления, кроме первого, соединен с второй входной. шиной, а остальные дополнительные входы элементов ИЛИ-НЕ в каналах деления, начиная с третьего; с инверсными выходами триггеров всех предыдущих каналов деления, при этом выходы триггера предпоследнего канала деления подключены к дополнительным входам избирательного каскада.

Источники инФормации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 750743, кл. H 03 K 23/02, 1977