Псевдостохастический интегратор

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик («)962938 (61) Дополнительное к авт. свид-ву(22) Заявлено 200231 (21) 3250961/18-24 (51)М Кп з с присоединением заявки М9

G 06 F 7/70

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет—

1 !

Опубликовано;30.09.82 Бюллетень М9 36

)53) УДК 681. 3 (088. 8) Дата опубликования описания 30.09.82 (72) Автор изобретения

В.М.Ерухимович

Специальное проектно-конструкторское и технологическое бюро по погружному электрооборудованию для бурения скважин и добычи нефти (71 ) 3a яв ит ель (54) ПСЕВДОСТОХАСТИЧЕСКИЙ ИНТЕГРАТОР

Изобретение относится к вычислительной технике и может быть использовано в стохастических вычислительных машинах.

Известны цифро-аналоговые интеграторы, в которых интегрируемые сигналы представляются в виде периодически детерминированных импульсных последовательностей, а роль интегратора выполняет накопительный счетчик импульсов (1 j и j21.

Известные устройства обладают высокой точностью, однако оказываются аппаратурно сложными при интегрировании с заданным весом, например при реализации спектрального или корреляционного анализа сигналов, ввиду сложности устройства умножения на входе интегратора.

Наиболее близким по технической сущности к предлагаемому устройству является стохастический интегратор, в котором интегрируемые сигналы представляются случайной последовательностью импульсов (Э).

Этот стохастический интегратор содержит генератор случайных чисел, например сдвиговый регистр с линей" ной обратной связью, декодирующий преобразователь, нуль-орган, нако,пительный счетчик, выходы разрядов которого являются выходами интегратора, первый вход нуль-органа подключен к выходу декодирующего преобразователя, а второй вход является входом интегратора, выходы разрядов сдвигового регистра с обратной связью присоединены к соответствую1ð щим входам декодирующего преобразователя.

Применение стохастического кодирования позволяет существенно упростить устройство для умножения интегрирующих сигналов.

Недостатком данного стохастичес,кого интегратора является значительная погрешность интегрирования,которая растет пропорционально време- ни интегрирования и обусловлена стохастической структурой последовательности на входе накопитель,ного счетчика.

Цель изобретения — повышение точности.

Поставленная цель достигается тем, что псевдостохастический интегратор, содержащий сдан говый регистр с линейной обратной связью,,тактовый вход которого является

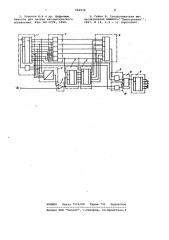

9б2938 тактовым входом интегратора, преобразователь код — аналог, входы- которого соединейы с соответствующими прямыми выходами сдвигового ре.— гистра с линейной обратной связью, нуль-орган, первый вход которого 5 соединен с выходом преобразователя код -аналога, а второй вход является входом интегратора,.накапли,вающий счетчик, выходы которого явI ляются выходами интегратора, допол- 10 нительно содержит счетчик, регистр, коммутатор, группу элементов И,первый и второй элементы И и элемент ИЛИ первый и второй входы которого соединены с выходами соответственно пер- 15 ваго и второго элементов И, а выход соединен со счетным входом накапливающего счетчика, выход нуль-органа соединен с первым входом второго элемента И и счетным входом счетчика, 2О группа выходов которого соединена с группой входов регистра, группа выходов регистра соединена с первой группой входов коммутатора, выход которого соединен с первым входом пер-у5 вого элемента И, первый вход каждого элемента группы элементов И соединен с прямым выходом соответствующего разряда сдвигового регистра с линейной обратной связью, а все остальные входы соединены с инверсными выходами всех старших разрядов регистра с линейной обратной связью, выходы группы элементов И соединены с второй группой входов коммутатора, инверс" ный и прямой выводы младшего разряда сдвигового регистра с линейной обратной связью соединены с вторыми входами соответственно первого и второго элементов И, управляющие . входы счетчика и регистра подключены к вы- 40 ходу младшего элемента группы элементов И. . На чертеже представлена блок.-схе-; ма интегратора.

Он содержит сдвиговый регистР 1 с 45 линейной обратной связью ... преобразователь 2 код-аналог, нуль-орган 3, накапливающий счетчик 4, счетчик 5, регистр б, группу элементов И 7,коммутатор 8,первый 9 и второй 10 элементы И, элемент ИЛИ 11.

Прямые выходы разрядов сдвигового . регистра 1 с линейной обратной связью соединены с соответствующими входами преобразователя код«аналог 2 .и первыми входами соответствующих элементов группы элементов И 7, все последующие входы каждого из которых соеди" иены с инверсными выходами всех старших разрядов сдвигового регистра 1 с линейной обратной связью. 60

Выход преобразователя. 2 код-аналог соединен с первым входом нуль-органа 3, выход которого соединен с первым входом второго элемента И 10 и счетным входом счетчика 5. Группа б5 выходов счетчика 5 соединена с груп- пой входов регистра б, группа выходов которого соединена с первой группой входов коммутатора 8.

Вторая группа входов коммутатора

8 соединена с выходами группы элементов И 7, а выход - с первым входом первого элемента И 9. Инверсный и прямой выходы младшего разряда сдвигового регистра 1 с линейной обратной связью соединены с вторыми входами соответственно первого 9 и второго 10 элементов И, выходы которых соединены соответственно с первым.и вторым входами элемента ИЛИ.

ll. Выход элемента ИЛИ 11 соединен со счетным входом накапливающего счетчика 4, Управляющие входы счетчика 5 и регистра б подключены к выходу младшего элемента группы элементов И 7.

В предлагаемом интеграторе реализуется численный метод интегрирования по формуле трапеций. Он работает следующим образом.

С момента подачи тактовых импульсов на шину сдвига, -разрядного сдвигового регистра 1 с линейной обрат. ной связью на выходах его и -разрядов генерируется имеющая период, 2" -1 тактов последовательность псевдослучайных чисел, которая преобразуется в псевдослучайный процесс с помощью преобразователя 2 код-аналог. После сравнения этого процесса с интегрируемым сигналом на выходе нуль-органа

3 образуется псевдослучайная импульсная последовательность, математическое ожидание которой пропорционально текущему значению интегрируемого сигнала.

Указанная последовательность в течение 2 — 1 тактов подается на вход и-разрядного счетчика 5. В счетчике 5 формируется усредненное за 2>- 1 тактов значение интегрируемого сигнала. Двоичный код счетчика 5 затем переписывается в ре" гистр б. После .записи кода счетчика

5 в регистр б счетчик 5 обнуляется и на его счетный вход вновь поступает последовательность с выхода нуль-органа 3 для формирования в двоичном коде последующего значения входного сигнала.

Импульсами управления записью в регистр б и обнулением счетчика 5 является сигнал, получаемый с выхода младшего элемента группы элементов И 7, который подхлючен к прямому выходу младшего разряда сдвигового регистра 1 с линейной обратной связью. В регистре б формируются отсчеты интегрируемого сигнала, сдвинутые по времени на шаг интегрирования, равный 2" - 1 тактов.

962938

Псевдослучайные последовательности с выходов разрядов сдвигового регистра 1 с линейной обратной связью (М-последовательности), имеющие математические ожидания, пропорциональI ные. 0,5, поступают также на входы группы элементов И 7, на выходах которых образуются последовательности с математическими ожиданиями,пропорциональными 2 +,0=1,2...,n.

Последовательности с выходов груп- 10 пы элементов И 7 поступают на вторую группу входов коммутатора 8, к первой группе входов которого подключена соответственно группа выходов регистра б. I5

На выходе коммутатора 8 образуется псевдослучайная последовательность математическое ожидание которой пропорционально значению содержимого

1 регистра 6. 20

На первые входы элементов Й 9 и

10 с выходов нуль-органа 3 и коммутатора 8 поступают последователь ности, математические ожидания которых пропорциональны текущему и 25 предыдущему значениям выходного сигнала.

Несовместимость последовательностей на входах элемента ИЛИ 11 обеспечивается подачей на вторые ф30 входы элементов И 9 и 10 соответственно прямой и инверсной М-последовательностей. Указанная М-последовательность, имеющая математическое ожидание, пропорциональное 0,5.посту- 35 пает с младшего разряда сдвигового регистра 1 с линейной обратной связью, что с погрешностью порядка 2 обеспечивает ее некоррелированность с последовательностями на выходах коммутаторов 8 и нуль-органа 3.

С помощью элементов И 9, 10 реализуется. операция умножения на

0,5 соответственно предыдущего и текущего отсчетов интегрируемого сигнала.

На выходе элемента ИЛИ 11 образуется последовательность, матема. тическое ожидание которой пропорционально полусумме значений текущего-и предыдущего отсчетов интегрируемого сигнала.

Последовательность с выхода эле" мента ИЛИ 11 поступает на вход накапливающего счетчика 4. Через интервалы времени, равные периоду работы сдвигового регистра 1 с линейной обратной связью, в счетчике 4 образуются текущие значения интеграла, вычисляемые по формуле трапеций с погрешностью порядка 2-". 66

Величина шага интегрирования

/ и

n=(2 — 1)7 (т - длительность тактовых импульсов) выбирается таКой, чтобы погрешность формулы трапеций не превышала по абсолютной величине 2-<"+ ). фЯ

Введение в стохастический интегратор счетчика, регистра, блока элементов И, коммутатора, двух элементов

И и элемента ИЛИ, соединенных соответствующим образом, позволяет реализовать численный метод интегрирования по формуле трапеций с погрешностью, не превышающей 2, т.е. существенно повысить точность стохастического интегратора.

Ъ формула изобретения

Псевдостохастический интегратор, содержащий сдвиговый регистр с линейной обратной связью, тактовый вход

:которого является тактовым входом йнтегратора, преобразователь код - . аналог, входы которого :соединены с соответствующими прямыми выходами сдвигового регистра с линейной обратной связью, нуль-орган, первый вход которого соединен с выходом преобразователя код — аналог, а второй вход является входом интегратора, накапливающий счетчик, выходы которого являются выходами интегратора,отличающ-ийся тем, что, с целью повышения точности, он содержит счетчик, регистр, коммутатор, группу элементов И, первый и второй элементы И и элемент ИЛИ, первый и второй входы которого -=-оединены с выходами соответственно первого и второго элементов И, а выход соединен со счетным входом накапливающего счетчика, выход нуль-органа, соединен с первым входом второго элемента И и сче гным входом счетчика, группа выходов которого соединена с группой входов регистра, группа выходов регистра соединена с первой группой входов коммутатора, выход которого соединен с первым вхоцом первого элемента И, первый вход.каждого элемента группы элементов И соединен с прямым выходом соответствующего разряда сдвигового регистра с линейной обратной связью, а все остальные входы соединены с инверсными выходами всех старших разрядов сдвигового регистра с линейной обратной связью, выходы группы элементов И соединены с второй группой входов коммутатора, инверсный и прямой выходы младшего разряда сдвигового регистра с линейной обратной связью соединены с вторыми входами соответственно первого и второго элементов

И, улравляющие входы счетчика и регистра подключены к выходу младшего элемента группы элементов И.

Источники информации, принятые во внимание при экспертизе

1. Ерухимович В.М. Интегрирование в вероятностно-импульсных АВМ.—

Известия вузов СССР. Электроника, 1971, Р 12, с. 1294-1297.

962938

ВНИИПИ Заказ 7514/69 Тираж 731 Подписное

Филиал ППП "Патент", r.Óæãîð0ä, ул.Проектная,4

2. Воронов A.A и др. Цифровые аналоги для систем автоматического управления. Изд. AH СССР, 1960.

3. Гейнс Б. Стохастическая вычислительная машина- Электроника, 1967, Р 14, с.3 - 11 (прототип).