Многоканальное устройство приоритета

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик

<1>962946 (61) Дополнительное к авт. свид-ву (22) Заявлено 12. 01. 81 (23) 3234154/18-24

Р М К з с присоединением заявки ¹

G F 9/46

Государственный Комнтет

СССР но делам изобретений н открытий (23) Приоритет (53) УДК 681. 325 (088.8) Опубликовано 3009.82. Бюллетень ¹ 36

Дата опубликования описания 30. 09. 82 (72) Авторы изобретения

И.И.Бахметьев, В.В.Тощев и A.Ä.Ùå÷êèí (71 ) Заявитель (54) ИНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА

Изобретение относится к вычислительной технике, в частности к устройствам приоритетного обслуживания запросов и может быть использовано в системах обработки данных.

Известно приоритетное устройство, содержащее регистр приоритета, счетчик, блок управления, циклический регистр сдвига, блок анализа счетчика на нуль и блок анализа старшего разряда циклического регистра сдвига на единицу (1 ).

Недостаток устройства — низкое быстродействие, обусловленное последовательным характером анализа приоритетов.

Наиболее близким по технической сущности к предлагаемому является многоканальное устройство приоритета, содержащее шифратор, каналы,в каждом из которых — элемент И, элемент НЕ и элемент ИЛИ (2g.

Недостаток устройства - ограниченные функциональные возможности, так - как изменение распределения запросов производится в паузах работы устройства при отсутствии из на входах.

Цель изобретения — расширение функциональных возможностей устройсТва за счет возможности перемены порядка обслуживания запросов в любой момент времени.

Поставленная цель достигается тем,. что в многоканальное устройство при- оритета, содержащее шифратор, выход которого является информационным выходом устройства, каналы, а в каждом канале — первый элемент И, первый элемент НЕ, элемент ИЛИ, регистр и коммутатор, причем каждый запросный вход у тройства соединен с первыми входами первого элемента И и элемента ИЛИ соответствующего канала, выход первого элемента HE каждого канала соединен с вторым вхоцом первого элемента И своего канала, каждый кодо-, вый вход устройства соединен с входом регистра соответствующего канала, выход регистра канала соединен с инфор ; мационным входом коммутатора своего, канала, выход коммутатора каждого ка, нала соединен с входом первого эле- мента НЕ своего канала и с вторым входом элемента ИЛИ своего. канала, выход элемента ИЛИ каждого канала соединен с соответствующими управляющими входами коммутаторов предыдущих и последующих каналов, разрешающий вход устройства соединен в каждом канале

З0 с управляющим входом коммутатора, 962946 соответствующим номеру канала, введены элемент ИЛИ и элемент НЕ, а в каждом канале-триггер, второй элемент НЕ и второй элемент И, причем запросный вход устройства через втоIpoA элемент HE соответствующего ка- 5 ,нала соединен с нулевым входом триггера своего канала, первый вход второго элемента И каждого канала соеди нен с выходом первого элемента И своФ

1 его канала, выход второго элемента И каждого канала соединен с единичным входом триггера своего канала, выход триггера каждого канала соединен с соответствующим входом шифратора, выход которого соединен с входом эле-15 мента ИЛИ, выход которого через элемент НЕ соединен с вторым входом второго элемента И каждого канала.

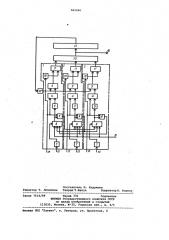

На чертеже приведена структурная схема устройства .

Многоканальное устройство приоритета имеет каналы 1-3, каждый из которых содержит элемент И 4, элемент

НЕ 5, коммутатор б, регистр 7, элемент ИЛИ 8, элемент И 9, элемент- НЕ 10 триггер 11, кодовые входы 12-14 устройства„ разрешающий вход 15 устройства, запросные входы 16-18 устройства, информационный выход 19, шифратор 20, элемент ИЛИ 21 и элемент НЕ 22.

Устройство работает следующим образом.

Перед началом работы на регистр 7 через входы 12-14 заносятся коды, которые совместно с коммутаторами б и

I элементами ИЛИ 8 обеспечивают началь- 35 ное распределение запросов по приори" тетам. По мере необходимости распределение приоритетов может динамически изменяться, для этого достаточно изменить содержимое регистров 7 сооТ 4р ветственно требуемому распределению запросов по приоритетам.

Необходимые кодовые комбинации на регистрах 7 определяются по следующим правилам. 45

1. Регистр 7 самого старшего по приоритету канала должен содержать код, равный номеру данного канала, обеспечивая подключение к выходу коммутатора б данного канала входа 15, подключенного к шине логического нуля.

Нуль на выходе коммутатора через элемент НЕ 5 разрешает прохождение запроса с входа 16 (или 17, .18) через И 4 дфиного канала на вход элемента И 9 этого канала. Кроме того, появление запроса на запросном входе данного канала вызывает последовательйую блокировку обслуживания остальных, более младших по приоритету каналов устройства через элемент ИЛИ 8 данного канала 60 и через коммутаторы б и элементы ИЛИ Ь остальных каналов °

2. Регистр 7 каждого последующего младшего по приоритету канала должен . содержать код, равный номеру предыду- 65 щего старшего по приоритету канала.

Например, регистр 7 для устройства, имеющего каналы 1-3 при распределении; (в порядке убывания) приоритетов 2, 1, 3 должен. содержать следующие кодыг.

Номер канала Код приоритет

1 1I2и

2 "2"

3 "1"

Указанные коды в регистрах 7 формируют структуру устройства таким образом, что появление запроса в старшем по приоритету втором канале устройства блокирует обслуживание запросов, возникших на входах каналов

1 и 3 устройства в порядке убывания приоритетов.

Код, равный двум, в регистре 7 канала 2, самого старшего по приоритету, вызывает появление нулевого уровня на выходе коммутатора б канала 2 (так как второй вход коммутатора б соединен с входом 15) и через элемент НЕ 5 обеспечивает прохождение запросов через элемент И 4 канала

2 на выход элемента И 9, открытого по второму входу элементом НЕ 22, а также обеспечивает установку в единичное состояние триггера 11, сигнал с единичного выхода которого поступает на соответствующий вход шифратора

20. Кроме того, на выходе элемента

ИЛИ 8 канала 2 при наличии запроса на входе 17 вырабатывается единичный сигнал, который блокирует через коммутатор 6 и элемент НЕ 5 канала 1 запрос с входа 16,так как код, равный двум, в регистре 7 канала 1 подключает второй вход коммутатора к его выходу.

Единичным сигналом с выхода элемента ИЛИ 8 канала 1 через первый вход коммутатора б и элемент НЕ 5 канала 3 блокируется обслуживание запроса, поступившего на вход канала 3, так как код, равный единице, в регистре 7 канала 3 подключает первый вход коммутатора б канала 3 к выходу этого коммутатора. Из комбинации сигналов на единичных выходах триггеров 11 (единичный сигнал всегда присутствует только на выходе одного триггера 11) шифратор. 20 формирует код номера приоритетного канала на выходе 19. этот же код поступает на элемент

ИЛИ 21, единичный сигнал с выхода . которого через элемент НЕ 22 запирает элементы И 9.

При перемене порядка обслуживания запросов при новом распределении запросов по приоритетам, возникший сигнал запроса в любом канале не пройдет через. соответствующий второй элемент И 9 до тех пор (чтобы не было ложного кода номера канала на выходе шифратора, пока не будет отслужен запрос возникший до

962946 перемены порядка обслуживания запросов. После этого снятый с соответствующего запросного входа сигнал устанавливает через второй элемент НЕ 10

1в нулевое состояние триггер 11. Нулевой сигнал с выхода шифратора через элемент ИЛИ 21 и элемент НЕ 22 разрешает прохождение возникшего сигнала запроса на выход шифратора 20.

Дальнейшая работа устройства проходит аналогично. 10

Отсутствие запроса на входе самого старшего по приоритету канала (в данном случае канала 2.) снимает последовательную цепь блокировок, вследствие,чего появляется возможность удовлетворения возникающих запросов по запросным входам каналов 1 и 3.

Применение изобретения позволяет расширить функциональные возможности устройства.

Формула изобретения

Многоканальное устройство приоритета, содержащее шифратор, выход которого является информационным выходом устройства, каналы, а в каждом канале — первый элемент И, первый эле— мент НЕ, элемент ИЛИ, регистр и коммутатор, причем каждый запросный вход >Зо устройства соединен с первыми входами первого элемента И и элемента ИЛИ соответствующего канала, выход первого элемента НЕ каждого канала соединен с вторым входом первого элемента

И своего канала, каждый кодовый вход устройства соединен с входом регистра соответствующего канала, выход регистра канала соединен с информационным входом коммутатора своего канала, 40 выход коммутатора каждого канала соединен с входом первого элемента НЕ своего канала и с вторым входом элемента ИЛИ своего канала, выход элемента ИЛИ каждого канала соединен с соответствующими управляющими входами коммутаторов предыдущих и последующих каналов, разрешающий вход устройства соединен в каждом кана ле с управляющим входом коммутатора, соответствующил но леру канала, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет возможности перемены порядка обслуживания запросов в любой момент времени, оно содержит элемент ИЛИ и элемент НЕ, а в каждом канале — триггер, второй элемент НЕ и второй элемент И, причем запросный вход устройства через второй элемент HZ соответствующего канала соединен с нулевым входом триггера своего канала, первый вход второго элемента И каждого канала соединен с выходом первого элемента.

И своего канала, выход второго элемента И каждого канала соединен с единичным входом триггера своего канала, выход триггера каждого канала соединен с соответствующим входом шифратора, выход которого соединен с входом элемента ИЛИ, выход которого через элемент НЕ соединен с вторым входом второго элемента И каждого канала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 506854, кл. G 06 F 9/22,1974., 2. Авторское свидетельство СССР

Р 679982, кл. G 06 F 9/22, 1977 (прототип) .

962946

Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035 Москва Ж-35 Ра окая наб. д.. 4/5

Заказ 7514/б9

t У у ую

Филиал 1ИП "Патент", r. Ужгород, ул. Проектная, 4

Составитель М. Кудряшев

Редактор T. Лонатина Техред Т.Фанта КорректорН. Король