Устройство для обнаружения сбоев синхронизируемой цифровой системы

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву (22) Заявлено 130281 (21) 3249902/18-24 f Sg) М Ктт з с присоединением заявки h92—

G 06 F 11/16

Государственный комитет

ССС P

II0 делам изобретений и открытий (23) Приоритет(53) УДК 681. 3 (088. 8>

Опубликовано 30.09.82. Бюллетень М 36

Дата опубликованмя описания 300982

В.П.Карчевский, Н.В.Карчевская, В.М.Ковтун и A.Ì.Òþëüòèí (72) Авторы .изобретения т <СМ@3Я Я

ПА ГЕРТИФ.

П- ХНИЧЕСКЛ% (71) Заявитель

Стахановский филиал Коммунарского горно-мета лургЫИЩффщц, института (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ СБОЕВ

СИНХРОНИЗИРУЕМОЙ ЦИФРОВОЙ СИСТЕМЫ

Изобретение относится к автомати- » ке и вычислительной технике и может найти применение для диагностирования синхронизируемых цифровых систем.

Для диагностирования сбоев в цифровых системах, в общем случае необходимо сбой обнаружить, зафиксировать, а затем дешифрировать результат для получения информации о месте сбоя..

Известно устройство для фиксации сбоев, которое содержит счетчик,дешифратор, два элемента ИЛИ, группу элементов И, реле времени, элемент

НЕ, генератор импульсов, формирователь, выходной регистр и регистр памяти 1 .

Однако данное устройство не позволяет. обнаружить сбои, возникающие в результате логических-гонок.

Наиболее близким по технической сущности к предлагаемому является дискриминатор логических сигналов, содержащий триггеры, к выходам которых, подсоединен .дешифратор для преобразования состояния указанных триггеров в сигналы, соответствующие определенным видам переходного процесса в исследуемой точке. Выходы дешифратора служат для визуального отображения изменения сигнала (2j.

С помощью дискриминатора логичес-, ких сигналов невозможно обнаружить сбой в некоторой линии передачи данных между блоками цифровой системы, так как кроме фиксации перехода сигнала от уровня логической "1" к уровню логического "0" и наоборот, необходима еще и фиксация момента времени, в которой этот переход совершен.. Последняя же не входит в функции дискриминатора.

Таким образом, дискриминатор логических сигналов не позволяет получить важную информацию, необходимую для локализации н .исправного блока в синхронизируемых цифровых системах.

Цель изобретения — расширение .функциональных возможностей устройства путем обнаружения сбоев, вызванных логическими состязаниями.

Поставленная цель достигается тем, что в устройство для обнаружения сбоев, содержащее H узлов контроля, в состав каждого из которых входят два триггера, элемент НЕ, элемент

И-НЕ, элемент индикации, причем в каждом узле контроля нулевые выходы первого и второго триггеров соедине962958 ны с соответствующими входами элемента И-1 Е, выход которого соединен с входом элемента индикации и является выходом узла контроля, информационные входы узлов контроля образуют группу информационных входов устрой- 5 ства, которая соединена с выходами .соответствующих блоков контролируемой системы, введены элемент И в каждый узел контроля, элемент ИЛИ-НЕ, причем первый и второй входы элемен- 1О та И соединены соответственно с входами синхронизации и управления данного узла контроля, выход элемента И соединен с М-входами первого и второго триггеров, й-входы которых объеди-15 иены и соединены с входом начальных установок узла контроля, информационный вход узла контроля соединен с Tвходом первого триггера и через элемент НЕ соединен с Т-входом второго триrrера, входы синхронизации всех узлов контроля образуют группу входов синхронизации устройства и соединены с соответствующими выходами блока синхронизации контролируемой системы, выходы узлов контроля соединены с соответствующими входами элемента ИЛИ-НЕ, выход которого соединен с входами управления всех канальных узлов и является выходом устройства, входы начальных установок-ЗО всех узлов контроля соединены с входом начальных установок устройства.

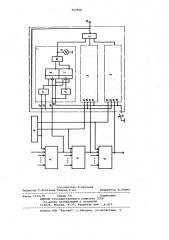

На чертеже приведена ;.структурная схема устройства для обнаружения сбоев контролируемой системы. 35

Предлагаемое устройство для обнаружения сбоев содержит элемент ИЛИ-НЕ

2, узлы 3 контроля, блок 4 синхронизации контролируемой системы, блоки

5 контролируемой системы, первый 40 триггер 6, второй триггер 7, элемент

НЕ 8, элемент И 9, элемент И-НЕ. 10, элемент 11 индикации, вход 12 синхронизации узла 3 контроля, вход 13 управления узла 3 контроля, информа- 45 ционный вход 14 узла 3 контроля, вход 15 начальных установок узла 3 контроля, выход 16 устройства, вход

17 начальных установок устройства.

Данное устройство предназначено для обнаружения сбоев, возникающих, в частности из-за логических состязаний в цифровых синхронизируемых системах. Они сопровождаются изменением выходных сигналов блоков во время синхроимпульса, то есть выход- ной сигнал не остается неизменным, равным "0" или "1", а изменяется от

"0" к "1" и наоборот однократно или многократно. На этом основывается принцип действия устройства. 60

Устройство работает следующим образом.

В начале работы по входу 17 начальных установок устроиства все узлы 3 контроля устанавливаются в на- . 65

4 чальное положение. На нулевых выходах триггеров устанавливаются сигналы "1", а на выходе элемента И-НЕ 10- сигнал "0", следовательно на элемент

11 индикации напряжение не поступает. Посредством элемента ИЛИ-НЕ-2 на всех входах 13 управления узлов 3 контроля устанавливаются сигналы "1".

Если в цифровой системе нет сбоев, то устройство функционирует следующим образом. С блока 4 синхронизации контролируемой системы на один из рабочих блоков 5 контролируемой системы и на один из узлов 3 контроля поступает синхроимпульс. На выходе блока 5 устанавливается сигнал "1" или сигнал "0".

Поступление синхроимпульса (уровень сигнала "1") на вход 12 синхронизации узла контроля вызывает сигнал "1". на выходе элемента И 9, а значит сигнал

"1" на входах триггеров 6 и 7. По этой причине становится возможной реакция триггеров 6 и 7 на изменение сигнала на Т-входах, один из которых подключен непосредственно к информационному входу 14 узла 3 контроля, а другой — к этому же входу через элемент HE-8, но при исправном функционировании блока 5, на выходе которого сигнал во время синхроимпульса не изменяется, а значит не изменяются сигнал на информационном входе 14 узла 13 контроля и состояние триггеров би 7.

Таким образом, Если в цифровой системе нет сбоев, то состояние всех узлов 3 контроля при функционировании системы не изменяется.

При возникновении сбоя в цифровой системе с блока 4 синхронизации контролируемой цифровой системы на один из рабочих блоков 5 контролируемой системы и на один из узлов 3 контроля, как и прежде, поступает синхроимпульс.

Но в этом случае на выходе блока

5 сигнал не устанавливается и изменяется от "0" до "1" или наоборот, возможно многократно. Поступление синхроимпульса на вход 12 синхронизации узла 3 контроля делает возможной, как уже рассматривалось, реакцию триггеров б и 7 на изменение сигнала на информационном входе 14. Причем из-за наличия двух триггеров 6 и 7 и элемента НЕ 8 первое жв изменение сигнала на информационном входе 14 от "0" до "1" или наоборот вызывает переброс одного из триггеров. На выхо де элемента И-НЕ 10 устанавливается сигнал "1" и элемент 11 индикации индицирует сбой. Источник сбоя однозначно определяется сработавыим узлом 3 контроля, который регистрирует первый сбой, что достигается наличи.ем обратной связи с выхода элемента ИЛИ-НЕ -2 на входы 13 управления ,всех узлов 3 контроля. При первом же перебросе триггера любого узла 3

962958 контроля сигнал "0" с выхода элемента ИЛИ-HE -2 поступает на вход управления узлов 3 контроля. На выходе элементов И 9 устанавливается сигнал "0", который поступает на .4-входы триггеров 6 и 7, в результате чего триггеры 6 и 7 перестают реагировать на сигналы, поступающие, на T-входы.

С выхода 16 устройства сигнал о возникновении сбоя может передаваться в блок управления цифровой системой для фиксации такта, на котором произошел сбой.

Таким образом, устройство позволяет определять сбои, вызванные логическими состязаниями. Возможность индикации узла контроля, первым обнаружившего сбой, повышает эффективность и надежность контроля.

Формула изобретения

Устройство для обнаружения сбоев синхронизируемой цифровой системы, содержащее И узлов контроля, в состав каждого из которых входят два триггера, элемент НЕ, элемент И-НЕ, элемент индикации, причем в каждом узле контроля нулевые выходы первого,и второго триггеров соединены с соответствующими входами элемента И-НЕ, выход которого соединен с

;входом элемента индикации и является выходом узла контроля, информационные входы узлов контроля образуют группу информационных входов устрой ства, которая соединена с выходами соответствующих блоков контролируемой системы, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет обнаружения сбоев, вызванных логическими состязаниями, в него введены элемент

И в каждый узел контроля, элемент

ИЛИ-НЕ, причем первый и второй входы элемента И соединены соответственно с входами синхронизации и управления данного узла контроля, выход элемента И соединен с Ч-входами первого и второго триггеров, R-входы которых объединены и соединены с установочным

15 входом узла контроля, информационный вход узла контроля соединен с Т-входом первого триггера и через элемент .НЕ соединен с -входом второго триггера, входы синхронизации всех уз2О лов контроля образуют группу входов синхронизации устройства и соединены с соответствующими выходами блока синхронизации контролируемой системи, выходы узлов контроля соединены р с соответствующими-входами элемента

ИЛИ-НЕ, выход которого соединен с входами управления всех канальных узлов и является выходом устройства, входы начальных установок всех узлов

ЗО контроля соединены с входом начальных установок устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 601695, кл. G 06 F 11/00, 1978.

2. Авторское свидетельство СССР

9 555354, кл . G 06 Р 11/04, 1975.

9á 2958

Составитель В.Т речнев

Редактор Т.Лопатина Техред А.Ач

Корректор Е.Рошко

Филиал ППП "Патент", r.Óæãîðoä, ул.Проектная, 4

Эаказ 7515/70 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5