Функциональный преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскими

Социалистических

Республик

««962973 (61) Дополнительное к авт. свид-ву (22) Заявлено 30.06.80 (21) 2982020/18-24 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 30.09.82. бюллетень ¹ 36

Дата опубликования описания 3009.82 (31) М. Ктт.з

G 06 F 15/31

Государственный комитет

СССР по делам нзобретеннй н открытий

1ЮЗ} УДК 681. 325 (088. 8) (72) Авторы изобретения

A.Н.Флоренсов, В.И.Потапов и И.Ю.Плотников

Омский политехнический институт, (7t) Заявитель.,(54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к вычислительной технике и может быть использовано для аппаратурной реализации функций в специализированных и универсальных быстродействующих цифровых вычислительных машинах.

Известен функциональный преобразователь, содержащий регистры старших и младших разрядов аргумента, блоки памяти, умножителя и сумматор (1).

Недостатком преобразователя является низкая точность преобразования °

Наиболее близким по технической сущности к предлагаемому является цержащее регистр стар ших разрядов аргумента, соединенный с адресными входами четырех блоков памяти, первый и второй иэ которых через первый коммутатор соединены с первым входом сумматора, другой вход которого через второй коммутатор подключен .к выходу регистра младших разрядов аргумента, а выход сумматора соединен с входом делителя блока деления и с выходным регистром 2 .

Недостатком данного устройства является необходимость применения двух последовательных операций деления, что существенно снижает его ,быстродействие. 30

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что преобразователь, содержащий четыре блока памяти, два коммутатора сумматор, регистр старших разрядов, регистр младших разрядов, блок деления, блок синхронизации и регистр результата, информационный вход которого соединен с выходом .сумматора и входом делителя блока деления, первый и второй входы сумматора соединены с выходами соответственно первого и второго коммутаторов, выход регистра старших разрядов соединен с информационными -входауи блоков памяти, выходы первого и второго из которых соединены с первым и вторым информационными входами первого коммутатора, выход регистра младших разрядов соединен с первым информационным. входом второго коммутатора, дополнительно введены блок умножения, первый и второй информационные входы которого соединены с выходами соответственно сумматора и регистра младших разрядов, выход блока умножения соединен с вторым информационным входом второго коюаутатора, третий информационный вход которого соединен с выхо.962971

ААмвох J при

Формула изобретения дом третьего блока памяти, выход четверто. о блока памяти соединен с входом делимого блока делЕния, выход которого соединен с третьим информационным входом первого коммутатора, первый выход блока синхронизации 5 соединен с управляющими входами всех блоков памяти, второй, третий, чет-вертый, пятый и шестой выходы блока синхронизации соединены соответственно с управляющими входами первого 10 коммутатора, второго коммутатора, блока умножения, блока деления и регистра результата.

Вычисление значений функции производится на основе следующих соотношений. Пусть задана функция F(x), О ах В<1, удовлетворяющая условию

1F(x)) 1, значения аргумента х представляются и-разрядным двоичным кодом, а значения функции у = F(x) требуется находить с и-верными двоичными цифрами после запятой.

Разобьем аргумент х = 0, х„.х ...х„, в сумму двух слагаемых хд = О, х ° х0 *0 идх0 0е* ° 0

4 К 25 х, х„ х = х+ дх, Расчеты показывают, что значения заданной функции Р(х) можно аппрокси. миров ать вираже вием

u(>= (Wо)ьаХ(А(Ао) Е(В 1,„) у) где F (xo) А(хо) А В (х, ), С (х, ) висят только от промежуточного аргумента хо, но не зависят от д х и определяются следующим образом:

А(Х )ж 6.(o)-© (Wo) f Фэ(Хо);

И о)--Ф ((О) I ©,((О)

С(Xp) =-(b<(Xp) Ф (Хо) с ф„(7).= —,, " (Z), <=-<,4.

Значение параметра k для получения верными всех двоичных разрядов результата и необходимо взять из выражения . ", gg(g+)yegg g) (4 )

45 к

О<, Я.-"

50 где значение коэффициентов F(x ), А (xp), В (xo) С (х„) предварительно рассчитываются по указанным формам и запоминаются по соответствующим адресам блоков памяти предлагаемого 55 устройства.

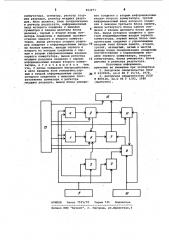

На чеРтеже представлена блок-схема преобразователя.

Устройство содержит блоки 1-4 памяти, регистр 5 старших разрядов, 40 коммутатор 6, сумматор 7, коммутатор 8,.блок 9 деления, регистр 10 младших разрядов, блок 11 умножения, регистр 12 результата, блок 13 синхронизации . 65

Преобразователь работает следующим образом.

В первом такте по адресу х, передаваемому с выхода регистра старших разрядов аргумента 5 на входы блоков 1-4 памяти, на выходах которых появляются соответственно значения коэффициентов F(х ), С(х„), А(х ), B(xo) . По сигналам блока 13 синхронизации, поступающим на первый и второй коммутаторы 6 и 8, значения

С(хо) с выхода блока 2 памяти и ьх с выхода регистра 10 младших разрядов аргумента поступают на. входы сумматора 7, на выходах которого

Формируется значение С(х ) + д х, Во втором такте работй по сигналу иэ блока 13 синхронизации, поступающему на блок 9 деления, на его входы поступают значения В(хо) с выхода блока 4 памяти и С(х,,) + b x с выхода сумматора 7. При этом на выходе блока деления формируется частное В (х. ) /(С (х, ) + д x) .

В третьем такте работы по сигналу из . блока 13 синхронизации,поступающему на блок 11 умножения, значение cyme с выхода сумматора 7 и значение А(х ) с выхода регистра, 10 младших разрядов аргумента поступают на входы блока 11 умножения, на выходе которого формируется произведение (А(х„) + В(хо) /(C(xo) +bx)) b x

В последнем, пятом, такте работы устройства произведение с выхода блока 11 умножения и его значение

"(xo).под действием сигналов из блока 13 синхронизации, поступающих на первый и второй коммутаторы 6 и 8, передаются на входы сумматора 7, на выходе которого образуется сумма

F(x) =Е(х; )+(А (х„)+B(xo)/(Ñ(xp.)+äx)) Ьх

По сигналу иэ блока 13 синхронизации значение F(x) с выхода сумматора 7 передается на регистр 12 результата.

Таким образом, время Т„, требуемое для вычисления эначенйя функции в предлагаемом устройстве, составляет Т = 3t + де + t>z,. В то же время для устройства прототипа время вычисления функции определяется

Тя = 4 с +2 дел

Полагая, что „ер 2 „„,(умножение с анализом двух разрядов множителя), получаем

3t + З, А

Т„= 4 + 4t„ .

Таким образом, предлагаемое устройство обеспечивает выигрыш во времени на 25% по сравнению с известным устройством, что существенно повышает его быстродействие.

Функциональный преобразователь, содержащий четыре блока памяти,два

962971

ВНИИПИ Заказ 7515/70 Тираж 731 Подписное

Филиал ППП "Патент", r. Ужгород, ул.Проектная,4 коммутатора, сумматор, регистр старших разрядов, регистр младших разрядов, блок деления, блок синхронизации и регистр результата, информационный вход которого соединен с выходом сумматора и входом делителя блока деления, первый и второй входы сумМатора соединены с выходами соответственно первого и второго коммутаторов, выход регистра старших разрядов соединен с информационными входа- lO ми блоков памяти, выходы первого и второго из которых соединены с первым и вторым информационными входами первого коммутатора, выход регистра младших разрядов соединен с первым !5 информационным входом второго коммутатора, о т л и ч à ro ta и и с я тем, что, с целью повышения быстродействия, в него введены блок умножения,первый и второй информационные входы 2О которого соединены с выходами соответственно сумматора и регистра младших разрядов, выход блока умноже1 ния соединен с вторым информационным входом второго коммутатора, третий информационный вход которого соединен с выходом третьего блока памяти, выход четвертого блока памяти соединен с входом делимого блока деления, выход которого соединен с третьим информационным входом первого коммутатора, .первый выход блока синхронизации соединен .с управляющими .входами всех блоков памяти, второй, третий, четвертый, пятый и шестой выходы блока синхронизации соединены

coответственно с управляющими входами первого коммутатора, второго коммутатора, блока умножения, блока деления и регистра результата.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 6220906, кл.б 06 F 15/34, 1978.

2. Авторское свидетельство СССР

В 809126, кл.6 06 F 1/02, 1980 (прототип) .