Нелинейный интегратор

Иллюстрации

Показать всеРеферат

Союз Советских.

Социалистических

Республик

<>962990

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт, свид-ву (22) Заявлено 06.02. 81 (21) 3245456/18-24 (51) М. Кл.з с присоединением заявки N

6 06 С 7/18

Государственный комитет

СССР ио делам изобретений и открытий (23) Приоритет

Опубликовано 300982. Бюллетень ¹36 (53) УДК 681. 335 (088,8) Дата опубликования описания 30.09.82 (72) Авторы изобретения

A.Á.Ëàíäûøeþ, Ю.A.Ìåäâåäåâ и В.В.Сергеев

Владимирский политехнический институт 1 (71 ) 3a яв и тель (54) НЕЛИНЕЙНЫЙ ИНТЕГРАТОР

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве корректирующего устройства, например, для повышения порядка астатизма и улучшения качества переходных процессов систем автоматического ynpasления, работающих в условиях помех.

Известен интегрирующий преобразователь постоянного, напряжения, содержащий линейный интегратор, два ключа, формирователь импульсов, масштабный резистор и блок постоянного запаздывания, который введен в устройство с целью повышения коэффициента подавления помех преобразователя при .изменении. частоты помехи (1 .

Однако данное устройство предназначено для интегрирования только постоянного напряжения и не интегрирует сигналы переменного напряжения. Кроме того, недостаточным коэффициентом подавления помех устрой ство обладает лишь в ограниченном диапазоне изменения частоты помехи, а выходной сигнал устройства имеет отрицательный фазовый сдвиг по отношению к.входному сигналу.

Известно также нелинейное интег. рирующее устройство, содержащее два линейных интегратора, образующих две цепи интегрирования, первая из которых служит для интегрирования положительных сигналов, вторая для отрицательных, усилительный элемент и суммирующий усилитель (2).

Существенными недостатками указанного устройства являются отсутствие помехоэащищенности и отрицательный фазовый сдвиГ между синусоидальным входным сигналом и первой гармоникой выходного сигнала.

Наиболее близким к предлагаемому по технической сущности является нелинейный интегратор, который содержит линейный интегратор, переключающее устрОйство и устройство для

20.сравнения знаков 3).

Существенным недостатком данного интегратора является отсутствие помехозащищенности, так как наличие помехи во входном гармоническом сиг25 нале приводит к ложным срабатываниям устройства для сравнения знаков, что вызывает ложные срабатывания . переключающего устройства, частота которых определяется частотой помехи. Кроме того, фазовый сдвиг между

962990

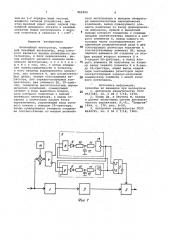

На фиг. 1 приведена схема предлагаемого интегратора, на фиг. 2 временные диаграммы при гармоническом входном сигнале, на фиг. 3 то же, при наличии высокочастотной помехи на гармоническом входном сигнале (временные диаграммы при работе генератора высокочастотных периодических колебаний для гармони= чеакого входного сигнала аналогичны временным диаграммам на фиг,3).

Нелинейный интегратор содерх<ит линейный интегратор 1, блок 2 переключения, блок 3 выделения модуля, 55

60 входным сигналом и первой гармоникой выходного сигнала нелинейного интегратора равен 0, что не позволяет использовать устройство в тех системах автоматического управления, где необходим положительный фазовый 5 сдвиг.

Цель изобретения — повышение помехозащищенности и точности регулирования.

Указанная цель достигается тем, .10 что в нелинейный интегратор, содер>кащий линейный интегратор, вход которого является входом нелинейного интегратора, и блок переключения, выход которого является выходом нелинейного интегратора, введены формирователь импульсов, два элемента

И, два разделительных диода, четыре токозадающих резистора, два зарядно-разрядных. конденсатора, два эдемента НЕ, SR-триггер, генератор высокочастотных периодических колебаний, суммирующий элемент и блок выделения модуля, вход которого подключен к выходу линейного интегратора, а выход соединен с сигнальным входом блока переключения, управляющий вход которого связан с выходом SR-триггера, входы суммирую= щего элемента соединены соответственно со входом нелинейного интегратора и выходом генератора высокочастотных периодических колебаний, выход суммирующего элемента подключен ко входу формирователя импульсов, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов

И, выход ках<дого из которых через последовательно соединенные разделительный диод и два токозадающих ре- 40 зистора подключен к соответствующему элементу НЕ, выход первого элемента

НЕ соединен со вторым входом второго элемента И и S-входом SR-триггера, а выход второго элемента НЕ 45 подключен ко второму входу первого элемента И и R-входу SP. — òðèããåðà, общий вывод каждой пары токозадающих резисторов через соответствующий зарядно-разрядный конденсатор соединен с шиной нулевого потенциала. формирователь 4 импульсов, SR-триг-. гер 5, первый 6 и второй 7 логические блоки, каждый из которых состоит из элемента И 8, разделительного диода 9, первого 10 и второго 11 токозадающих резисторов, зарядно-разгрузочного конденсатора 12 и элемента HE 13, генератор 14 высокочастотных периодических колебаний и суммирующий элемент 15, Кроме того, на фиг. 2 и 3 приняты следующие обозначения: U — напряжение на входе формирователя 4 импульсов, U и 0 — напряжения на неинвертирующем и инвертирующем выходах формирователя 4 импульсов соответственно, U — напряжение на конденсаторе 12, U< — напряжение на выходе нетактируемого ЯН-триггера 5;

U@ — напряжение на, выходе линейного

1 ийтегратора 1, Ць - напря>кение на выходе блока 3 выделен ия модуля, напряжение <>а выходе блока 2 переключения.

При подаче на вход устройства гармонического сигнала OH интегрируется линейным интегратором 1 и через блок 3 выделения модуля поступает на первый вход блока 2 переключения. Одновременно входной сигнал поступает на вход формирователя 4 импульсов, при этом на неинвертирующем выходе формирователя 4 импульсов импульсы формируются в момент изменения полярности входного сигнала с отрицательной на положительную, а на инвертирующем — с положительной на отрицательную. Неинвертирующий выход формирователя 4 импульсов подключен к первому входу логического блока б, а ийвертирующий — к первому входу логического блока 7, выход первого логического блока б подключен ко второму входу второго логического блока 7, а выход второго логического блока 7 — ко второму входу первого логического блока б, Выходные сигналы логических блоков б и 7 управляют работой нетактируемого SR-триггера, выход которого подключен ко второму входу блока 2 переключения. Работа блока 2 описываетая уравнением

Г

)Ug j HpH U = "1"

lU6 l ITp>< U+ = "0"

В момент времени t (фиг.2) формируется импульс на неинвертирующем выходе формирователя 4 импульсов, а сигналы на вторых входах логических блоков б и 7 соответствуют логической единице, при этом сигналом положительной полярности с выхода элемента И 8 заряжается конденсатор 12 через диод 9 и резистор 10. Разряд конденсатора 12 происходит через резистор 11 на вход элемента НЕ 13, 962990 причем постоянная времени заряда конденсатора 12 значительно меньше постоянной времени разряда конденсатора 12. Выходной сигнал элемента

НЕ 13, соответствующий логическому нулю, устанавливает триггер 5 в состояние, при котором выходной сигнал триггера 5 соответствует логической . единице, при этом напряжение на выходе нелинейного интегратора равно

) Ugf (фиг.2, интервал времени t„ -tz).

В момент времени t (фиг.2) фор мируется импульс на инвертирующем выходе формирователя 4 импульсов, и на входе логического блока 7 (по аналогии с логическим блоком б) формируется импульс, который изменяет состояние триггера 5 на противоположное, т.е. выходной сигнал триггера 5 соответствует логическому нулю, нри этом напряжение на выходе нелинейного интегратора — Б / (фиг.2, интервал времени t> -t>).

C момента времени t> (фиг.2) работа устройства повторяется.

При подаче на вход устройства гармонического сигнала с высокочастотной помехой (фиг.3) в момент времени tq формируется импульс на неинвертирующем выходе формирователя

4.импульсов, а сигналы на вторых входах логических блоков б и 7 соответствуют логической единице, при этом сигналом положительной полярности с выхода элемента И 8 эаI ряжается конденсатор 12 через диод

9 и резистор 10. Разряд конденсатора 12 происходит через резистор 11 на вход элемента НЕ 13, причем постоянная времени заряда конденсатора

12 значительно меньше постоянной времени разряда конденсатора 12. Выходной сигнал элемента НЕ 13, соот-. ветствующий логическому .нулю, блокирует работу второго логического блока 7 и устанавливает триггер 5 в состояние, при котором выходной сигнал триггера 5 соответствует логической единице, В момент времени t>.ôî@ мируется импульс на инвертирующем выходе формирователя 4 импульсов, но сигнал на выходе логического блока.7 не меняет caoего значения,. поскольку на втором входе логического блока 7 присутствует сигнал, соответствующий логическому нулю, и состояние триггера 5 не меняется.

Следующее изменение полярности сиг-, нала, поступающего на вход нелинейного интегратора (фиг.3, момент времени t3), формирует импульс йа неинвертирующем выходе формирователя 4 импульсов, при этом сигналом положительной полярности с вьхода элемента И 8 через диод 9 и резистор 10 подзаряжается конденсатор i=, Такой подзаряд и разряд кондеисатора 12 происходит до тех пор, пока изменяется полярность входного сигнала из-за наличия помехи, т.е. до момента времени 14 . Таким образом, напряжение на выходе нелинейного интегратора в интервале времени л tg pctBHo 1 Ug ((Фиг, 3) °

В момент времени t формируется импульс на инвертирующем выходе формирователя 4 импульсов, а сигналы 0 на вторых входах логических блоков б и 7 соответствуют логической едини-. це, при этом работа логического блока 7 аналогична работе логического блока б, описанной выше, а напряже35 ние на выходе нелинейного интегратора в интервале времени t+-t равно— U6 t (фиг. 3) .

Таким образом, наличие высокочастотной помехи во входном гармоничесщ ком сигнале не приводит к ложным

° срабатываниям блока переключения, нри этом первая гармоника выходного сигнала устройства имеет положительный фазовый сдвиг по отношению к вы25 ходному сигналу

Кроме того„ для регулирования фазочастотной характеристики нелинейный интегратор содержит генератор 14 высокочастотных периодических колебаний и суммирующий элемент 15, выход которого подключен ко входу формирователя импульсов, первый вход— ко входу устройства, а второй входвыходу генератора 14:высокочастотных периодических колебаний.

При этом устройство работает следующим образом.

Гармонический сигнал, поступающкй на вход устройства, интегриру4 ется линейным интегратором 1 и через блок 3 выделения модуля подается на первый вход блока 2 переключения. Одновременно входной сигнал йоступает на первый вход суммирующего элемента 15, на второй вход суммирующего элемента 15 подается выходной сигнал генератора 14 высокочастотных периодических колебаний.

Выходной сигнал суммирующего элемента 15. поступает на вход формирователя импульсов. При этом нелинейный интегратор работает таким же образом, как и в случае подачи на вход устройства гармонического сигнала с высокочастотной помехой, а работа устройства характеризуется временными диаграммами, приведенными на фиг. 3.

Желаемую фазочастотную характеристику нелинейного интегратора можно получить, изменяя амплитуду выходно49 го сигнала генератора 14 высокочастотных периодических колебаний, а точность регулирования фазочастотной характеристики определяется частотой выходного сигнала. генератора

14, которая должна быть не менее

962990 чем на 1-2 порядка выше частоты входного сигнала устройства, при этом фазовый сдвиг между первой гар! моникой выходного сигнала и входным сигналом можно регулировать с высокой точностью в пределах 0 = =90 формула изобретения

Нелинейный интегратор, содержащий .линейный интегратор, вход кото рого является входом нелинейного интегратора, и блок переключения, выход которого является выходом нелинейного интегратора, о т л и ч а ю— шийся тем, что, с целью повышения помехозащищенности и точности, в него введены формирователь импульов, два элемента И, два разделительных диода, четыре токозадающих резистора, два зарядно-разрядных конденсатора, два элемента НЕ, SR-триггер, генератор высокочастотных периодических колебаний, суммирующий элемент и блок выделения модуля, „ вход Которого подключен к выходу линейного интегратора, а выход со- . единен с сигнальным входом блока переключения, управляющий вход которого связан с выходом SR-триггера, входы суммирующего элемента соединены соответственно со входом нелинейного интегратора и выходом генератора. высокочастотных периодических колебаний, выход. суммирующего эле-. мента. подключен ко входу формирователя импульсов, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И, выход каждого из которых через последовательно соединенные разделительный диод и два

® токозадающих резистора подключен к соответствующему элементу НЕ, выход первого элемента НЕ соединен со вто рым входом второго элемента И и

S-входом SR-триггера, а выход вто15 рого элемента НЕ подключен ко второму входу первого элемента И и R-входу SR-триггера, общий вывод каждой пары токозадающих резисторов через соответствующий зарядно-разрядный

QQ конденсатор соединен с шиной нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

0627487, кл. G Об G 7/18, 1978 °

2.. Тэлер Цж. и Пестель М, Анализ и расчет нелинейных систем автоматического управл ния, М,-Л., "Энергия"

1964, с. 379, рис. 8-20.

3. Авторское свидетельство СССР

9244725, кл. G. 06 G 7/18, 1969.

Составитель С.Белан

Техред А.Бабинец Корректор С,Шекмар

Редактор Ю.Ковач

Филиал ППП. "Патент", г. Ужгород, ул, Проектная, 4

Закаэ 751б/71 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5