Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сою» Советских

Социалистических

Ресттублик

«i 963102 (6l ) дополнительное к авт. свив-ву (22)Заявлено 30.06.80 (2!) 2950398/18-24 (51) M. Кл.

G,,ll С 19/00 с присоединением заявки М

9вудврвтввввый квмитет

СССР ав Аелвм изобретений и атврыткй (23 ) П р и ори тет

Опубликовано 30. 09. 82. бюллетень М 36 (53) ЯК 681 ° 327..67088.8) З,ата опубликования описания 30. 09. 82

В. П. Артеменко, В. И. Аствацатуров и И. О. Жученко (72) Авторы изобретения

Опытное конструкторско-технологическое бюро

Института металвюфизики АН Украинской CCP" . ---. (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля и управления произ- . водственными процессами, а также в устройствах отображения информации на ЭЛТ.

Известно циклическое запоминаюшее устройство, содержащее накопитель, блок синхронизации, дешифратор, сумматор, обеспечивающее селективное управление временем хранения информации (1 ).

Информация в таком запоминающем устройстве не может долго хранить" ся в накопителе и нуждается в регенерации.

Известно также запоминающее устройство, применяемое как приставка к осциллографу, которое содержит що статическое полупроводниковое запоминающее устройство, цифро-аналоговый преобразователь, аналого-:: цифровой преобразователь, счетчик управления адресами, управляющее устройство, коммутатор, и применяется вместо дорогостоящих запомина" ющих ЭЛТ (2)...

Недостаток устройства заключается в том, что оно имеет довольно сложную организацию.

Наиболее близким К предлагаемому является .запоминающев устройство, содержащее генератор импульсов," кольцевые сдвиговые регистры, счетчик, дешифратор, сумматор, элементы И по количеству ячеек сдвигового регистра, блоки записи-считывания (3).

Недостатком этого устройства является наличие счетчика, дешифратора, элементов И по количеству ячеек сдвигового регистра и сумматора, что приводит к излишним аппаратурным затратам.

Цель изобретения - упрощение устройства.

3102

46

56

3 96

Указанная цель достигается тем что в запоминающее устройство, содержащее сдвиговые регистры, выходы которых подключены к первому входу соответствующего блока записи-считывания и является выходом устройства, а вход - к выходу соответствующего блока записи-считывания, вторые входы блоков записи-считывания являются входами устройства, генератор импульсов, выход которого подключен к тактовым входам двиговых регистров, а вход генератора импульсов является тактовым входом устройства, дополнительно введены синхронизатор и блок управления, (выход которого подключен к управляющим входам блоков записи-считывания, а вход -к выходу синхронизатора, управляющие входы синхронизатора подключены к соответствующим выходам блока управления, тактовый вход синхронизатора подключен к выходу генератора импульсов, входы блока управления являются входами устройства.

Кроме того, синхронизатор содержит элементы И, элементы ИЛИ, запоминающие ячейки и группу соединенных последовательно запоминающих ячеек, выход последней из которых является выходом синхронизатора и подключен к входу первой запоминающей ячейки, а вход первой - к выходу элемента ИЛИ, выход первой запоминающей ячейки подключен к входу первого элемента И и к входу второй запоминающей ячейки, выход которой подключен к первому входу второго элемента И и к входу третьей запоминающей,ячейки, выход третьей запоминающей ячейки подключен к первому входу третьего элемента И, тактовые входы запоминающих ячеек и соединенных последовательно запоминающих ячеек группы подключены к тактовому входу синхронизатора, выходы элементов, И подключены к соответствующим входам элемента ИЛИ, вторые входы элементов И являются управляющими входами синхронизатора.

Кроме того, блок управления содержит элементы И, элемент ИЛИ, элемент ИЛИ-НЕ и триггер, выход которого подключен к первым входам первого, второго и третьего эле" ментов И, вход триггера подключен к выходу четверто|го элемента И, первый: вход которого является входом блока ф управления, второй вход четвертого элемента И подключен к выходу элемента ИЛИ, входы которого подключены к вторым входам соответствующих элементов И и являются входами блока управления, выходы первого и второго элементов И являютая управляющими выходами блока управления, выходы первого и второгО элементов И являются управляющими выходами блока управления и подключены к соответствующим входам элемента ИЛИ-НЕ, выход которого является выходом блока управления.

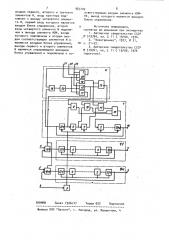

На чертеже представлена блоксхема предлагаемого устройства.

Устройство содержит сдвиговые регистры 1, запоминающие ячейки 2 сдвиговых регистров, выходы 3 сдвиговых регистров, блоки 4 записисчитывания с входами для подклю .чения внешних устройств 5, генератор

6 импульсов, синхронизатор 7, вход 8 внешнего тактирующего сигнала, элементы И 9-l2 элемент ИЛИ-НЕ 13, элемент И 14, блок 15 управления, элемент ИЛИ 16, элемент И 17 и 18, выход синхронизатора 19, элемент ИЛИ 20, входы 21 сигналов "Запись-считывание", 22 "Сдвиг влево", 23 "Сдвиг вправо" и триггер 24.

Количество сдвиговых регистров в предлагаемом запоминающем устройстве, т.е. число необходимых каналов для записи и хранения информации, может быть любым (цифрами в скобках показаны номера каналов от 1. до и), а длина сдвиговых регистров может быть также любой и выбирается исходя из необходимого объема хранимой информации (цифрами в скобках показаны номера ячеек сдвиговых регистров от 1 до n). Все сдвиговые регистры имеют обратную связь с выхода на вход, т.е. замкнуты в кольцо.

Устройство работает следующим образом.

При подаче сигнала "Запись-считывание" на вход 21 (логическая "1") устанавливается логическая",1" на входе элементов l? и 20 блока 15 управления. Логическая "1" с выхода элемента 20 разрешает прохождение оигнала с выхода синхронизатора 19 на вход триггера 24. Последний Формирует разовый сигнал, который поступает на вход элемента 17 и по совпадению с сигналов "Запись-считывание". элемента 17 вырабатывается сигнал

963102

5 управления блоками записи-считывания.

По этому сигналу блоки записисчитывания разрывают связь выходов кольцевых сдвиговых регистров 3 с входами и образуют связь выходов внешних устройств 5 с входами сдвиговых регистров, т.е. производится запись с внешних устройств в запоминающее устройство. Образовавшаяся 10 таким образом связь разрывается по окончании управляющего сигнала с выхода элемента 17 и восстанавливается связь выходов с входами сдвиговых регистров. lS

Генератор 6 импульсов вырабатывает серию тактовых сигналов, синхронных с внешним тактовым сигналом,8, которые тактируют работу сдвиговых .регистров и синхронизатора 7.

При поступлении сигналов "Сдвиг влево" 22 или "Сдвиг вправо" 23 триггер 24 как и в режиме записи-считывания вырабатывает разовый сигнал логической "1", который ФОРмирует соответственно логическую "1" элемента 14 или элемента 12. Логическая "1" с выхода элемента 14 или

12 поступает на вход элемента 9 или

10, удлиняя либо укорачивая соответственно длину сдвигового регистра синхронизатора íà и бит (длина ячейки 2), При увеличении или уменьшении периода синхронизатора на и бит информация на входах запоминающего устрой3S ства сдвигается влево или вправо на и бит относительно сигнала на выходе 19 синхронизатора 7. Многократно подавая сигнал сдвига, выводят 0 любой участок записанной информации на выход запоминающего устройства.

Применение предлагаемого запоминающего устройства для отображения цифровой информации на экране ЭЛТ поз4S воляет обходиться без дорогостоящих запоминающих осциллографов и значительно упрощает процесс настройки и отладки цифровых систем.

Кроме того, применение запоминающего устройства в качестве приставки к осциллографу позволяет запоминать сигналы на сколь угодно большой период времени.

Возможно также применение предлапаемого устройства в комбинации с

АПЦ и ЦАП для хранения и визуализиции аналоговых сигналов.

Формула изобретения

1.. Запоминающее устройство, содержащее сдвиговые регистры, выходы которых подключены к первому входу соответствующего блока записи-считывания и являются выходом устройства, а вход - к выходу соответствующего блока записи-считывания, вторые входы блоков записи-считывания являются входами устройства, генератор импульсов, выход которого подключен к тактовым входим сдвиговых регистров, а вход генератора импульсов является тактовым входомустройства, о т л и ч а ю щ е е о я тем, что, с целью упрощения устрой" ства, оно содержит синхронизатор и блок управления, выход которого подключен к управляющим входам блоков записи-считывания, а вход - к выходу синхронизатора, управляющие входы синхронизатора подключены к соответствующим выходам блока управления, тактовый вход синхронизатора подключен к выходу генератора импульсов, входы блока управления являются входами устройства.

2. Устройство по и. 1, о т л и ч аю щ е е с я тем, что синхронизатор содержит элементы И, элементы

ИЛИ, запоминающие ячейки и группу соединенных последовательно запоми-нающих ячеек, выход последней из которых является выходом синхронизато. ра и подключен к входу первой запоминающей ячейки, а вход первой — к выходу элемента ИЛИ, выход первой запоминающей ячейки подключен к входу первого элемента и к входу второй запоминающей ячейки, выход кото, рой подключен к первому входу второго элемента И и.к входу третьей запоминающей ячейки, выход третьей запоминающей ячейки подключен к первому входу третьего элемента И, тактовые входы запоминающих ячеек и соединенных последовательно запоминающих ячеек группы подключены к тактовому входу синхронизатора, выхо» ды элементов И. подключены к соответствующим входам элемента ИЛИ, вторые входы элементов И являются управляющими входами синхронизатора.

3. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок управления содержит, элементы И, элемент ИЛИ, элемент ИЛИ-НЕ и триггер, выход которого подключен к первым

ВНИИПИ Закаэ 7526/77 Тираж 622 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 входам первого, второго и третьего элементов И, вход триггера подключен к выходу четвертого элемента И, первый вход которого является входом блока управления, второй вход четвертого элемента И подключен к выходу элемента ИЛИ, входы которого подключены к вторым входам соответствующих элементов И и. являются входами блока управления, выходы первого и второго элементов

И являются управляющими выходами блока управления и подключены к со963102 8 ответствующим входам элемента ИЛИНЕ, выход которого является выходом блока управления.

5 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР и 519764, кл. G 11 С 19/00, 1974.

2. "Электроника", 1977, N 21, 1О с. 21-22, 3. Авторское свидетельство СССР

Ю 519761, кл, G 11 С 19/00, 1974 (прототип).