Двухтактный динамический регистр сдвига

Иллюстрации

Показать всеРеферат

(54) ДВУХТАКТНЫЙ ДИНАИИЧЕСКИЙ РЕГИСТР

СДВИГА

Изобретение относится к импуль сной технике и может быть использовано в радиоэлектронных устройствах систем автоматического управления, для построения функциональных узлов вычислительных устройств.

Известен регистр сдвига, содержащий запоминающие конденсаторы, транзисторы и-р-и типа, резисторы, источник положительного постоянного напряжения, диоды, источник импульсов управления, источник тактового питания, источник входного сигнала, транзисторы р-и-р типа, поле вые транзисторы, выходную .нагрузку 03 1>

Одним из основных недостатков данного устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия динамического регистра ?o сдвига.

Поставленная цель достигается тем, что в двухтактный динамический регистр сдвига, содержащий на

2 один разряд два каскада, каждый иэ которых состоит из запоминающего конденсатора, одна обкладка которого соединена с змиттером первого ключевого транзистора и стоком полевого транзистора, исток которого подключен к .шине нулевого потенциала, другая обкладка запоминающего конденсатора подключена к тактовой шине, затвор полевого транзистора соединен с коллектором второго ключевого транзистора, одним из выводов первого резистора и катодом диода, анод диода и другой вывод первого резистора соединены соответственно с шиной управления и шиной постоянного напряжения, база второго ключевого тран" зистора через второй резистор, а змиттер непосредственно соединены с шиной нулевоге. потенциала, база первого ключевого транзистора подключена к шине нулевого потенциала через третий резистор, в каждый каскад регистра введен дополнительный

3 963 полевой транзистор, затвор которого соединен с коллектором второго ключевого транзистора данного каскада, сток — с базой второго ключевого транзистора данного каскада, истокс коллектором первого ключевого тран зистора предыдущего каскада.

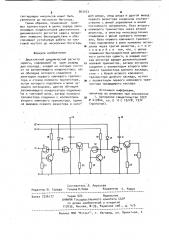

На чертеже приведена принципиальная схема предлагаемого регистра сдвига, Двухтактный динамический регистр сдвига содержит запоминающие конденсаторы 1 и 2, транзисторы 3 и 4 и-р-и типа, полевые транзисторы

5-8 с затвором типа и, транзисторы

9 и 10 р"и-р типа, и источник входного сигнала, источники 12 и

13 тактового питания, источник

14 положительного постоянного напряжения, источник 15 импульсов управления, диоды 16 и 17, резисторы 18

1 и !9, выходнУю нагРУзкУ 20, резисторы 21-24.

Устройство работает следующим образом.

Полевые транзисторы 5 и 6 включены таким образом, что исток через переход коллектор-эмиттер выходного транзистора второго каскада регистра сдвига предыдущего разряда и выходного транзистора первого каскада регистра сдвига данного разряда под ключен к запоминающим конденсаторам, сток - к базам транзисторных ключей, затвор - к коллекторам транзисторов этих же транзисторных ключей.

При поступлении входного сигнала от источника 11 в момент отсутствия тактирующего импульса от источника

12 регенеративное устройство, представляющее совместно включенные полевой транзистор 5 и транзистор 3, открывается. При этом на затворе полеваго транзистора 7 устанавливается низкий потенциал и транзистор 7 открывается. Происходит разряд запоминающего конденсатора 1. Постоян = ная времени цепи разряда составляет несколько микросекунд.

103

1О

g5 ния известного транзистора регистра сдвига, так как время переключения регенеративного устройства составляет несколько наносекунд.

После разряда запоминающего конз0 денсатора 2 и заряда запоминающего конденсатора 1 импульс управления от источника 15 импульсов управления через диод 17 поступает на затвор полевого транзистора 8, повышает положительный потенциал и закрывает его.

При поступлении тактирующего импульса от источника 13 тактового питания происходит процесс заряда запоминающего конденсатора 2. Процесс заряда запоминающего конденсатора 2

40 .такой же, как и конденсатор 1. 8 этом случае на нагрузке 20 выделяется сигнал, который является входным для регистра сдвига последующего разряда.

В предлагаемой схеме быстродей45 ствие регистра сдвига зависит от переходных процессов при заряде и разряде запоминающих конденсаторов и от скорости переключения регенеративного устройства. Так как момент нача-, 50 ла разряда запоминающего конденсатора 2 наступает значительно раньше, чем в известном регистре сдвига, то тактирующий импульс источника 13 тактового питания подается по отношение к моменту поступl ления тактирующего импульса от источника 12 тактового питания значительно раньше. Следовательно, частота (tp = C RohTt где С - емкость конденсатора 1; колт — сопротивление канала открытого полевого транзистора 7.

После разряда запоминающего конденсатора 1 импульс управления от источника импульсов управления через диод 16 поступает на затвор полевого транзистора 7, повышает положительный его потенциал и закрывает его.

При поступлении тактирующего импульса от источника 12 тактового питания происходит заряд запоминающего конденсатора 1 по цепи : переход эмиттер-коллектор транзистора 9, канал полевого транзистора 6, переход база-эмиттер транзистора 4.

При заряде запоминающего конденсатора 1 до определенного уровня открывается транзистор 4 и на затворе полевого транзистора 8 устанавливается низкий потенциал. Полевой транзистор 8 открывается и происходит разряд запоминающего конденсатора 2 через открытый канал полевого транзистора 8. Время начала разряда запоминающего конденсатора 2 зависит от времени срабатывания транзистора 4. Применение полевого транзисто ра 6 позволяет значительно уменьшить время переключения транзистора

4 по сравнению с временем переключе96310 формула изобретения

Соста витель Л. Амусьева

Редактор Ю. Середа Техред М.Надь КорректоР Е. Рошко

Заказ 7526/7?

Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д 4/5

Филиал ППП "П тент", r. Ужгород, ул. Проектная, 4

5 тактирующих импульсов может быть увеличена до несколько Мегагерц..

Таким образом, применение полевых транзисторов в цепях заряда запоминающих конденсаторов двухтактного динамического регистра сдвига позволяет повысить быстродействие и обеспечивает устойчивую работу на тактовой частоте до нескольких Мегагерц. !

Двухтактный динамический регистр сдвига, содержащий на один разряд два каскада, каждый из которых состоит из запоминающего конденсатора, одна обкладка которого соединена с эмиттером первого ключевого транзистора и стоком полевого транзистора, исток которого подключен к шине нулевого потенциала, другая обкладка запоминающего конденсатора подключе1 на к тактовои шине, затвор полевого транзистора соединен с коллектором 2з второго ключевого транзистора, одним из выводов первого резистора и като3 4 дом диода, анод диода и другой вывод первого резистора соединены соответственно с шиной управления и шиной постоянного напряжения, база второго ключевого транзистора через второй резистор, а эмиттер непосредственно соединены с шиной нулевого потенциала, база первого ключевого транзистора подключена к шине нулевого потенциала через третий резистор, о т л ич а ю шийся тем, что, с целью повышения быстродействия динамического регистра сдвига, в каждый каскад регистра введен дополнительный полевой транзистор, затвор которого соединен с коллектором второго ключевого транзистора данного каскада, сток - с базой второго ключевого транзистора данного каскада, истокс коллектором первого ключевого транзистора предыдущего каскада.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ю 417844, кл. 6 11 С 19/28, 1972 (прототип).