Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 96З1О()

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических республик (6! ) Дополнительное к авт. саид-ву (22) Заявлено 06.03.81 (2! ) 3256897/18-24 с присоединением заявки № (23) Приоритет

Ойубликовано 30 0g.82 Бюллетень № 36

Дата опубликования описания 03;10.82 (5i)M. Кл .611 С 27/00

9кудврственьй квиитет

СССР

lO делам взабретеикк и вткрытнй (53) Уд ((68 1.327. .66(088.8) (72) Авторы изобретения

A. Н.Савин, Ф. И. Жуганарь и И. Ф. Клисторин

Кишиневский политехнический институт им. С. азо

---.. (7!) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к измерительной технике и может быть использовано в устройствах обработки аналоговых величин, а также в электрических измерительных преобразователях.

Известно аналоговое запоминающее устройство (АЗУ), содержащее операционный усилитель, ключ, буферный повторитель напряжения, ко входу которого подключен запоминающий конденсатор, а выход через резистор соединен со входом операционного усилителя 1 ) .

Однако в таком устройстве точность хранения информации мала из-за утечки заряда накопительного конденсатора. !

Наиболее близким к предлагаемому является АЗУ, содержащее компаратор, один из входов которого соединен со входом устройства, а другой - с выходом устройства и выходом буферного повторигс теля напряжения, вход которого подключен к одной из обкладок накопительного конденсатора и через ключ к выходу ком2 паратора. Вторая обкладка конденсатора соединена с шиной нулевого потенциала(2).

Низкая точность хранения информации в таком АЗУ обусловлена утечкой заряда с конденсатора через входное сопротивле ние буферного повторителя напряжения, сопротивление замкнутого ключа и сопро тивление утечки самого конденсатора.

Время хранения запоминаемой величины в этом АЗУ редко превышает несколько секунд.

Бель изобретения — повышение точности хранения устройства.

Поставленная дель достигается тем, что в аналоговое запоминающее устройство, содержащее компаратор, первый вход которого является входом устройства, ключ, первый вход которого соединен с выходом компаратора, накопительный элемент, например конденсатор. одна из обкладок которого соединена с шиной нуле» вого потенциала, а другая обкладка конденсатора соединена с выходом ключа и с входом повторителя напряжения, и шину ьи

K„7 (2 макс (5) u„=u „+ u/2, 3 963 10 управления, введены блок цифровой памяти, формирователь и суматор, выход которого является выходом устройства, входы сумматора соединены с выходами повторителя напряжения и блока цифровой памяти, первый вход которого соединен с шиной управления и с входом формирователя, второй вход блока цифровой памяти соединен с первым входом компаратора, второй вход которого подключен к выхо- щ ду сумматора, выход формирователя соединен с вторым входом ключа.

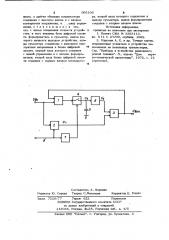

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит компаратор 1, блок 2 цифровой памяти, сумматор 3, ключ

4, накопительный эле мент, например конденсатор 5, повторитель. 6 напряжения, формирователь 7, шину 8 управления, шину 9 нулевого потенциала.

Устройство работает следующим образом, В начальный момент времени ключ 4 разомкнут. При подаче на шину 8 стробируюшего импульса он вызывает вначале 25 сброс, а затем запуск блока 2 цифровой памяти. При этом блок 2 генерирует напряжение ступенчатой формы. Когда уровень очередной ступеньки достигает уровня входного сигнала, блок 2 переходит в режим "Хранение". При этом на выходе блока 2 устанавливается сигнал )ч где nU — величина ступеньки квантова- З ния выходного напряжения блока 2 цифровой памяти.

Величина а U определяется количеством разрядов и блока 2 и динамическим диапазоном входного сигнала и -и

BX.КОКС, BX. NИН. (g)

20. де Ugx ма кс „Ugх мин — соответственно 45 максимальное и минимальное значения входного сигнала.

После перехода блока 2 в режим "Храпение" с выхода формирователя 7 на второй вход ключа поступает импульс, $0 переводящий ключ 4 в замкнутое состояние. При этом замыкается контур отрицательной обратной связи устройства и конденсатор 5 заряжается до тех пор, пока выходное напряжение устройства дости- у гает уровня входного напряжения

08blX=uq..К2+U2 K1 UBX 1(Э) 6 4 где и2 — выходное напряжение повторителя 6 напряжения;

k К вЂ” коэффициенты передачи суммач! 2 тора 3 соответственно по первому и второму входам.

После окончания управляющего импульс са ключ 4 размыкается и устройство переходит в режим "Хранение", При условии, что коэффициент усиления компаратора 1 достаточно большая величина и коэффициенты передачи повторителя 6 напряжения и сумматора 3 по второму входуравны единице, на конденсаторе 5 устанавливается следующее напряжение

Э К 2К ч ч

При этом величина Кч определяется величиной а U и максимально допустимым выходным напряжением повторителя 6 напряжения +01 м, с

Например, при 08хмакс.= 5 В:

Usx мин.= 5 В И= В -U2 макс =+10 на основании формулы (2) AU =39,06 мВ, а на основании формулы (5) К < ) 1, 95 х х10, что намного меньше единицы.

Благодаря тому, что коэффициенты передачи сумматора 3 по первому и второму входам выбираются так, чтобы К„<< 1, а

К = 1, из формулы (3) следует, что основная доля выходного напряжения устройства хранится с высокой точностью в блоке 2 цифровой памяти, определяемой высокой стабильностью ее элементов, и как следствие из этого - влияние утечки заряда конденсатора 5 на точность хранения информации устройства уменьшается в 0 Х/< U раз.

Смешение нуля повторителя 6 напряжения и сумматора 3 не влияют на точность работы устройства, так как они включены в контуре отрицательной обратной связи компаратора 1, имеющего боль» шой коэффициент усиления.

Формула изобретения

Аналоговое запоминающее устройство, содержащее компаратор, первый вход которого является входом устройства, ключ, первый вход которого соединен с выходом компаратора, накопительный элемент, например конденсатор, одна из обкладок ко« торого соединена с шиной нулевого потен5 963106 6 циала, а другая обкладка конденсатора ра, второй вход которого подключен к соединена с выходом ключа и с входом .выходу сумматора, выход формирователя повторителя напряжения, и . шину управ- соединен с вторым входом ключа.

1 ления, о т л и ч а ю ш е е с я тем, Источники информации, что, с целью повышения точности устрой- 5 принятые во внимание при экспертизе ства, в него введены блок цифровой памя- 1. Патент США % 3363113, ти, формирователь и сумматор, выход ко- кл. 6 11 С 27/00, опублик. 1968. торого является выходом устройства, вхо- 2. Мурсаев А. Х. и др. Точные ключи, ды сумматора соединены с выходами пов- операционные усилители и устройства заторителя напряжения и блока цифровой 10 поминания на канальных транзисторах. памяти, первый вход которого соединен Сер. "Приборы и устройства радиоэлект с шиной управления и с входом формиро- ронной техники . Л., изд-во "Дом научвателя, второй вход блока цифровой памя- но-технической пропаганды, 1972, с. 21 ти соединен с первым входом компарато- (прототип).

Составитель А. Воронин

Редактор Ю. Середа Техред С.Мигунова Корректор E. Рошко

Заказ 7526/77 Тираж 622 П одписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35; Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4