Способ цифрового измерения временных интервалов и устройство для его реализации

Иллюстрации

Показать всеРеферат

Союз Соввтсиик

Социалистически к

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К . АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 964569 (61) Дополнительное к авт. свив-ву (22) Заявлено . 06. 04. 77(21) 2472704/18-10 с присоединением заявки М (23) Приоритет (51)М. Кл.

G 04 F 10/04

Веуаеретаапв4 кемятат,СССР аю делам наебретакяй я етарытий

Опубликовано 07. 10 . 82 . Бктллетень,яа 37 (53) УЙ3(681.11 (088.8) Дата опубликования описания 09.10.82 юг я О,., tl4 TEfj сей хци щцц g икиБИБлиоli„4 (72) Авторы изобретения

В.Я. Загурский и Г.И. Готлиб

Институт электроники и вычислительной те

АН Латвийской ССР (71) Заявитель. (54) СПОСОБ ЦИФРОВОГО ИЗМЕРЕНИЯ ВРЕМЕННЫХ

ИНТЕРВАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО

РЕАЛИЗАЦИИ

Изобретение относится к измерительной технике, в частности к измерению временных интервалов.

Известны способы цифрового измерения временных интервалов (1)..

Наиболее близким техническим решением является способ измерения временных интервалов и устройство для

его реализации, включающий формирование двух сдвинутых по времени импульсных последовательностей,определения опережающей и отстающей по отношению к на алу измеряемого интервала импульсных последовательностей, заполнение импульсами опережающей последовательности измеряемого интервала и просчет этих импульсов.

Устройс во,- реализующее этот способ, содержит формирователь сдвинутых импульсных последовательностей, блок памяти, блок сравнения и счетчик (2).

Однако известный, способ обладает невысокой точностью измерения из-за

-2 невозможности определить конечный участок измеряемого интервала с точностью большей, чем разрешающая способность импульсной последовательности.

Целью изобретения является точность измерения.

Указанная цель достигается тем, е что согласно способу, включающему формирование импульсной последовательности, заполнение импульсами этой последовательности измеряемого интервала и просчет этих импульсов, вводят ся операции фиксации состояния импульс ной последовательности в момент начала измеряемого интервала, сравнения зафиксированного состояния с каждым. из

20 двух состояний этой последовательности в течение измеряемого интервала, подсчета числа этих совпадений, фиксации его как целой части длительнос; ти измеряемой вел чины, фиксации ре3 „9645 зультата сравнения в момент окончания измеряемого интервала как результата измерения дробной части измеряе мой вели чи ны.

В устройство, реализующее способ, содержащее формирователь импульсной последовательности, сборку схем ИЛИ, блок памяти, блок сравнения и счетчик, введены дешифратор и двухфазный счетчик, при этом формирователь им- >в пульсной последовательности соединен с входами блока памяти и блока сравнения, выход блока памяти соединен с вторым входом блека сравнения, выходы которого соединены с входами сборки схем ИЛИ, входы двухфазного счетчика соединены с выходами сборки схем ИЛИ, а эыходы .соединены с входами дешифратора, вход счетчика соединен с одним выходом двухфазного 2О счетчика, а второй вход блока памяти и третий вход сборки схем ИЛИ являются входом устройства для измеряемого интервала.

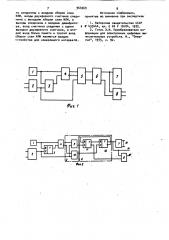

На фиг. 1 представлена Функциональ- ная схема измерителя временных интервалов в код; на фиг. 2 - принципиальная схема измерителя временных интервалов; на фиг. 3 - диаграммы, поясняющие работу устройства.

Устройство содержит формирЬватель 1 импульсной последовательности, источник 2 временного интервала, блок 3 памяти, блок 4 сравнения, сборку схем ИЛИ 5, двухфазный счетчик 6, счетчик 7, дешифратор 8.

На схеме (фиг. 2) представлены

О-триггер, выполняющий функции блока 3 памяти, схема равнозначности, выполняющая функции блока 4 сравнения,пер-. вая 9 и вторая 10 схемы ИЛИ, составляющие сборку схем ИЛИ 5, первый 11 и второй 12 О-триггеры, образующие двухфазный счетчик 6, кодовые выходы счетчика 13, выход 14 триггера 12, являющийся выходом второго разряда измерителя, вторая схема равнозначности, выполняющая функции дешифратора 8.

Измеритель временных интервалов работает следующим образом.

so

В исходном состоянии на выходе триггера. 3 повторяются сигналы Формирователя 1, присутствующие на О-входе этого триггера. Поскольку сигналы на входах блока сравнения 4 равно- H значны (синфаэны), то на прямом выходе этой схемы имеется логическая 1", а на инверсном - логический "0". Триггеры 11 и 12, а также счетчик 7 пред« варительно установлены в состояние логического "0" соответствующим сиг" налом (цепи установки "нуля" не изображены 7.

Рассмотрим рабсгу измерителя в том случае, когда временной интервал начинается при логическом "0" на выходе формирователя 1 (момент 15, группа диаграмм А).

После прихода логического "0" на

О-вход триггера 3 íà его выходе оста" ется логический "0" в течение временного интервала. Следовательно, сигналы на выходе формирователя 1 и выходе блока сравнения 4 взаимно инверсны, а на выходе формирователя 1 и инверсном выходе блока сравнения 4 " синфазны. В момент 1б на выходе схемы 10 появляется положительный фронт, однако изменения состояния тригreров 11 и 12 не происходит, поскольку на О-входе, и выходе 14 триггера 12 сигналы синфазны. В момент 17 на выходе схемы ИЛИ 9 появляется положитель ный фронт, что приводит к появлению логической "1" на выходе триггера 11.

В момент 18 появляется положительный фронт на выходе схемы ИЛИ 1О, что приводит к появлению логической "1" на прямом, и логического "0" на инверсном выходе триггера 12. В момент 19 изменяется состояние на пря". мом выходе триггера 11 и т.д. Описанные для моментов 17-19 процессы повторяются до окончания временного интервала в момент 20. Поскольку в этот момент на О-входе триггеров 11 и 12 появляется положительный фронт, на Р-входе триггера 12 - логический

"0", а на выходе !4 - логическая "1", то на выходе 14 состояние меняется а логический "0". В момент времени 21 на выходе триггера 3 появляетcR сигнал, синфазный сигналу формирователя 1, на прямом выходе блока сравнения 4 остается логическая ."1", а на инверсном - логический "0", поскольку сигналы на ее входах теперь синфаэны. Счет окончен. Для случая А длительность временного интервала превышает 7, но меньше 9-ти целых полупериодов частоты формирователя

Код преобразованного временного интервала составляет: на выходе дешифратора 8, являющимся выходом младшего разряда (2 ) - логический "0"

{сигналы на входах противофазны), на выходе 14 (,второй разряд, 2") 569

S 964 логический "0". В счетчик 7 поступает два сигнала переноса (сигналом переноса считается отрицательный фронт на выходе 14), так что в третьем и четвертом разрядах (на выходах 13) преобразователя код соответственно

01. Код временного интервала составляет 1000 (от старшего разряда к младшему), т.е. 8 полупериодов. Ошибка преобразования не превышает + Т/2.

Группа временных диаграмм Б иллюстрирует работу измерителя в случае начала временноro интервала при логической. "1" на выходе формирователя 1.

В этом случае в течение временного интервала на выходе триггера 3 - логическая "1". Работа младших разрядов счетчика происходит аналогично описанной для случая А, Код преобразованного временного интервала преж- 3В

I нии — 8 полупериодов, ошибка не превышает + Т/2.

Группы -временных диаграмм В-Д иллюстрируют поведение измерителя в случае окончания временного интервала 35 при других кодах на прямых выходах триггеров 11. и 12. В случае В перед окончанием временного интервала на прямом выходе триггера 11 и на 14 логические "0". После окончания, íà 30

Ыыхоре триггера 11 появляется логическая 1", поскольку перед положительным фронтом на D-входе этого триггера 11 был логический "0". Длительность временного интервала превыша35 ет 8, но меньше 10-ти целых полупериодов частоты формирователя 1, Код на выходе измерителя составляет 1001, т.е. 9 полупериодов. Ошйбка не превышает +Т/2. о

В случае Г перед окончанием временного интервала на прямом выходе триггера 11 - логическая " i", на

14 - логический "0". После окончания на прямом выходе триггера 11 оста-45 ется логическая "1", а на 14 появляется логическая 1". Длительность временного интервала превышает 9, но меньше 11-ти целых полупериодов. Код на выходе преобразователя 1010 (от старшего к младшему j, т.е. 10 полу50 периодов. Ошибка не превышает + Т/2.

В случае Д перед окончанием временного интервала на прямом выходе триггера 11 и на выходе 14 - логическая "l". После окончания на выходе 14 остается логическая "1", а на прямом выходе триггера 11 появляется логический "0". Длительность временного ин- .

1 тервала превышает 10, но меньше 12-ти целых полупериодов. Код на выходе измерителя 1011, т.е. 11 полупериодов..

Ошибка не превышает i T/2.

Группы диаграмм В-Д иллюстрирует четыре возможные ситуации на прямых выходах триггеров 11 и 12 перед окончанием временного интервала. Эти и только эти ситуации при окончании временного интервала возможны и в случае начала временного интервала при логическом "0" на выходе формирователя 1, что для одной ситуации проиллюстрировано группой диаграмм А.

Следовательно, измеритель времен" ных интервалов (фиг. 2) реализующий данный способ цифрового измерения вре менных интервалов, обеспечивает циф-. ровое измерение интервалов е дискретностью, равной половине периода частоты формирователя импульсной после" довательности. формула изобретения

1. Способ цифрового измерения временных интервалов, включающий формирование импульсной последовательности, заполнение импульсами этой последовательности измеряемого интервала и просчет этих импульсов, о т л и ч а юшийся тем, что, с целью повышения точности .измерения, фиксируют состояние импульсной последовательности в момент начала измеряемого интервала, сравнивают Зафиксированное состояние с каждым иэ двух состояний этой последовательности в течение измеряемого интервала, подсчитывают число этих совпадений и принимают его за целую часть длительности измеряемой величины, а результат сравнения в момент окончания измеряемого интервала фиксируют как результат измерения дробной части длительности временного интервала.

2. Устройство для реализации способа по и. 1; содержащее формирователь импульсной последовательности, сборку схем ИЛИ, блок памяти, блок сравнения и счетчик, о т л и ч а ющ е е с. я . тем, что в него введены дешифратор и двухфазний счетчик, при этом формирователь импульсной последовательности соединен с входами . блока памяти и блока сравнения, выход блока памяти соединен с вторым входом блока сравнения, выходы которо964569

7 го соединены с входами сборки схем .ИЛИ, входы двухфазного счетчика соеди.нены с выходами сборки схем ИЛИ, а выходы соединены,с входами дешифратора, вход счетчика соединен с одним 3 выходом двухфазного счетчика, а второй вход блока памяти и третий вход сборки схем ИЛИ являются входом стройства для измеряемого интервала.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

И 433444, кл. G 04 F 10/04, 1972.

2. Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. M. "Энергия", 1975, с. 92.

Заказ 7626/26

Тираж 427 Подписное

ВНИИПИ

Филиал flflfl "Патент", r. Ужгород, ул. Проектная, 4

Ф

1Ф

11

964569

Фмк Ю