Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Союз Советсник

Социапистичеснии рес убпик

О П И С А Н И Е „„ЕЕ4ВаО

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6I ) Дополнительное к авт. свид-ву (51)М. Кл.

Cj 06 1 9/22 (22) Заявлено 08.01.81 (2l ) 3260121/18-24 с и рисоединениеи заявки .йв (23) Приоритет

9вуаарстванвй кеюетет

CCCP ао дввви взввретвеФ и опрытий

Опубликовано 07.10.82. Бюллетень Фв 37 (53) УДК 681. .325(088.8) Дата опубликования описання07.10.82 (72) Авторы изобретения

Б. Г. Балакирев, Г. Н. Вейс, И. В. Волков и (71) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ в 1

Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении управляющих автоматов.

Известно микропрограммное устройство

5 управления, содержащее запоминающее устройство, регистр мнкрокоманд, счетчик микрокоманд и блок проверки условий перехода, состоящий из дешифратора, группы элементов И и элемента ИЛИ f1) Ip

Недостатком этого устройства является низкое быстродействие, прскольку длительность автоматного такта увеличивается на время выполнения операпии счета в двоичном счетчике. I5

Наиболее близким к изобретению техническим решением является микропрограммное устройство управления, содержащее блок запоминания микрокоманд, регистр микрокоманд, блок запоминания . эквивалентных адресов, накапливакцций сумматор и блок управления (2 .

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее два блока памяти, регистр и блок проверки условий, причем первый выход регистра соединен, с информационным входом блока проверки условий, второй выход регистра является информационным выходом устройства, группа информационных входов блока проверки условий является группой входов условий устройства, введен коммутатор, причем первый и.второй информационные входы коммутатора соединены соответст» венно с выходами первого и второго блоков памяти, входы которых соединены с третьим выходом . регистра, первый и второй разрешакзцие входы коммутатора соединены соответственно с первым и вторым выходами блока проверки условий, выход коммутатора соединен с информационным входом регистра.

Блок проверки условий содержит де шифратор, группу элементов И, элемент ИЛИ и. элемент НЕ, причем каждый 1 -й

9646

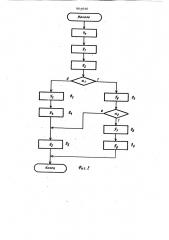

При выполнении микропрограммы (граф-схема на фиг. 2) в исходном состоянии регистр микрокоманд 5 обнулен

40 и с его поля 6 на вход блока 1 и блока

2 поступает адрес ячейки В . После прихода пускового сигнала блок 4 вырабатывает управляющий сигнал на считывание информации из ячейки В блока 1. Происходит это следующим образом. Поскольку

IIonei осведомительных сигналов 7 обнулено, то на вход дешифратора 9 поступают уровни логического О, и все его выходы (кроме нулевого, который не используется) находятся в состоянии логическо- 5О го О . С выходов дешифратора нулевые сигналы поступают на первые входы соотaeTcTsyxanHx элементов И 10 и запирают их, запрещая щжем информации с входов

13. Выходы всех элементов И 10 находятся в состоянии логического О", что приводит к тому, что выход элемента

ИЛИ 11 также находится в состоянии

3 вход группы входов блока соединен с первым входом -го элемента И группы, второй вход которого. соединен с

И -м выходом дешифратора, выход каждого элемента И группы соединен с соот-, 5 ветству1ошим входом элемента ИЛИ, выход которого соединен с первым выходом блока н через элемент НŠ— со вторым выходом блока, вход дешифратора соединен с входом блока. о

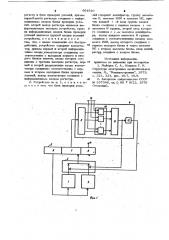

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - граф-схема выполнения программы; на фиг. 3 и 4 принцип размещения микропрограмм в блоках памяти.

Микропрограммное устройство управления (фиг. 1) содержит блок 1 памяти, блок 2 памяти, коммутатор 3, блок 4 проверки условий, регистр 5, поле 6 адресов регистра 5, поле 7 осведомитель- рц ных сигналов регистра 5, поле 8 микрокоманд регистра 5, дешифратор 9 блока

4, группа элементов И 10 блока 4, элемент ИЛИ 11 блока 4, элемент НЕ 12 блока 4, группа входов 13 условий устройства, информационный выход 14 устройства.

Устройство работает следующим образом. Ha вход дешифратора 9 с выхода поля осведомительных сигналов 7 регистра

5 поступает код номера осведомительного сигнала, значение которого анализируется в данной микрокоманде. Сам осведомительный сигнал поступает на. соот35 ветствующий вход грунцы входов 13.

40 4 логического "0", а выход элемента

НЕ 12 находится в состоянии логической

lF If

1 . Нулевой сигнал с выхода элемента

ИЛИ 11 поступает на первый управляющий вход коммутатора 3 и запирает цепь приема информации из блока 2, одновременно с.выхода элемента НЕ 12 единичный сигнал поступает на второй управляющий вход коммутатора 3 и открывает цепь приема информации из блока 1.

Размещение микропрограммы в блоке 1 и в блоке 2 показано на фиг. 3 и 4 соответственно.

После микрокоманды Ус, хранящейся в ячейке В блока 1, выполняется микрокоманда У, затем У2. При этом блок 4 ° вырабатывает сигналы на считывание информации из блока 1, так как команды

Уо и У в поле осведомительных сигналов содержат нулевые сигналы, что приводит к появлению на выходе элемента

HE 12 сигнала логической "1", который управляет считыванием информации из блока 1. При выполнении микрокоманды

У происходит следующее. Код номера осведомительного сигнала 0! g (см. содержимое ячейки В блока 1 на фиг. 3) поступает на вход дешифратора 9, при этом соответствующий выход дешифратора 9 переходит в состояние логической

1 ". Сигнал (X g поступает на соответст вующий вход 13. Если значение сигнала g,< = О, то состояние управляющих входов коммутатора 3 не изменяется и очередная микрокомацда считывается IIo адресу В из блока 1. На выходе поля 8 регистра 5 .(на выходе устройства) появляется микрокоманда У .

Если значение сигнала сС = 1, то на обоих входах соответствующего элемента

И 10 появляются единичные сигналы, что пвивоцит к появлению сигнала логической 1 на выходе элемента ИЛИ 11,: а на выходе элемента НЕ 12 устанавливается значение логического ."О

Нулевой сигнал с выхода элемента

HE 12 поступает на коммутатор 3 и запирает цепь приема информации из блока

1. Единичный сигнал поступает с выхода элемента ИЛИ 11 на коммутатор 3 и открывает цепь приема информации из блока 2. В блоке 2 в ячейке Вч хранится микрокоманда У, которая и появляется на выходе 14 устройства.

Применение изобретения позволяет повькжгь быстродействие устройства.

Формула изобр ет ения

1. Микропрограммное устройство управления, содержащее два блока памяти, 5 9646 регистр и блок проверки условий, причем первый выход регистра соединен с информационным входом блока проверки условий, второй выход регистра является информационным выходом устройства, груп- S па информационных входов блока проверки усповий является группой входов условий устройства, о т л и.ч а ю ш е е с я тем, что,. с целью повышения его быстродействия, устройство содержит коммута о тор, причем первый и второй информационные входы коммутатора соединены соответственно с выходами первого и второго блоков памяти, входы которых соединены с третьим выходом регистра, пер- 15 вый и второй разрешакацие входы коммутатора соединены соответственно с первым и вторым выходами блока проверки условий, выход коммутатора соединен с. информационным входом регистра. . 20

2. Устройство по.п. 1, о т л и ч а юш е е с я тем, что блок проверки усло40 6 вйй содержит дешифратор, группу элемен тов И, элемент ИЛИ и элемент НЕ, причем каждый (-Й вход группы входов блока соединен с первым входом j -ro элемента И группы, второй вход которого соединен с . -м выходом дешифратора, выход каждого элемента И группы соединен с соответствующим входом элемента ИЛИ, выход которого соединен с первым выходом блока и через элемент

НЕ с вторым выходом блока, вход дешифратора соединен с входом блока.

Источники информации, принятые во внимание при экспертизе

1. Майоров С. А, Новиков Г. Н.

Структура электронных вычислительных машин. Л., "Машиностроение", 1979, с. 321, 324, рис. 10.7, 10.9.

2. Авторское свидетельство СССР

И 537346, кл. g 06 F 9/22, 1976 (сотип).

964640

Поле осоедома тель- Члраб яющ ал нь!м сигнамоо жесть

Андрес н юейки ЯУ

Ядреонам часлгь

Фиг.Я .

Составитель М. Кудряшев

Редактор Л. Гратилло Техред М. Рейвес Корректор Г. Огар

Заказ 7631/29 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4