Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

964733

«вт, ",! !!, i в

7Ф »

« (61) Дополнительное к авт. свид-ву(22) Заявлено 11. 03. 81(21) 3259282/18-24 с присоединением заявки №вЂ” (23) ПриоритетОпубликовано 07.10.82 ° Бюллетень ¹ 37

Дата опубликования описания 071082 (31) М. Кл.з

G 11 С 11/00

Государственный комитет

СССР но делам изобретений и открытий

f 53) УДК 681. 327 (088. 8) ВСЕСОЮЗНАЯ

ПАТЕНТНО.

ТЕХНИЧЕСКАЯ

ЫБЛИОТЫ-. i!

A. Ю. Веревкин, Г. Н. Булкин, В.. Н. Петрун

В. П. Лачугин и Ю. С. Мануйлов (72) Авторы изобретения (71) Заявитель (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запомина: ющим устройствам.

Известно запоминающее устройство, которое содержит регистры памяти, логические схемы по числу регистров памяти, триггеры по числу регистров памяти.и элементы И (1).

Недостатком этого устройства являются большие аппаратурные затраты..

Наиболее близким техническим решением к изобретению является буферное запоминающее устройство, содержащее накопитель на регистрах памяти и логические схемы по числу регистров памяти Г2)

Недостатком этого устройства является его сложность, вследствие чего снижается его надежность.

Цель изобретения — повыаенив надежности устройства..

Поставленная цель достигается тем, что в буферное запоминающее, устройство, содержащее накопитель, одни из входов и выходы которого-являются информационными входами и выходами устройства, введены блок управления режимами работы и адресный блок, входы и первый выход которого

l соединены с другими входами накопителя, второй, третий и четвертый. выходы адресного блока подключены соответственно к первому, второму и третьему входам блока управления режимами, выходы которого и входы адресного блока являются соответственно управляющими выходами и входами устройства.

Адресный блок содержит дешифратор счетчики, элементы И, элементы задержки и элемент ИЛИ, выход которого соединен с входом дешифратора, а вхо-. ды подключены соответственно к выходам первого и второго элементов И, первые входы которых соединены с входами первого и второго элементов задержки соответственно, выходы которых подключены соответственно к входам первого и второго счетчиков, выход первого счетчика соединен с вторым входом первого элемента И и первым входом третьего элемента И, второй вход которого подключен к выходу второго счетчика и второму входу второго элемента И, выходы дешифратора и третьего элемента И, выходы и входы первого и второго элементов задержки являются соответственно выходами с первого по четвертый и входами блока.

9б 4731

Кроме того, блок управления режимами работы содержит триггеры, четвертый и пятый элементы И, причем прямой ныхрд первого триггера подключен к первым входам четвертого элемента И и второго триггера, второй вход которого соединен с выходом пятого элемента И, первый вход которого подключен к инверсному выходу первого триггера и. первому входу третьего триггера, второй вход которого соединен с выходом четнертого элемента И, вторые входы четвертого и пятого элементов И объединены и являются первыми входами блока, вторым и третьим входами и ныходами которого 15 являются первый и второй входы первого триггера и ныходы второго и третьего триггеров.

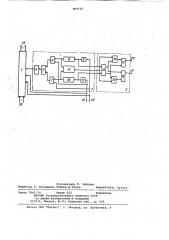

На чертеже изображены функциональные схемы предложенного устройства, 2О адресного блока и блока управления режимами работы.

Устройство содержит накопитель 1 на регистрах памяти (не показаны), .адресный блок 2 и блок 3. управления режимами работы. Адресный блок содержит дешифратор 4, элемент ИЛИ 5, перный б и второй 7 элементы И, первый счетчик 8, предназначенный для формирования дцреса чтения, первый элемент 9 задержки, второй счетчик

10, предназначенный для формирования адреса записи, второй элемент 11 задержки и третий элемент И 12. Блок управления режимами работы содержит перный триггер 13, четвертый 14 и .пятый 15 элементы И, второй 16 и третий 17 триггеры. На чертеже обозначены информационные 18 и управляющие 19 и 20 вхоцы устройства, упранляющие 21 и 22 и информационные 23 выходы устройства. . Предложенное устройство работает следующим образом.

Адреснйй блок 2 вырабатывает адрес, в соответствии с которым происходит запись или чтение данных из накопителя 1. Блок 3 служит для индикации состояния накопителя 1 (полностью свободен, частично занят или полностью занят), в соответствии с которым организуется работа устройства. В исходном состоянии все регистры накопителя 1 свободны. Триггер 13 находится н единичном состоянии и сигнал с его прямого выхода устанавливает триггер 16 н единичное состояние, на выходе 21 устройства появляется единичный сигнал,, что соответствует разрешению записи. Содержимое счетчиков 10 и 8 равно нулю. 6О

Элемент И 12 вырабатывает сигнал совпадения, который через элемент И 14 устанавливает триггер 17 в нулевое состояние, при этом на выходе 22 устройства появляется нулевой сигнал, что соответствует запрету чтения.

Таким образом, в исходном состоянии разрешена только запись данных в накопитель 1 °

При подаче управляющего сигнала записи на вход 19 устройства он поступает в накопитель 1, информация с входов 18 устройства подается в накопитель 1. Этот же управляющий сигнал записи открывает элемент И 7, и так. как содержимое счетчика 10 равно нулю, то нулевой код адреса записи через элемент ИЛИ 5 поступает на вход дешифратора 4, сигнал с нулевого выхода которого организует запись слова данных в нулевой регистр накопителя 1.

Задержанный управляющий сигнал записи с выхода элемента 11 задержки унеличинает содержимое счетчика 10 на единицу, т.е, формируется следующий адрес для записи данных.. Этим же задержанным сигналом устанавливается в нулевое состояние триггер 13, сигнал с инверсного выхода которого устанавливает в единичное состояние триггер 17, снимая запрет чтения.

Таким образом, чтение данных из накопителя 1 возможно только в том случае, если происходит запись в него хотя бы одного слова.

Работа устройства при чтении данных аналогична рассмотренной выше за исключением того, что триггер 13 в этом случае устанавливается в единичное состояние и снимает сигнал запрета записи, если он установлен.

Информация.при этом считывается с выходов 23.устройства.

В устройстве вырабатываются сигналы запрета записи данных в полностью занятый накопитель 1, а также запрета чтения данных из пустого накопителя 1. В таких случаях содержимое счетчиков 10 и 8 равно между собой, что приводит к срабатыванию элемента И 12, сигнал с выхода которого через элементы И 14 или 15 приводит к установке н нулевое состояние триггеров 16 или 17, что соответствует сигналам запрета записи или чтения.

Например, происходит запись данных в накопитель 1 до полного его заполнения, причем чтение данных не производится. В этом случае после записи последнего слова данных в накопитель 1 сигнал, задержанный элементом

11 задержки, вызывает переполненйе (обнуление) счетчика 10, а так как содержимое счетчика 8 также равно нулю, то срабатывает элемент И 12, сигнал с выхода которого через элемент И 15- устанавливает в нулевое состояние триггер 16, тем самым вырабатывая сигнал запрета записи данных н накопитель 1.

964731

Аналогичным образом происходит выработка запрета чтения данных из пустого. накопителя 1.

Таким образом, в устройстве определяется степень занятости накопителя 1 (полностью свободен - разрешена только запись, частично содержит данные - разрешены и чтение и запись, полностью занят - разрешено только чтение), о чем сообщается абонентам, что расширяет область применения устройства и повышает надежность работы устройства„

ДОЛЯ @ппаратурных затрат, приходя . щаяся на выполнение адресного блока

2 и блока 3 управления режимами рабо- t5 ты, значительно снижается при увеличении емкости накопителя 1, за счет чего также повышается надежность устройства., Технико-экономическое преимущест- 7п во предложейного, устройства заключается в его более высокой надежности по сравнению с известным.

Формула изобретения

1. Буферное запоминающее устройство, содержащее накопитель, один иэ ВХОДОВ и ВЫХОДОВ КоторогО ЯВЛЯЮТ 3р ся информационными входами и выходами устройства, о т л и ч а ю щ е ес я тем, что, с целью повышения надежности устройства, оно содержит блок управления режимами работы и, адресный блок, входы и первый выход которого соедйнены с другими входами накопителя, второй, третий и четвертый выходы адресного блока подключены соответственно к первому, второму и третьему входам блока управления 4О режимами работы, выходы которого и вкоды адресного блока Явля отся соответственно управляющими выходами и входами устройства.

2. Устройство по и.. 1, о т л и- 45 ч а ю щ е е с я тем, что адресный блок содержит дешифратор, счетчики, элементы И> элементы задержки и элемент ИЛИ выкод которого соединен с входом дешифоатооа а входы подключены соответственно к выходам первого и второго элементов И, первые входы которых соединены с входами первого и второго элементов задерж ки соответственно, выходы последних подключены соответственно к входам первого и второго счетчиков, выход первого счетчика соединен с вторым входом первого элемента И и первым входом третьего элемента И, второй вход которого подключен к выходу второго счетчика и второму входу вто. рого элемента И, выходы дешифратора и третьего элемента И, выходы и входы первого и второго элементов. задержки являются соответственно выходами с первого по четвертый и входами блока °

3. Устройство по пп. 1 и 2, о тл и ч а ю щ е е с я тем, что блок управления режимами работы содержит триггеры, четвертый и пятый элементы И, причем прямой выход первого триггера подключен к первым входам четвертого элемента И и второго триггера, второй вход которого соединен с выходом пятого элемента И, ïåðвый вход последнего подключен к инверсному выходу первого триггера и первому входу третьего триггера, второй вход которого соединен с выходом четвертого элемента И, вторые входы четвертого и пятого элементов И объединены и являются первым входом блока, вторым и третьим входами и выходами которого являются первый и второй входы первого триггера и выходы второго и третьего триггеров.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании

Р 2009984, кл., G С 5/06, опублик.

1979.

2. Патент Великобритании

9 2009983, кл. G 4 С 5/06,.опублик.

1979 (прототип).

964731

2Л

Составитель T. Зайцева

Редактор Т. Кугрышева Техред M.Tenep. Корректор В, Ьутяга

Заказ 7641/34 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.: 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4