Устройство для управления реверсивным выпрямителем

Иллюстрации

Показать всеРеферат

С. Г. Обухов, E. Е. Чаплыгин и Г. А. Б (72) Авторы изобретения

ЮСТАС®ЮЗйА Я

ПАТЕНТНОГЕХНИЧЕГЫМ

ЬИЙЛИОТЩД

Московский ордена Ленина энергетический инс (7l ) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕВЕРСИВНЫМ ВЫПРЯМИТЕЛЕМ

Изобретение относится к электротехнике и предназначено для управления реверсивным выпрямителем, состоящим из параметрического источника тока и двух встречно-параллельно включенных вентильных комплектов.

Известно устройство управления, содержащее датчики выходных токов параметрического источника, обеспечивающее непрерывное проте/ канне фаэных токов источника через нагрузку либо через короткоэамкнутый внутренний кон р: (1) °

К недостаткам устройства относится наличие датчиков выходных токов параметрического источника. Их введение усложняет силовую схему, снижает надежность, усложняет осуществление пуска вентильного преобразователя.

Наиболее близким по технической сущности к изобретению является устройство для управления реверсивными вентильными преобразователями, построенное по многоканальной схеме и содержащее 2m каналов, каждый из которых состоит из последовательно включенных компаратора, конъюнктора и выходного формирователя (2).

Однако подобное устройство предназначено для управления вентильным преобразователем, питающимся от источника напряжения, что сужает его функциональные возможности.

Целью изобретения является расширение функциональных возможностей устройства.

Поставленная цель достигается тем, что. устройство для управления реверсивным выпрямителем, состоящим из двух m-фазных мостов и параметрического источника тока, 1О содержащее два блока, каждый иэ которых. состоит из 2m узлов, включающих последовательно соединенные компаратор, конъюнктор и выходной формирователь, введены m датчиков анодных напряжений, датчик выход15 ного напряжения, m вычитателей, два источника постоянного напряжения, два диэъюнктора, два О-триггера, задатчик полярности тока с выходом Ч, эадатчик нулевой паузы с выходом Z и два логических узла, реализующие функции (V+2) и (V+Z) ппичем прямые входы одних m компараторов первого блока и инверсные входы одних tn компараторов второго блока связаны с соответ964960

2S

3 ствующими датчиками анодных напряжений, а те же входы второй половины компараторов связаны с соответствующими датчиками анодных напряжений через вычитатели, вторые входы которых связаны с датчиком вы- S ходного напряжения, инверсные входы компараторов первого блока связаны с первым источником постоянного напряжения, а прямые входы компараторов второго блока— с вторым источником постоянного напряжения. 111

Выходы всех компараторов каждого блока связаны с входами соответствующего дизъюнктора, выходы каждого дизъюнктора присоединены к тактовому входу соответствующего 0-триггера; выходы которых связаны 15 с вторыми входами всех конъюнкторов соответствующих блоков. Задатчик полярности тока и задатчик нулевой паузы связаны с

0-входами триггеров через логические узлы.

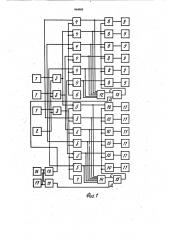

На фиг. I приведена, структурная схема р11 устройства; на фиг. 2 — схема силовой части.

Для определенности фазность принята m = 3.

Датчики анодных напряжений 1 и датчик выходного напряжения 2 присоединены к вычитателям 3, выходы которых связаны с половиной компараторов первого блока 4 и с половиной компараторов второго блока.

5, входы другой половины компараторовсвязаны с датчиками анодных напряжений 1.

Вторые входы всех компараторов 4 связаны с первым источником постоянного напряжения 6, вторые входы компараторов 5 со вторым источником постоянного напряжения

7, К выходам компараторов первого блока через конъюнкторы 8 подключены выходные формирователи 9. К выходам компараторов второго блока через конъюнкторы 10 подключены выходные формирователи 11. Выходы компараторов первого блока 4 связаны через дизъюнктор 12 с С-входом 0-триггера 13, а выходы компараторов второго блока 5 связаны через диэъюнктор 14 с С-входом D-триг- . гера 15, выходы обоих триггеров связаны с конъюнкторами обоих блоков. Задатчик полярности тока 16 и задатчик нулевой паузы 17 через логические узлы 18 и 19 связаны с

0-входами триггеров 13 и 15. Схема силовой части устройства (фиг. 2) включает параметрический m-фазный источник тока 20 и два вентильных моста: первый (вентили 21 — 26) и второй (вентили 27 — 32), работающие на нагрузку 33.

Устройство работает следующим образом.

При положительной полярности тока Ч= 1 и отсутствии нулевой паузы 2 = 0 должны в S» циклическом порядке включаться вентили

21 — 26, между включениями вентилей не должно быть пауз, т.е. вентили включаются сразу при появлении положительного напряжения на их анодах, Напряжение на вентилях 21 — 23 фиксируется датчиками анодных напряжений

1, анодные, напряжения на вентилях 24 — 26 определяются как разность выходного напряжения (сигнал датчика 2) и сигнала датчиков 1, разность определяется вычитателями 3.

Таким образом на компараторы 4 и 5 поступает сигнал, соответствующий величине анодного напряжения соответствующего вентиля.

Если этот сигнал превышает некоторое напряжение задаваемой источником постоянного напряжения 6 (для второго комплекта вентилей 7), то компараторы срабатывают и через конъюнкторы 8 (для второго комплекта 10) передают управляющий импульс на выходные формирователи 9 (для второго комплекта 11). При Ч = 1, Z = 0 единичный сигнал только на выходе D-триггера 13, на выходе D-триггера 14 нулевой сигнал, конъюнкторы 10 заперты и на выходные, формирователи 11 управляющие импульсы не поступают.

При V = 0 и Z = 0 на выходе 0-триггера 13 нулевой сигнал, конъюнкторы 8 закрыты. На выходе 0-триггера 15 единичный сигнал, управляющие импульсы с компараторов

5 поступают на выходные формирователи I I, работают вентили второго комплекта (27 — 32) .

При Z = 1 в нагрузке — нулевая пауза тока, токи параметрического источника тока

20 замыкаются через внутренний контур, образованный вентилями обоих комплектов. При этом единичные сигналы формируются на выходах обоих 0-триггеров (13 и 15), открыты конъюнкторы 8 и 10, управляющие импульсы формируются на выходные.формирователи обоих комплектов.

При включении вентиля, его анодное напряжение уменьшается, соответствующий компаратор возвращается в исходное состояние, сигнал с выходного формирователя снимается, таким образом автоматически устанавливается длительность импульсов на управляющие электроды минимально необходимая .для включения вентиля, Нами рассмотрено функционирование уст/ройства управления в длительно повторяющихся режимах. При переходе из одного режима в другой для обеспечения оптимального протекания процессов в параметрическом источнике 20 необходимо производить коммутации токовых цепей только при спаде тока данной фазы к нулю. При спаде тока данной фазы к нулю ток должен перейти на второй вентиль данной фазы (например, с вентиля 21 на вентиль 24), при этом на вентиле 24 появляется положительное анодное напряжение, его появление через компаратор

4 и дизъюнктор 12 передается на тактирую5 964960 щий вход. (С вЂ” вход) 0-триггера 13, который может изменить свое состояние в соответствии с сигналом на его входе. Наличие дизъюнктора 12 позволяет подавать на вход триггера 13 информацию о смене знака тока в каждой фазе, именно эти моменты времени синхронизируют работу триггера: изменение

его состояния синхронизировано с моментами перехода фазовых. токов параметрического источника через ноль. Выходной импульс

0-триггера 13 разрешает или блокирует подачу управляющих импульсов на очередные вентили первого комплекта (вентили 21-26).

Аналогично работает 0-триггер 15 во втором блоке. 1S

Таким образом, данное изобретение позволяет осуществлять управление вентильными преобразователями, содержащими параметрический источник тока.

Формула изобретения

Устройство для управления реверсивным выпрямителем, состоящим из двух m-фазных мостов и параметрического источника тока, содержащее два блока, каждый из которых состоит из 2m узлов, включающих последовательно соединенные компаратор, конъюнктор и выходной формирователь, о тличающееся тем,что,сцелью расширения функциональных возможностей, оно снабжено m датчиками анодных напряжений, датчиком выходного напряжения, m . вычитателями, двумя источниками постоянного напряжения, двумя дизъюнкторами, двумя О-триггерами, эадатчиком полярности тока с выходом V, задатчиком нулевой паузы с выходом Z и двумя логическими узлами, реализующими функциями (Ч+ Z) и (V+ Z) причем прямые входы одних m компараторов первого блока и инверсные входы одних m компараторов второго блока соединены с соответствующими датчиками анодных напряжений, прямые входы других m- компараторов первого блока и инверсные входы других m компараторов второго блока соединены с соответствующими датчиками анодных напряжений через первые входы вычитателей, вторые входы которых соединены с датчиком выходного напряжения, инверсные входы компараторов первого блока соединены. с первым источником постоянного напря-. жения, прямые входы компараторов второго блока соединены с вторым источником посто20 янного напряжения, выходы всех компараторов каждого блока соединены с входами соответствующего дизъюнктора, выход каждого дизъюнктора подключен к тактовому входу соответствующего О-триггера, выход

2S каждого триггера соединен с вторыми входами конъюнкторов соответствующего блока, задатчик полярности тока и задатчик нулевой паузы связаны с О-входами триггеров через логические узлы.

Зп, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР N 738097, кл. Н 02 P 13/24, 1977.

2. Булатов О. Г., Чаплыгин Е. Е. Учебное пособие по курсу "Преобразовательные установки", из-во МЭИ, М., 1979, с. 43 — 45.

964960

Составитель О. Парфенова

Техред E. Харитончик Корректор Н. Буряк

Редактор А. Гулько

Заказ 7686/45

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Тираж 721 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5