Устройство дискретной автоподстройки частоты

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6() Дополнительное к авт. свид-ву (22) Заявлено 291280 (21) 3226699/18-09 51)М. Кл.з

Н 03 L 7/10 с присоединением заявки. ¹

Государственный комитет

СССР. по делам изобретений и открытий (23) Приоритет—

Опубликовано 07.10.82. Бюллетень № 37 (53) УДК 621.3 6.

° 662 (088,8) Дата опубликования описания 07.10.82 (72) Авторы изобретения

В.Б. КУДРЯвЦев, Б.Ф. Мастерских и Т.И. Т (71) Заявитель (54) УСТРОЙСТВО ДИСКРЕТНОЙ АВТОПОДСТРОЙКИ

ЧАСТОТЬ1

Изобретение относится к радиотехнике и может быть использовано в устройствах автоматической подстройки частоты.

Известно устройство дискретной автоподстройки частоты, содержащее последовательно включенные смеситель, соединенный вторым входом с гетеродином, управляющий вход которого подключен к выходам реверсивного счетчика через преобразователь код - напряжение (ПКН), а цифровой дискриминатор частотной ошибки соединен с опорным генератором и подключен к управляющему входу реверсивного счетчика через коммутатор фазы, управляемый с выхода реверсивного счетчика через схемы совпадений. Указанное устройство осуществляет подстройку частоты гетеродина по внешнему сигналу и запоминание установившегося значения частоты эа счет прекращения подачи импульсов на счетный вход реверсивного счетчика (1).

Однако указанное устройство не обеспечивает высокую скорость перестройки частоты из-за отсутствия элемента регулировки скорости подстройки частоты между выходом смесителя и входом реверсивного счетчика и не вырабатывает сигнал окончания процесса подстройки и фиксации кода в реверсивном счетчике, что не nosволяет автоматически прекратить процесс подстройки и ухудшает помехоустойчивость запоминания подстроенной частоты.

1р Целью изобретения является повышение помехоустойчивости запоминания подстроенной частоты.

Цель достигается тем, что в устройстве дискретной автоподстройки частоты, содержащем .последовательно соединенные реверсивный счетчик, преобразователь код-напряжение, подстраиваемый генератор и смеситель, другой вход которого является входом устройства, а также цифровой дискриминатор частотной ошибки н опорный генератор, между выходом опорного генератора и первым счетным входом реверсивного счетчика включены последовательно делитель частоты .с переменньм коэффициентом деления и элемент совпадения, между выходом смесителя и управляющими входами делителя частоты с переменным коэффициентом деления включены посЗО ледовательно усилитель промежуточ964983 ной частоты, многополосный фильтр с.нечетным числом выходов и шифратор номера выхода многополосного фильтра, между средним выходом многополосного. фильтра и другим входом элемента совпадения и установочньии входа- 5 ми реверсивного счетчика включены соответственно инвертор и элемент блокирОвки кода, при этом Цифровой дискриминат(ор включен между выходами многополосного фильтра и вторьм счет-10 ным входом реверсивного счетчика, а выход опорного генератора дополнительного подключен к дополнительному входу многополосного фильтра.

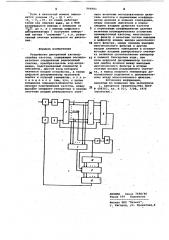

На чертеже изображена стРУктУРная электрическая схема устройства.

Устройство содержит смеситель 1, первый вход которого соединен со входом устройства, второй вход соединен с выходом подстраиваемого генератора 2, а выход соединен со 20 входом многополосного фильтра (МПФ)

3 через усилитель 4 промежуточной частоты (УПЧ) 4. Второй вход .МПФ соединен с выходом опорного генератора 5. Выходы МПФ подключены к 25 шифратору 6 номера выхода МПФ и цифровому дискриминатору 7 частотной ошибки (ЦДЧО) . Код номера возбужденного фильтра 3 с шифратора.б подается на управляющие входы делителя 8,30 частоты с переменньм коэффициентом деления (ДПКД), который соединен так-, же с опорным генератором 5. Импульсы с выхода ДПКД 8 подаются на вход реверсивного счетчика 9 через элемент

10 совпадения, на второй вход которой подается сигнал разрешения подстройки из МПФ через инвертор 11.

Выход цифрового дискриминатора 7 соединен с соответствующим входом 40 реверсивного счетчика 9. Вход эле-. мента 12 блокировки кода соединен со средним выходом МПФ 3, а выходы элемента 12 подключены к установоч.ным входам реверсивного счетчика 9.

Выходы реверсивного счетчика 9 соединены с входами преобразователя 13 код-напряжение, а его выход подключен к управляющему входу подстраиваемого генератора 2.

Устройство работает следующим образом.

Входной сигнал частоты f смешивается в смесителе 1 с сигналом fг подстраиваемого генератора 2. Сигнал разности этих частот поступает через усилитель 4 промежуточной частоты на вход многополосного фильтра 3, где сравниваеФся с сигналом опорного генератора 5. В результате сравнения появляется сигнал в виде логи60 ческой единицы на одном из п (n нечетно) выходов многополосного фильтра 3, соответствующего диапазону частот, в котором находится разность (f — f ) . Если, например, 65 после включения устройства (— f )

r,iF и йс — fry О, где iF - заданный допуск на точность установки частоты подстраиваемого генератора, то сиг" нал появляется на одном из выходов с номером от 1 до (" ")а

При этом в цифровом дискриминаторе 7 в ыра батываетс я сигнал Сложение,который поступает на вход реверсивного счетчика 9, разрешая сложение счетных импульсов. Одновременно сигнал с возбужденного выхода

ИПФ поступает в шифратор б, где преобразуется в код номера возбужденнбго выхода,.второй поступает на вход управления коэффициентом деления ДПКД 8..

Если (f — f ) велик, то в ДПКД устанавливается минимальный коэффициент деления, если (fc — йг) мал, то максимальный. Таким образом, осуществляется процесс ступенчатого

Регулирования скорости подстройки частоты, что позволяет достичь максимальной скорости подстройки при заданной точности путем соответствующего подбора кодов в шифраторе.

Импульсы с выхода ДПКД проходят в рассматриваемом случае через открытый элемент 10 совпадения на счетный вход реверсивного счетчика

9, поскольку не возбужден средний выход с нОмером ) многополосга+ ) ного фильтра, и на выходе инвертора

11 имеется сигнал логической единицы. Элемент блокировки кода 12 при этом выключен. Код в реверсивном счетчике увеличивается, что приводит к возрастанию напряжения на выходе ПКН 13. Это напряжение воздействует на подстраиваемый генератор 2 таким образом, чтобы уменьшался модуль разности (fc — fr) ° причем отработка рассогласования идет по кратчайшему пути, так как направление счета в реверсивном счетчике однозначно определено номером возбужденного выхода в МПФ-3;

После того как в процессе отра» ботки рассогласования выполнится условие (f — Е) < ь Р, сигнал логи" ческой едийицы появится на среднем выходе МПФ с номером -" -)- . При этом закроется элемент 1К совпадения; прекратив подачу счетных импульсов на реверсивный счетчик 9, и включится элемент 12 блокировки кода. Он предохранит от искажения запоминаемый в реверсивном счетчике код, соответствующий заданной подстроенной частоте, и повышает таким образом, помехозащищенность запоминания частоты.

Напряжение со среднего выхода

МПФ 3, имеющего номер, может быть использовано для сигнализации об окончании процесса подстройки.

964983

Если в начальный момент выполнится условие (йс — Е) > а Г; (fo — f< 0), то схема работает также как описано виае, но в ИПФ возбуждаются выходы с номерами от до и н с выхода цифрового дискриминатора 7 поступает инверсный сигнал сложенйе, т.е, реверсивный счетчик включается на вычитание.

Формула изобретения

Устройство дискретной автоподстройки частоты, содержащее последовательно соединенные реверсивный счетчик, преобразователь код-напряжение, подстранваемый генератор и смеситель, другой вход которого является входом устройства, а также . цифровой дискриминатор частотной ошибки и опорный генератор, о т л ич а ю щ е е с я тем, что, с целью повышения помехоустойчивости sanoминания подстроенной частоты, между выходом опорного генератора и первьм счетчньм входом реверсивного счетчика включены последовательно дели тель частоты с переменньм коэффициентом деления и элемент совпадения, между выходом смесителя и управляющими входами делителя частоты с переменяют коэффициентом деления включены последовательно усилитель промежуточной частоты, многополосный Фильтр о нечетным числсм выходов и шифратор номера выхода многополосного фильтра, между средним выходом многополосного фильтра и другим входси элемента совпадения и устаиовочяыии входами реверсивного счетчика включены соответственно инвертор и элемент блокировки «ода, при этом цифровой дискриминатор частот» ной ошибки включен между выходами многополосного фильтра и вторыа счетным входом реверсивного счетчика, а выход опорного. генератора дополнительно подключен к дополнительному входу многополосного фильтра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 488303, кл. Н 03 ) 7/08, 1976 (прототип) ..ВНИИПИ Заказ 7688/46

Тираж 959 Подписное »

Филиал ППП "Патент", r. Ужгород, ул. Проектная,4