Бортовое устройство связи

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (»»)964996 (61) Дополнительное к авт. свид-ву (22) Заявлено 16.03.81 (21) 3260434/18-09

Р11М Кп з

Н 04 В 7/165 с присоединением заявки ¹ (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 07. 10.82. Бюллетень №37 (531 УДК 621. 396. .93(088.8) Дата опубликования. описания 07. 10. 82 (72) Авторы изобретения

Н.Н. Бирюков, Г.Д. Козлов, Ю.П. Паньковский В) . Семенов, В.П. Соколов, А ° А ° Чаднов и В.С. Я требОв

Ю(.(»И",,я -.. !

à» 1 е» Г»

1 Ей И",", ». .;

1 „ л,» „"»,,Т "» (71) Заявитель (54) БОРТОВОЕ УСТРОЙСТВО СВЯЗИ

4

Изобретение относится к технике передачи информации, а именно к системам многоканальной связи.

Известно бортовое устройство свя5 зи, содержащее приемный .блок, детектор, блок выделения двоичной информации, измеритель частоты, блок фазовой автоподстройки частоты (ФАПЧ), формирователь кода, коммутатор, сумматор, формирователь сигнала управления, а также последовательно -соединенные блок регистров, блок памяти, формирователь цифрового потока и передающий блок, причем выход блока регистров подключен соответственно к второму входу формирователя цифрового потока и входу дешифратора, выход которого подключен к третьему входу формирователя цифрового потока f1), Однако у известного устройства недостаточное быстродействие.

Цель изобретенйя — повышение быстродействия.

Для этого в бортовое устройство связи, содержащее приемный блок, де- 25 тектор, блок выделения двоичной информации, измеритель частоты, блок фазовой автоподстройки частоты (ФАПЧ ), формирователь кода, коммутатор, сумматор, формирователь сигнала управ- 30 ления, а также последовательно соединенные блок регистров, блок памяти, формирователь цифрового потока и передающий блок, причем выход блока регистров подключен соответственно к второму входу формирователя цифрового потока и входу дешифратора, выход которого подключен к третьему входу формирователя цифрового потока, введены п-каналов, каждый из которых содержйт последовательно соединен- ные полосовой фильтр, детектор огибающей и пороговый блок, а также преоб. разователь код-аналог, блок автоматической регулировки, формирователь временного интервала, формирователь порогового сигнала и синтезатор частот, выходы которого подключены соответственно к входу приемного блока, к входу формирователя порогового сигнала, к входу формирователя сигнала управления, к первому входу измерителя частоты и к входу блока выделения двоичной информации, и к первому входу блока ФАПЧ, выход которого через последовательно соединенные детектор, блок выделения двоичной информации и сумматор подключен к входу блока регистров, при этом выход приемника подключен соответственно к входам по964996 лосовых фильтров, к входу блока автома тической регулировки, к второму входу блока ФАПЧ и к второму входу детектора, причем выход формирователя временного интервала через последовательно соединенные1формирователь сигна- 5 ла управления и форгя|рователь порогового сигнала подключен к входам соответствующих пороговых блоков, выходы которых через коммутатор подклвчены соответственно к входу формирователя !0 кода и к третьему входу формирователя сигнала управления, четвертый вход которого соединен с вторым выходом блока ФАПЧ, третий выход которого через измеритель частоты подключен 15 к другому входу сумматора, при этом выход формирователя кода частоты через преобразователь код-аналог подключен к третьему входу блока ФАПЧ, причем другой выход блока выделения двОичной информации подключен к третьему входу измерителя частоты, второй выход формирователя сигнала управления подключен к входу формирователя временного интервала, а выход блока автоглатической регулировки подключен к второму входу приемного блока.

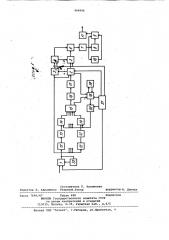

На чертеже приведена структурная электрическая схема устройства.

Бортовое устройство связи содер- жит приемный блок 1,. блок 2 фазовой автоподстройки частоты (ФАПЧ), детектор 3, блок 4 выделения двоичной информации, измеритель 5 частоты, сумматор б, блок 7 регистров, блок 8 З5 памяти, формирователь 9 цифрового по» тока, дешифратор 10, передающий блок

Ы, полосовой фильтр 12, детектор 13 огибающей, пороговый блок 14, коммутатор 15, формирователь 16 кода, пре- 0 образователь 17 код-аналог, формирователь 18 сигнала управления, форгЯРователь 19 временного интервала, форми| рователь 20 порогового сигнала, синтезатор 21 частот, блок 22 автомати- 45 ческой регулировки.

Устройство работает следующим образом.

Радиосигнал поступает на вход приемного блока 1, в котором осуществля- 50 ется преобразование частоты радиосигнала в проме><уточную частоту и его усиление. Иирина полосы пропускания тракта промежуточной частоты приемного блока 1 выбирается больше ширины спектра частот радиосигнала с учетом возможных его измерений за счет эффекта Доплера и суммарной нестабильности частоты синтезатора 21 частот.

Запас на ширину полосы пропускания тракта промежуточной частоты необ- 60 ходим для организации автоматической регулировки усиления тракта промежу- точной частоты по уровню шумов, которая осуществляется при помощи блока 22 автоматической регулировки. 65!

Синтезатор 21 частот осуществляет формирование из сигнала эталонной частоты сигналов с частотами, являющимися гетеродинными для приемного блока 1, сигнала опорной частоты для блока 2 ФАПЧ и сигналов опорных сеток част т для формирователя 20 порогового сигнала, блока формирователя 18 сигнала управления, блока 4 выделения двоичной информации и измерителя 5 частоты.

Радиосигнал с выхода тракта промежуточной частоты приемного блока 1 поступает на вход детектора 3, вход блока 2 ФАПЧ и входы каждого из и полосовых фильтров 12, полосы которых перекрывают диапазон возможных изменений несущей частоты приходящего радиосигнала. Сигнал с частотой радиосигнала s зависимости от положейия на оси частот, определяемого в основном доплеровским смещениегл, попадает в полосу пропускания одного из полосовых фильтров 12 и далее, после детектирования соответствувщим детектором 13 огибающей на один вход порогового блока 14 в том v

14 уровнем напряжения с выхода детек. тора 13 огибающей на выходе порогового блока 14 образуется сигнал, который поступает на коммутатор 15.

Коммутатор 15 подклкчает к формирователю 16 кода тот канал, в котором присутствует сигнал и отключает все остальные каналы. Одновременно сигнал с выхода коммутатора 15 через формирователь 18 сигнала управления воздействует на формирователь

20 порогового сигнала и фиксирует его уровень ° При этом начинает работать формирователь 19 временного интервала.

На выходе формирователя 16 кода вырабатывается код .номера канала, в котором присутствует сигнал, этот код в преобразователе 17 код-аналог преобразуется в напря>хение для грубой подстройки частоты блока 2 ФАПЧ.

Блок 2 фазовой автоподстройки частоты с ошибкой, не превышающий ее полосу схватывания, подстраивается под частоту радиосигнала на ее входе и, через время, определяемое переходным процессом, выходная частота блока 2

ФАПЧ будет синхронна с частотой радиосигнала. Эта частота в качестве опорной подается на детектор 3, в котором производится детектирование символов информации. Одновременно сигнал, свидетельствующий о синхронизме в блоке 2 ФАПЧ, поступает на формирователь 18 сигнала управления

964996 и выключает формирователь 19 времен ° ного интервала, В случае, если эа время, заданное в формирователе 1 временного интервала, блок 2 ФАПЧ в синхрониэм не вошел, то по истечении времени, заданного в формирователе 19 временного интервала, формирователь 18 сигнала управления вырабатывает сигнал, который включает формирователь 20 порогового сигнала.

С выхода детектора 3 символы информации поступают на блок 4 выделения двоичной информации, где производится .символьная, кадровая синхронизация и выделение двоичных символов принимаемой информации. Сигнал несущей, заключающей в себе доплеровское смецение частоты с выхода блока 2 ФАПЧ подается на измеритель

5 частоты, где формируется код частоты Доплера, суммируется в сумматоре 6 суммирования двоичной информации и через блок 7 регистров двоичная информация поступает в блок памяти 8 на формирователь 9 цифрового потока и на дешифратор 10. Блок

8 памяти служит для сбора и хранения информации на время отсутствия радиосигнала на входе приемного блока 1. При этом возможна непосредственная ретрансляция информации в реальном времени, для чего в структуре входного радиосигнала заложена соответствующая команда, которая будет расшифрована дешифратором

10, который одновременно может разрешить выдачу информации через формирователь 9 цифрового потока на передающий блок 11.

Таким образом, предлагаемое устройство обладает достаточно высоким быстродействием.

Формула изобретения

Бортовое устройство связи, содержащее гриемный блок, детектор, блок выделения двоичной информации, измеритель частоты, блок фаэовой автоподстройки частоты (ФАПЧ), формирователь кода, коммутатор, сумматор, формирователь сигнала управления, а также последовательно соединеные блок регистров, блок памяти, формирователь цифрового потока и передающий блок, причем выход блока регистров подключен соответственно к второму входу формирователя цифро10

15 вого потока и входу дешифратора, выход которого подключен к третьему входу формирователя цифрового потока, о т л и ч а ю щ е е с я тем, . что, с целью повышения быстродействия, введены И каналов, каждый из которых содержит последовательно соединенные полосовой фильтр, детектор огибаюцей и пороговый блок, а также преобразователь код-аналог, блок автоматической регулировки, формирователь временного интервала, формирователь порогового сигнала и синтезатор частот, выходы которого подключены соответственно к входу приемного блока,к входу формирбвателя порогового сигнала, к входу фор мирователя сигнала управления, If первому входу измерителя частоты и к входу блока выделения двоичной щ информации, и к первому входу блока

ФАПЧ, выход которого через последовательно соединенные детектор, блок выделения двоичной информации и сумматор подключен к входу блока регистров, при этом выход приемного блока подключен к входам полосовых фильтров, к входу блока автоматической регулировки, к второму входу блока ФАПЧ и к второму входу детектора, причем выход формирователя вре. менного интервала через последовательно соединенние формирователь сигнала управления и формирователь порогового сигнала подключен к входам соответствующих пороговых блоков

З5 выходы которых через коммутатор подключены соответственно к входу формирователя кода и к третьему входу формирователя сигнала управления, четвертый вход которого соединен с

40 вторым выходом блока ФАПЧ, третий выход которого через измеритель частоты подключен к другому входу сумматора, при этом выход формирователя кода частоты через преобразователь

45 код-аналог подключен к третьему входу блока ФАПЧ, причем другой выход блока выделения двоичной информации подключен к третьему входу измерителя частоты, второй выход

50 формирователя сигналов управления подключен к входу формирователя временного интервала, а выход блока автоматической регулировки .подключен к второму входу приемного блока.

Источники информации, принятые во внимание прн экспертизе

1. Авторское свидетельство СССР по заявке Р 2841301, кл. Н 04 В 7/165, 1979 (прототип).

964996

Составитель Т. Колпикова

Редактор Л. Авраменко ТехредМ.Тепер КорректоР М Демчик

Заказ 7690/47 тираж 688 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, >(-35, Раущская наб., д.4/5

Филиал ППП "Патент", г.Ужгород, ул.Проектная, 4