Пороговый декодер сверточного кода

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ б

Союз Советскик

Социалистических

Республик (964999 (61) Дополнительное к авт. свид-ву (22) Заявлено 16. 03. 81 (21)3261334/18-09 с присоединением заявки Нов

Р11М К з

Н 04 L 1/10

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Р4 УДК 621. 394.14 (088 ..8) Опубликовано 071082 Бюллетень М37

Дата опубликования описания 07 . 10 .82 (72) Авторы изобретения

В.И.Долгов, И.В.Рогожин, Л.Б.1Иакаров, В.Д.Пашовкин, С.П.Белов и A.È.Калиниченко (71) Заявитель (54) ПОРОГОВЫЙ ДЕКОДЕР СВЕРТОЧНОГО КОДА

-Изобретение относится к технике связи и предназначено для использования в аппаратуре передачи дискретной информации.

Известен декодер сверточного кода, содержащий последовательно соединейные кодер, анализатор синдрома, первый пороговый обнаружитель, первый блок запрета коррекции, выход которого подключен к соответствующим входам анализатора синдрома, а также блок обнаружения пакетов ошибок и последовательно соединенные второй пороговый обнаружитель и второй блок запрета коррекции, выход которого подключен к первому входу корректора ошибок (1).

Однако известный пороговый декодер обладает недостаточной помехоустойчивостью из-за эффекта размножения ошибок.

Цель изобретения †. повышение помехоустойчивости.

Для этого в пороговый;декодер сверточного кода, содержащий последовательно соединенные кодер, анализатор синдрома, первый пороговый обнаружитель, первый блок запрета коррекции, выход которого подключен к, соответствующим входам анализатора синдрома, а также блок обнаружения пакетов ошибок и последовательно со5 единенные второй пороговый обнаружитель, второй блок запрета коррекции, выход которого подключен к первому входу корректора ошибок, введены последовательно соединенные блок задержки и дополнительный анализатор синдрома, а также блок управления коррекцией, блок задержки, сигналов управления и блок задержки информационной последовательности, причем к входу блока обнаружения пакетов ошибок подключен выход первого блока запрета коррекции, а выход блока обнаружения пакетов ошибок подключен к входу блока управления коррекцией, выход которого подключен к второму входу первого блока запрета коррекции непосредст . венно и через блок задержки сигналов управления — ко второму входу второго блока запрета коррекции,а выход второго блока запрета коррекции подключен к

2з соответствующим входам дополнительного анализатора синдрома, при этом второй вход корректора ошибок соединен с выходом кодера через блок задержки информационной последовательЗ0 ности, а входы кодера объединены с

964999

Формула изобретения

Пороговый декодер сверточного кода, содержащий последовательно соединенные кодер, анализатор синдрома, первый пороговый обнаружитель, первый блок запрета коррекции, выход которого подключен к соответствующим входам анализатора синдрома, а также блок обнаружения пакетов ошибок и последовательно соединенные второй пороговый обнаружитель и второй блок запрета коррекции, выход которого подключен к первому входу корректора ошибок, отличающийся тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные блок задержки и дополнительный анализатор синдрома, а также блок управления коррекцией, блок задержки сигналов управления и блок задержки информационной последовательности, причем к входу блока обнаружения пакетов ошибок подключен выход первого блока запрета коррекции, а выход блока обнаружения пакетов ошибок подключен к входу блока управления коррекцией, выход которого подключен к второму входу первого блока запрета коррекции непосредственно и через блок задержки сигналов управления — ко второму входу второго блока запрета коррекции, а выход второго блока запрета коррекции подключен к соответствующим входам дополнительного анализатора синдрома, при этом вход корректора ошибок соединен с выходом кодера через блок задержки информационной последовательности, а входы кодера объединены с соответствующими входами блока задержки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 586571, кл. Н 04 L 1/10, 1976 (прототип). соответствующими входами блока задержки.

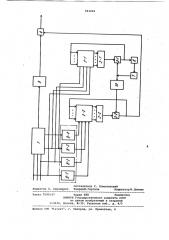

На чертеже представлена структурная схема порогового декодера сверточного кода.

Декодер содержит кодер 1, акали- 5 затор 2 — 1 синдрома, дополнительный анализатор 2-2 синдрома, первый пороговый обнаружитель 3-1, второй пороговый обнаружитель 3-2, корректор

4 ошибок, первый блок 5-1 запрета коррекции, второй блок 5-2 запрета корреции, блок 6 обнаружения пакетов ошибок, блок 7 управления коррекции, блок 8 задержки, блок 9 задержки информационной последовательности, блок 15

10 задержки сигналов управления.

Декодер, работает следующим образом. . Когда в дискретном канале нет ошибок, то кодер 1 формирует на проверочных выходах последовательности идентич ные проверочным последовательностям на выходе дискретного канала.В этои случае входные цепи основного и дополнительного анализаторов 2 синдрома формируют последовательности нулей. Пороговые обнаружители 3 порогов не превышают и коррекции не происходит.

Если произошли ошибки в кодовой последовательности с кратностью меньшей корректирующей способности кода, то ЗО в проверочных последовательностях образуются единицы, которые поступают в анализаторы 2 синдрома таким образом, что сначала поступают в основной анализатор 2-1 синдрома и лишь спустя 35 время, равное длительности К-информационных символов, через блоки 8-1

8>-4- задержки проверочных последовательностей в дополнительный анализатор 2-2 синдрома. При этом с выходов 40 пороговых обнаружителей 3 появляются единичные символы коррекции, происходит коррекция анализаторов 2 синдрома, очищая синдром от размноженной ошибки, и коррекция искаженных инфор- 45 мационных символов кодовой комбинации, при этом блок 7 управления коррекцией блоками 5 запрета коррекции не выдает сигнал управления на запрет коррекции.

Для согласования момента коррекции

50 искаженных информационных символов кодовой комбинации в корректоре 4 ошибок используются блок 10 задержки сигнала

1управления блоками 5 запрета коррекции, задерживая соответствующие сигналы на

55 длительность К-информационных символов. . При размножении ошибок с выхода порогового обнаружителя 3-2 единичные сигналы коррекции поступают на блок 6 . обнаружения пакетов ошибок, который, 60 насчитав больше заданного числа едиt ниц, дает сигнал на блок 7 управления блоками 5 запрета коррекции о запрещении ложной коррекции в анализаторах

2 синдрома и корректоре 4 ошибок.

Таким образом, отключая цепи коррекции на длительность, равную Кинформационным символам, полностью меняем состояние регистров анализа.торов 2 синдрома, тем самым очищаются анализаторы от размноженной ошибки, и не происходит ложной коррекции ийформационных символов. В результате повышается помехоустойчивость деко дера иэ-за предотвращения размноже- .

:ний ошибок.

964999

Составитель С. Осмоловский

Редактор Л. Авраменко ТехредМ.Гергель Корректор М. Демчик

Тираж 688 Подписное

BHH_#_IH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 7690/47

Филиал IIVI "Патент", г. Ужгород, ул. Проектная, 4