Устройство для сопряжения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик и

= .к Ь4 "» ="

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву Р 913359 (22) Заявлено 09.01.79 (21) 2709734/18-24 (51) M Rn .е

С 06 Е 3/04 с присоединением заявки ¹â€” (23) Приоритет

Государственный комитет

СССР ио делам изобретений и открытий

t53) УДК 681. 325 (088.8}

Опубликовано 15-10.82е Бюллетень № 38

Дата опубликования описания 15.10.82 ун

П," з "- н з Пт

"ч <. т- х. ". (72) Авторы изобретения

Н.П.Вашкевич, Н.Н.Коннов и К.И.Шестаков

И1.

ПензенсКий политехнический институт (71) Заявитель ч 1., 1 (54} УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

Изобретение относится к автоматике и вычислительной технике и может найти применение, например, в качестве буферного устройства между двумя разноскоростными устройствами передачи информации.

По основному авт.св. 9 913359 иэвестно устройство для сопряжения, содержащее узел синхронизации и узел памяти, включающий группу последовательно соединенных регистров, включающих триггера информационных разрядов и триггер служебного разряда, элементы И и И-НЕ по числу регистров, причем информационный вход узла памяти соединен с входом триггеров информационных разрядов первого регистра, а выходы триггеров информационных разрядов последнего регистра являются информационным выходом узла памяти, вход триггера служебного разряда первого регистра является призначным входом узла памяти, а выход триггера служебного разряда последнего регистра является призначным входом памяти первые входы элементов И соединены с входом тактовых импульсов узла памяти и с первым входом узла синхронизации и входом тактрвых импульсов устройства, первые входы; элементов И-HE .подключены к синхронизирую щему входу узла памяти и первому выходу узла синхронизации, второй вход которого является входом чтения информации устройства, выход

i-ro элемента И соединен с управляющим входом i-го регистра, а второй 0 вход - с выходом i-ro элемента И-HE второй вход которого подключен к выходу триггера служебного разряда

i-го регистра, а третий вход — к выходу триггера служебного разряда, (i+1}-ro оегистра (1).

Недостатком этого устройства является низкое быстродействие, так как информационные коды могут поступать на вход устройства только через

20 такт. е

Цель изобретения — повышение быс« тродействия устройства.

Поставленная цель достигается тем, что в устройство введены триггер, узел формирования сигнала переполне» ния, узел формирования сигнала готонности, второй узел памяти, пять элементов И и элемент ИЛИ, причем первые входы первого, второго и третьего элементов И соединены с вхоЗОз дом признака информации устройстват

966685 вторые входы первого и третьего элементов И соединены с соответствующими выходами триггера, вход которого подключен к выходу второго элемента И, вторым входом соединенного с входами тактовых импульсов первого и второго узлов памяти и входом тактовых импульсов устройства, выход первого элемента И соединен с призначным входом первого узла памяти и первым входом узла формирования сигнала пере- 10 полнения, второй вход которого подключен к выходу третьего элемента И и призначному входу второго узла памяти, третий и четвертый входы — соответственно к управляющим выходам 15 первого и второго узлов памяти, а выход является выходом сигнала переполнения устройства, информационные выходы первого и второго узлов памяти соединены соответственно с первыми входами четвертого и .пятого элементов И, выходы которых подключены

k.соответствующим входам элемента

ИЛИ, выходом соединенного с информационным выходом устройства, второй вход четвертого элемента И соединен с вторым выходом узла синхронизации и первым входом узла формирования сигнала готовности, второй вход которого подключен к призначному выходу первого узла памяти, третий вход -30 к призначному выходу второго узла памяти, четвертый вход — к третьему выходу узла синхронизации и второму входу пятого элемента И, а выход является выходом сигнала готовности . устройства, четвертый выход узла синхронизации соединен с синхронизирующим входом второго узла памяти.

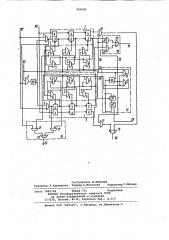

На чертеже представлена блок-схе- 40 ма устройства, Схема содержит узлы 1 и 2 памяти, состоящие из регистров с триггером 3 служебного разряда и триггерами 4 инФормационных разрядов, элементами 45

И-HR 5 и элементами И б, элементы

И 7-11, элемент ИЛИ 12, узел 13 синхронизации, состоящий из синхронного триггера 14, элементов И-HE 15 и асинхронных триггеров 1б и 17, узел 18 формирования сигнала готовности и узел 19 формирования сигнала переполнения, состоящие из элементов ИЛИ

20 и элементов И 21, триггер 22, первый 23, четвертый 24, третий 25 и второй 26 выходы узла 13 синхронизации, вход 27 признака информации устройства, информационный вход 28 устройства, вход 29 чтения информа-, ции, информационный выход 30 устройства, выход 31 сигнала готовности <60 устройства, выход 32 сигнала переполнения устройства, вход 33 тактовых импульсов устройства.

Устройство работает следующим образом. 65

При включении устройства обнуляются все триггеры 3, триггеры 14 и

17, а триггеры 16 и 22 устанавливаются в одинаковое состояние (допустим единичное).

На выходах всех .элементов И-НЕ 5 высокий уровень, который разрешает прохождение тактовых импульсов через элементы И б.

Информационный код, поступающий в устройство, сопровождается "1" на входе 27 признака информации, которая записывается в зависимости от состояния триггера 22 в триггер 3 первого регистра узлов 1 или 2 тактовым импульсом, который, кроме того, перебрасывает и триггер 22 в противоположное состояние. Поэтому при поступлении следующего информационного кода запись "1" с входа 27 происходит в другой узел памяти. Таким образом, нечетные информационные коды сов"местно с признаком записываются в узел 1, а четные информационные ко-. ды — в узел 2.

Тактовые импульсы непрерывно подаются в устройство и первый занесенный код, сопровождаемый "1" в служебном разряде, последовательно через все регистры продвигается в последний регистр, после чего, на выходе последнего элемента И-НЕ 5 появится низкий уровень и запись новой информации в последний регистр не происходит, поскольку тактовые импульсы не проходят на синхровходы триггеров последнего регистра. Аналогичное запрещение записи в последний регистр узла 2 происходит, когда в нем окажется второй занесенный код, сопровождаемый "1" в триггере 3. Третий занесенный код, достигнув предпоследнего регистра узла 1, своим служебным разрядом запрещает запись в него. Подобным образом идет заполнение всех регистров .обоих узлов памяти.

Триггер 16 подключает информационный регистр 2 узла 1 к выходу 30 через элемент И 10 и элемент ИЛИ 12, а через элементы 21 и 20 узла 18 разрешает прохождение высокого уровня с выхода триггера на выход 31 готовности устройства, что свидетельствует о наличии информации для считывания. После считывания информации, которое может происходить в любой момент времени, сигнал на входе

29 чтения информации устанавливает триггер 17 в единичное состояние.

Первый пришедший после этого тактовый импульс взводит триггер 14 в единичное состояние, что приводит к сбросу триггера 17 по второму тактовому импульсу и к появлению низкого уровня на выходе 23. Поскольку на выходе элементов И-НЕ 5 узла 1 высокий уровень, то следующий такто9666

Формула изобретения вый импульс сдвигает все содержимое узла 1 на один разряд и сбрасывает триггер 14, который переключает триггер 16 по счетному входу, и к выходу 30 через элементы И 11 и

ИЛИ 12 уже подключается регистр

5 узла 2 и на выход 31 идет сигнал с триггера 3 из того же узла 2. После считывания кода из узла 2 процедура работы узла 13 повторяется с той лишь разницей; что низкий уровень по- 1О является на его выходе 24. Затем считывается код из узла 2 и так далее. Таким образом, информация считывается из устройства в порядке своего поступления в него. 15

При переполнении устройства на выходе 32 появляется высокий уровень.

Таким образом, период тактовых импульсов для прототипа и для данно1о устройства определяется в основном временем переключения триггера служебного разряда и элемента

И-НЕ 5. Но в прототипе один информационный код записывается за два так- 25 .товых импульса, а в данном устройстве — за один, тем самым быстродействие устройства для сопряжения rioamaaeeca.

Наиболее эффективно устройство может использоваться для сопряжения в тех случаях, когда возможны ситуации пиковых иагрузок, т.е . поступает большой объем информации за короткий промежуток времени.

Устройство для сопряжения по авт.св. 9 913359, о т л и ч а ю— щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены триггер, узел формирования сигнала переполнения, узел формирования сигнала готовности, второй

Узел памяти, пять элементов И и эле- 45 мент ИЛИ, причем первые входы перво85 б

J го, второго и третьего элементов И соединены с входом признака информации устройства вторые входы первого и третьего элементов И соединены с соответствующими выходами триггера, вход которого подключен к выходу второго элемента H вторым входом соединенного с входами тактовых импульсов первого и второго узлов памяти и

-входом тактовых импульсов устройства, выход первого элемента И соединен с призначным входом первого узла памяти и первым входом узла формирования сигнала переполнения. второй вход которого подключен к выходу третьего элемента И и призначному входу вто-. рого узла памяти, третий И четвертый входы — соответственно к управляющим выходам первого и второго узлов памяти, а выход является выходом сигнала переполнения устройства, информационные выходы первого и второго узлов памяти соединены соответственно с первыми входами четвертого и пятого элементов И, выходы которых .подключены к соответствующим входам элемента ИЛИ, вЫходом соединенного с информациовным выходом устройства, второй вход. четвертого элемента H соединен с вторым выходом узла синхронизации и первым входом, узла формирования сигнала готовности, второй вход которого подключен к призначному выходу первого .узла памяти, третий вход †. к призначному выходу второго узла памяти, четвертый. вход †. к третьему выходу узла синхронизации и второму входу пятого элемента И, а выход является выходом сигнала готовности устройства, четвертый выход узла синхронизации соединен с синхронизирующим входом- второго узла памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 913359, кл.G 06 Г. 3/04, 1982 (прототип)., 966685

Составитель В.Вертлиб

Редантор Л.Авраменко Техред С .Мигунова Корректор С.Шекмар

Заказ 7845/66 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений .и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная,4