Преобразователь код-частота

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ .СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (u> 966890 л 1,,= .,/Г (61) Дополнительное к авт. свид-ву— (22) Заявлено 27. 03. 81(21) 3268223/ 18-21 (51)M Кл з с присоединением заявки ¹ (23) Приоритет-

Н 03 К 13/02

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 15.10.82, Бюллетень ¹ 38 (ЗЗ) УДК 681. 325, (088. 8) Дата опубликования описания 15.10.82 (72) Автор изобретения

В.Ф.Ким (71) Заявитель (54) ПРЕОБРАЗОВАТЕЛЬ КОД вЂ” ЧАСТОТА

Изобретение относится к вычислительной. технике и может быть использовано в устройствах, где необходимо линейное преобразование код-частота с возможностью управления начальной фазой выходного сигнапа.

Известен преобразователь код - частота следования импульсов, сдержащий две логические схемы И, инвертора, блок сравнения, генератор импульсов, управляемый делитель частоты, регистр кода числа, числовой регистр, дополнительный триггер управления,. три входные шины, шину сброса, счетчик обратных значений, блок считывания, суммирующий счетчик, второй блок сравнения, входную

Шину и и триггеров f1).

Данный преобразователь позволяет получить линейную зависимость между входным кодом и частотой следования выходных импульсов, но отличается высокой сложностью и в нем невозможно управление начальной фазой выходного сигнала.

Известен преобразователь код— частота, содержащий сумматор, и выходами подключенный к п первым входам через и-разрядный регистр, а выходом переноса - к выходу через формирующий блок, à и вторыми входами — к ходам преобразователя, причем стробирующие входы формирующего блока и и-разрядного регистра подключены к тактовому входу преобразователя f23., Этот преобразователь характеризуется простотой схемного решения, но функциональные возможности его ограничены, так как на нем невозможно осуществить управление начальной фазой выходного сигнала.

Целью изобретения является рас15 ширение функциональных воэможностей.

Поставленная цель достигается тем, что в.преобразователь кодчастота, содержащий сумматор, первы20 ми п входами подключенный к шине входного кода, вторыми и входами— к выходам регистра, а выходом переноса и- ãî разряда — к информационному входу выходного блока, такти25 руеьый вход которого соединен с тактируемым входом регистра и шиной тактирования, .дополнительно введен мультиплексор, первая группа входов которого подключена к соотЗ0 ветствующим выходам сумматора, вто9бб890 рая группа входов — к шине установки фазы, вход управления — к шине управления, а и выходов — к соответствующим входам .гистра.

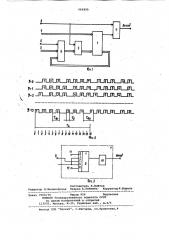

На фиг.1 приведена структурная схема преобразователя; на фиг.2 — 5 временные диаграммы, поясняющие его работу; на фиг.3 — структурная схема выходногб блока преобразователя.

Преобразователь содержит комби- . национный сучматор 1. Первые и входов сумматора 1 подключены к шине входного кода 2 преобразователя, а вторые и входов сумматора 1 — к выходам и-разрядного регистра 3, ин-. формационные вхОды которого подключены к выходам мультиплексора 4.

Мультиплексор 4 своими первыми и входами подключен к шине установки фазы 5 преобразователя, вторыми и входами — к выходам сумматора 1, а входом управления — к шине управления б преобразователя. Выход переноса n-ro разряда сумматора 1 подключен к информационному входу выход ного блока 7, тактируемый вход которого подключен к тактируемому входу регистра 3 и к шине тактирования 8 преобразователя. .Преобразователь работает следующим образом.

На шину 2 приложено двоичное чи- . ЗО сло F, а на шине 5 — число 9, на шине тактирования 8 действует им1 пульсный сигнал с частотой f о

íа шине б управления установлен 35 низкий потенциал, что свидетельствует о том, что мультиплексор передает на вход регистра 3 число 9 со входом 5. Так как тактируемые импульсы поступают непрерывно, то на выхо- .4р дах регистра 3 тоже устанавливается число Ф, а на выходе сумматора— число S> = Ф+ F.

С момента, когда по шине б управ- 45 ления установливается единица(высокий потенциал), мультиплексор

4 переключается на другие входы с выходов сумматора 1. При этом образуется замкнутое кольцо: мультиплексор 4, регистр 3 и сумматор 1. По мере поступления тактовых импульсов состояние выходов регистра 3 по каждому тактовому импульсу увеличивается на F до тех пор, пока величина

S на выходах сумматора 1 не превысит 2 -1. В этот момент на выходе переноса и-го разряда сумматора 1 образуется единица, а на остальных выходах S», -2" Г и т.д. В этом случае, если величина F не кратна 2, 60 исходное состояние в регистре 3 восстанавливается через 2 импульи сов, т.е. через 2 импульсов состояние выходов регистра 3 равно

Приняв за время цикла Т> прохожде- б5 ние 2 тактовых импульсов, можно определить количество импульсов, сформировавшихся на выходе переноса и-ro разряда, а следовательно, и среднюю частоту сформированной импульсной последовательности. Коли чество импульсов, очевидно, равно F, так как в числе F 2 " F определяет, сколько раз было превышено значение

2 -1, что тождественно появлению едии ницы перенос@..Время одного цикла

2 о

Тц = — а частота f = .„ -F

СР 2и о

Средний период последовательности импульсов с выхода переноса сумматора 1 Ь = т — не кратен в общем слу1

СР 7р чае бо . Фактическое значение периода в течение времени может принимать два значенйя Ч:,„и a+ отличающиеся ся друг от друга по длительности на

= т ф — ч Фри ближайшие по значению к ч.сР y < ср ф ) . Определенное количествб периодов т „ и за время цикла Т дает среднее значение периода не кратное о . Распределение в течение Т и позиционное положение Су и сф определяется, очевидно, значением 1 на шине установки фазы 5.

Сказанное можно проиллюстрировать на примере четырехраэрядного преобразователя для конкретного значения

F = 7. На основании вышеприведенных рассуждений на фиг.2 построены временные диаграммы последовательностей импульсов с выхода переноса и-ro разряда сумматора 1 для всех значений где щ порядковый номер тактового импульса после установки единицы на шине б управления.

Как видно из диаграмм, количество единиц совпадает с числом F.Êîëèчество Гф„равно 5, а ч- равно 2.

При детальном рассмотрении временных диаграмм можно сделать вывод,что .значение чиспа Р определяет количество тактов, участвующих,в опережении, по отношению к случаю, когда Ч = О.

Так, например, если пронумеровать каждый импульс, соответствующий единице на выходе переноса n-ro разряда сумматора 1 таким образом, чтобы первому соответствовал импульс с минимальным значением m, как показано на фиг.2, то видно, что между последовательностями при 9 =О и Ф = 1 сдвигу на один такт соответствует импульс под номером 4, а дпя „ Р = 15 первый, второй и третий импульсы сдвинуты на два такта, четвертый импульс — на три такта;; пятый, шестой и седьмой импульсы — на два такта, а в целом общий сдвиг составляет 15 тактов. Таким образом, можно утверждать, 9FI6890 что число P соответствует количеству сдвигов в последовательности относительно. F = О. Можно, исходя из приведенных рассуждений, определить сдвиг за один цикл, приходящийся на один импульс

ФГо ср сдв

Выходной блок 7 предназначен для преобразования сформированного потока импульсов с выхода переноса сумматора 1 в необходимую форму сигнала. В простейшем случае это может быть схема (см.фиг.3), работающая в режиме центрирования процесса с последующей его фильтрацией. В этой схеме триг- !5 гер 9 работает в счетном режиме и при этом на его выходе имеем последовательность аналогичную клиппированному синусоидальному сигналу, прошедшему через устройство дискретиза- 20 ции с частотой дискретизации Ед.

Период следования импульсов с выхода триггера 9 равен }о 2 т = О

F -25

Формула изобретения

Для выделения основной гармоники сигнала на выходе триггера 9 установлен узкополосный фильтр 10 с достаточно большой постоянной времени

При измененииЧ: рс впо выходу фильтра

10 происходит изменение фазового сдвига. Значение фазового сдвига может быть определено из выражения

Рл 35

2и

45 Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 677095, кл. Н 03. К 13/02, 1979.

Из этого выражения видно, что дискретность изменения фазового сдвига в пределах C определяется разрядностью преобразователя и и равна—

ZVl

Для случая, когда величина числа

} . на входе 5 кратна 2, где k< n к дискретность изменения фазового к сдвига увеличивается в 2 раз и равх на ч „

2 о

Переключение фазы на 180 производится путем предварительной устаЙорики триггера 9 по входам 11 или

12.

Дискретность установки фазы определяется не только разрядностью преобразователя, но и схемой выходного блока 7.

Таким образом, частота пропорциоьна коду,, установленному на входах 2, при этом дискретность установки частоты составляет, onpef деляется разрядностью преобразователя .

Одновременно в преобразователе обеспечивается управление фазой выходного сигнала, причем усредненная фаза сигнала пропорциональна коду, установленному на входах 5 преобразователя, при этом дискретность установки определяется тоже разрядностью преобразователя.

Преобразователь код - частота, содержащий сумматор, первыми и входами подключенный к шине входного кода, вторыми и входами — к выходам регистра, а выходом переноса и-го разряда — к информационному входу выходного блока, тактируемый вход которого соединен с тактируемым входом регистра и шиной тактирования, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен мультиплексор, первая группа входов которого подключена к соответствующим выходам сумматора, вторая группа входов - к шине установки фазы. вход управления - к шине управления, а и выходов - к соответствующим.входам регистра.

2. Авторское свидетельство СССР по заявке Р 2820488/18-24, кл. Н 03 К 13/02.

966890

Ьп.1 зф 1 2 Л 4 Ю в 7 1 2

0 5 6 7 2

2 3

У=2

7=a

s s 5 s s v j s rs r rf rs t4 rs rs

Фг.у

Заказ 7900/76 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная,4

Составитель В.Войтов

Редактор Л.Веселовская Техред A.Áàáèíåss, Корректорй. ороль