Устройство приема дискретных однополосных сигналов

Иллюстрации

Показать всеРеферат

В. В. Державина, Б. П. Калмыков, В. В. Королева и С.И.Лопатин (72) Авторы изобретения (7!) Заявитель

Ленинградский электротехнический институ связи"::. им. проф.М.А.Бонч-Бруевича (54) УСТРОЙСТВО ПРИЕМА ДИСКРЕТНЫХ

ОДНОПОЛОСНЫХ СИГНАЛОВ

Изобретение относится к электросвязи и может быть использовано в устройствах для высокоскоростной пе редачи данных.

Известно устройство приема дискретных однополосных сигналов, содержащее последовательно соединенные приемник с автоматической регулировкой усиления, первый перемножитель, первый фильтр, первый стробирующий блок, а также регулируемый формирователь опорных сигналов, регулируе-. мый формирователь тактовых сигнал ов, линейный корректор, решающий блок и блок вычисления ошибок, причем первый выход регулируемого формирователя опорных сигналов соединен с вторым входом первого перемножителя, первый выход регулируемого форми рователя тактовых сигналов соединен с вторым входом первого стробирующего блока, вход блока вычисления ошибок соединен с входом решающего. блока, выход которого соединен с вторым входом блока вычисления ошибок, выход блока вычисления ошибок соединен с первым входом линейного корректора (1 J.

Однако в данном устройстве не обеспечивается согласованная фильтрация после однополосной демодуляции, а также невозможно исполь1О зование линейных методов коррекции при наличии амплитудно-частотных искажений в канале связи, что не позволяет достигнуть потенциальной помехоустойчивости приема.

Целью изобретения является повышение помехоустойчивости.

Поставленная цель достигается тем, что в устройство приема дискретных однополосных сигналов, содержащее последовательно соединенные приемник с автоматической регулировкой усиления, первый перемножитель, первый фильтр, первый стробируюший

3 96692 блок, а также регулируемый формиро ватель опорных сигналов,. регулируемый формирователь тактовых сигналов, линейный корректор, решающий блок и блок вычисления ршибок, причем первый выход регулируемого формирователя опорных сигналов соединен с вторым входом первого перемножителя, первый выход регулируемого Формирователя тактовых сигналов соединен с вторым входом первого стробирующего блока, вход блока вы числения ошибок соединен с входом решающего блока, выход которого соединен с вторым входом бцока вычисления ошибок, выход блока вычисления ошибок соединен с первым входом линейного корректора, введены последовательно соединенные второй перемножитель и первый сумматор, после- щ довательно соединенные третий перемножитель, второй фильтр, второй стробирующий блок и четвертый перемножитель, а также второй сумматор, нелинейный корректор, декодер, при- 25 чем выход первого стробирующего блока соединен с первым входом второго перемножителя, второй вход которого соединен с вторым выходом регулируемого формирователя тактовых сигналов, выход первого сумматора соединен со вторым входом линейного корректора, первый выход которого соединен с первым входом регулируемого формирователя опорных сигналов, второй выход регулируемого формирователя опорных сигналов соединен с вторым входом. третьего перемножителя, первый вход которого соединен с выходом приемника с автоматической регулировкой усиления, выход первого фильтра соединен с первым входом регулируемого Формирователя тактовых сигналов, второй вход которого соединен с выходом второго фильтра, а третий выход которого соединен с вторым входом второго стробирующего блока, четвертый выход регулируемого Формирователя тактовых сигналов соединен с вторым входом четвертого перемножителя, выход которого соединен с вторым входом первого сумматора,второй выход линейного корректора соединен с первым входом второго сумматора, выход которого соединен с входом решающего блока, второй вход второго сумматора соединен с вторым выходом нелинейного корректора,первый вход нелинейного корректора соединен с выходом решающего блока,второй его вход соединен с выходом блока вычисления ошибок, а первый выход нелинейного корректора соединен со вторым входом регулируемого формирователя опорных сигналов, выход решающего блока соединен с входом декодера, выход которого соединен с третьим входом регулируемого формирователя тактовых сигналов.

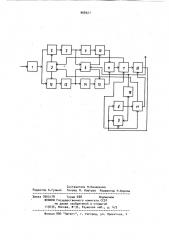

На чертеже представлена принципиальная электрическая схема предложенного устройства.

Устройство приема дискретных однополосных сигналов содержит приемник 1 с автоматической регулировкой усиления, первый перемножитель 2, первый фильтр 3, первый стробирующий блок 4, регулируемый формирователь опорных сигналов 5, регулируемый формирователь тактовых сигналов 6, линейный корректор 7, решающий блок

8, блок 9 вычисления ошибок, второй перемножитель 10, первый сумматор 11, третий перемножитель 12, второй

Фильтр 13, второй стробирующий блок

14, четвертый перемножитель 15,второй сумматор 16, нелинейный корректор

17, декодер 18.

Устройство работает следующим образом.

Принятый сигнал поступает на вход приемника 1 с автоматической регулировкой усиления и направляется в два подканала (синфазный и квадра турный ), где перемножаются в первом перемножителе. 2 и третьем перемножителе 12 с сигналом регулируемого формирователя опорных сигналов 5. Далее сигналы синфазного и квадратурного подканалов фильтруются первым 3 и вторым 13 Фильтрами и стробируются первым 4 и вторым 14 стробирующими блоками, после чего перемножаются с сигналами регулируемого Формирователями тактовых сигналов во втором

10 и четвертом 15 перемножителях.

С переносом спектра сигналов в рабочую полосу частый полученный сиг1 нал суммируется в первом сумматоре

11 и поступает в линейный корректор

7, далее через второй сумматор 16 на решающий блок 8, в который выносится поэлементное решение принятого символа. Затем, проходя через нелинейный корректор 17, сигнал подается на другой вход второго сумматора 16.

После решающего блока 8 сигнал де5 9669 кодируется в декодере 18 и поступает на выход устройства.

Одновременно с описанными процес-. сами сигналы с входа и выхода ренающего блока 8 поступают в блок 9 вычисления ошибок, предназначенный для управления линейного 7 и нелиней- ного 17 корректоров, сигналы с выходов которых поступают одновременно на вход регулируемого формировате- 10 ля опорных сигналов 5. Для получения сигнала подстройки фазы регулируемого формирователя тактовых сигналов 6 используются декодированные сигналы с выхода декодера 18 и сигналы с ts выходов первого 3 и второго 13 фильтров.

Таким образом,использоание предложенного изобретения позволяет снизить вероятность ошибки не менее, чем на 2 порядка, увеличивая таким образом эффективность средств связи.

Формула изобретения

2S

Устройство приема дискретных однополосных сигналов, содержащее последовательно соединенные приемник с автоматической регулировкой усиления, первый перемножитель, первый фильтр, первый стробирующий блок, а также регулируемый формирователь опорных сигналов, регулируемый фор- мирователь тактовых сигналов, линей-. ный корректор, решающий блок и блок .вычисления ошибок, причем первый выход регулируемого формирователя опорных сигналов соединен с вторым входом первого перемножителя, первыи выход регулируемого формирователя тактовых сигналов соединен с вторым входом первого стробирующего блока, вход блока вычисления ошибок соединен с входом решающего блока, выход которого соединен с вторым входом блока вычисления ошибок, выход блока вычисления ошибок соединен с первым входом линейного корректора, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные второй перемножитель и первый сумматор, последовательно соединенные третий перемножитель, 21 б второй фильтр, второй ст роби рующий блок и четвертый перемножитель, а также второй сумматор, нелинейный корректор, декодер, причем выход первого стробирующего блока соединен с первым входом второго перемножителя, второй вход которого соединен с вторым выходом регулируемого формирователя тактовых сигналов, выход первого сумматора соединен с вторым входом линейного корректора, первый выход которого соединен с первым входом регулируемого формирователя опорных сигналов, вто рой выход регулируемого формирова- . теля опорных сигналов соединен с вторым входом третьего перемножителя, первый вход которого соединен с выходом приемника с автоматической регулировкой усиления, выход первого фильтра соединен с первым входом регулируемого формирователя тактовых сигналов, второй вход которого соединен с выходом второго фильтра, а третий выход которого соединен с вторым входом второго стробирующего блока, четвертый выход регулируемого формирователя тактовых сигналов соединен с вторым входом четвертого перемножителя, выход которого соединен с вторым входом первого сумматора, второй выход линейного корректора соединен с первым входом второго.сумматора, выход которого соединен с входом решающего блока, а второй вход второго сумматора соединей с вторым. выходом нелинейного корректора, первый вход нелинейного корректора, первый вход нелинейного корректора соединен с выходом решающего блока, второй его вход соединен с выходом блока вы,числения ошибок, а первый выход нелинейного корректора соединен с вторым входом регулируемого формирователя опорных сигналов, выход решающего блока соединен с входом декодера, выход которого соединен с третьим входом регулируемого формировате- ля тактовых сигналов.

Источники. информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке и 256058ч/09, кл. H 04 t. 25/40, 29.06.79 (прототип).

966921

Составитель М.Овчаренко

Редактор А. Гулько Техред И. Коштура Корректор Н. Король

Заказ 7903/?8 . Тираж 688 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4