Устройство измерения фазы

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

«i>968767 (61) Дополнительное к авт. свид-ву Р 551571

{22) Заявлено 060481 (21) 3270201/18-21 (gqjМ К 1 3

G 01 R 25/00 с присоединением заявки №Государстаеииый комитет

СССР ио делам изобретеиий и открытий (23) Приоритет—

Опубликовано 23.1082. Бюллетень ¹ 39 (53) УДК 621. 317. 77 (088. 8) Дата опубликования описания 23. 10. 82 (72) Авторы изобретения

A.Ä.ÏîäëèíHîâ, В.В.Шкирятов и Е.М.Заводий

J (71) Заявитель (54) УСТРОЙСТВО ИЗМЕРЕНИЯ ФАЗЫ

Изобретение относится к радиоизмерительной технике, к системам аналого-цифровой обработки сигналов, в частности к цифровым измерителям фазы.

Io ocHo HoM T. . 9 551571 известно устройство измерения, фазы с нониусным методом оценок фазовых соотношений, содержащее блок свертки первый вход которого и один.из входов дискриминатора задержки подключены к первому входу устройства,выход блока свертки через блок гетеродинирования измеряемого сигнала соединен с первым входом фазового дискриминатора, блок поиска H выделений

"модулирующей" и "несущей" опорного сигнала, вход которого соединен с вторым входом устройства, один из выходов через дискриминатор задерж- ки, аналого-цифровой преобразователь грубой шкалы, счетчик грубой шкалы и сумматор соединен с регистром выходной информации, а второй выход подключен к второму входу блока свертки и через блок гетеродинирования опорного сйгйала соединен с вторым вхо-. дом фазового дискриминатора, выход которого через элемент ИЛИ,аналогоцифровой преобразователь точной шкалы, счетчик точной шкалы соединен с вторым входом регистра выходной информации, генератор пониженной . частоты, выход которого подключен соответственно к вторым входам блоков гетеродинирования измеряемого и опорного сигналов, блок сравнения, сое" диненный по входам с вторыми выходами счетчиков грубой и точной шкал, а по выходу — c вторым входом сумма;тора, элемент совпадения, входы которого соединены соответственно с вторым выходом фазового дискриминато:ра, с входом блока задержки и, одним иэ входов формирователя времейного интервала, выход которого подключен к второму входу элемента ИЛИ, второй вход формирователя временного интервала соединен с выходом блока задержки, выход элемента совпадения подклю чен к третьему входу формирователя временного интервала, первый вход которого и вход блока задержки соединены с соответствующими входами элемента совпадения.

Недостатком такого устройства является то, что при увеличении флуктуаций возможна "ложная стыковка" показаний грубой и точной шкал в блоке сравнения, что является причиной

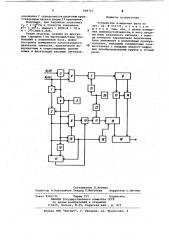

968767 дискриминатор б задержки, аналогоцифровой преобразователь 7 грубой шкалы, счетчик 8 грубой шкалы, фазовый дискриминатор 9, элемент 10

ИЛИ, аналого-цифровой преобраэовател

11 точной шкаЛы, счетчик 12 точной шкалы, блок 13 сравнения, сумматор

14, элемент 15 совпадения, блок 16 задержки, формирователь 17 временногс интервала, регистр 18 поправки и . регистр 19 выходной информации.

Блок 20 эталонного сигнала соединен по выходу с умножителем 21 и масштабным преобразователем 22. Выход умножителя 21 соединен с преобразователем 7 грубой шкалы, а выход масштабного преобразователя 22 соеди-. нен с преобразователем 11 точной.

Устройство работает следующим образом.

Для повышения помехоустойчивости сигналы заполнения (F, Г - ) преобразователей 7 и 11 вырабатываются от одного источника блока эталонного сигнала 20 путем умножения его на коэффициент е = 2", где. м — число

"избыточных" разрядов счетчика 8 грубой шкалы. При этом сигнал с выхода блока 20 эталонного сигнала (Гз) умножается в умножителе 21 на коэфсит от уровня помех в канале измерения и быстродействия применяемых логических элементов преобразователя 7 шкалы. В преобразователе 7 грубой шкалы сформированный дискриминатором б задержки временной интервал заполняется частотой заполнения (Ггщ ). и в двоичном коде хранится на каждом цикле измерения в счетчике 8 грубой шкалы. Благодаря когерентным преобразователям сигнала Е в блок 13 сравнения на логический анализ подключаетсить достоверность стыковки отсчетов по грубой шкале с измерениями по точной шкале.

Измерения по точной шкале также формируются путем заполнения временного интервала с выхода фазового дискриминатора 9 в преобразователе 1 точной шкалы сигналом F g, полученного от б пока 20 эталонного сигнала и умноженного масштабным преобразователем

22 на коэффициент M:

2и тШ M.ГЭ Ъ fbi где М вЂ” количество разрядов счетчика 12 точной шкалы;

И вЂ” коэффициент гетеродинирования входных сигналов.

Значения коэффициента гетеродинирования и количество разрядов счетчика 12 точной шкалы определяется заданной точностью измерений, а преобнизкой помехоустойчивости устройства в целом.

Целью изобретения является повышение помехоустойчивости.

Поставленная цель достигается .тем, что в устройство измерения фа- 5 эы, содержащее блок свертки, первый вход которого и один из входов дискриминатора задержки подключены к первому .входу устройства, евыход бло- ка свертки через блок гетеродини- . g, рования измеряемого сигнала соединен с первым входом фазового дискриминатора, блок поиска и выделения "модулирующей" и "несущей" опорного сигнала, вход которого сОединен с вторым1 входом устройства, один из выходов через дискриминатор задержки, анало" го-цифровой преобразователь грубой шкалы. шкалы,- счетчик грубой шкалы и сумматор соединен с регистром выходной информацис, а второй выход подключен к второму входу блока свертки и через блок гетеродинирования опорного сигнала соединен с вторым входом фазового дискриминатора, выходкоторого через элемент ИЛИ,аналогоцйфровой преобразователь точной шка лы, счетчик точной шкалы соединен с вторым входом регистра выходной информации, генератор пониженной частоты, выход которого .подключен со- З0 фициент т., величина которого завиответственно к вторым входам блоков гетеродинирования измеряемого и опорного сигналов, блок сравнения,соеди- ненный по входам с вторыми выходами . грубой шкалы и счетчика 8 грубой счетчиков грубой и точной шкал, .а по 35 выходу - с вторым входом сумматора, элемент совпадения, входы которого соединены соответственно с вторым выходом фазового дискриминатора, с входом блока задержки и одним из входов 40 формирователя временного интервала, выход которого подключен к второму входу элемента ИЛИ, второй вход фор- : мирователя. временного интервала сое- ся и разрядов, что позволяет повы. динен.с выходом блока задержки, выход45 элемента совпадения подключен к тре тьему входу Формирователя временногс интервала, первый вход которого и вход блока задержки соединены с соот.ветствующими входами элемента совпадения, введены блок эталонного сигнала, к выходу которого параллельно подключены блок умножения .и масштабный:преобразователь, выходами соединенные соответственно с входами ана"

;луго-цифровых преобразователей грубой15 и1точной шкал.

Йа чертеже приведена схема предлагаемого устройства.

Устройство измерейия фазы содержит блок 1 свертки, блок 2 гетероди- 60 нирования измеряемого сигнала, блок

3 поиска и выделения "модулирующей" и "несущей" опорного сигнала, блок 4 гетеродинирования опорного сигнала, генератор 5 пониженной частоты, 968767

Формула изобретения.

Составитель Н.Areesa

Редактор И.Николайчук.Техред:С.Мигунова Корректор С.Мекмар.

Заказ 8162/75 Тираж 717 Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, 3-35, Раушская наб., д. 4/5

Филвал ППП "Патент", r. Ужгород, ул. Проектная, 4 разования К определяетсядвончным представлением чисел в блоке 13 сравнения.

Например, при заданных значениях

f = 1 10 Гц и точности измерения а4 1 10 с, имеем k = 1000,й = 10 н

М = 21О/1000=1,024.

Таким образом, исходя из доступных (средних ) по быстродействию требований к элементной базе, можно построить измерители наносекундного диапазона точности, практически инвариантные к существующему уровню помех и флуктуаций входных сигналов. устройство измерения фазы по авт. св. Ю 551571, о т л н ч а ющ е е с я тем, что, с целью повышения помехоустойчивости, в него введены блок эталонного сигнала, к выходу которого параллельно подключены блок умножения и масштабный преобразователь, выходами соединенные соответственно с входами аналого-цифровых преобразователей грубой и точной

IOK cUl