Устройство для параллельного счета количества единиц (нулей) в двоичном числе

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (ii) 96880 I (61) Дополнительное к авт.,саид-вуР 450160 (22) Заявлено 190581 (21) 3287416/18-24

{51}М Кл з

G 06 F 5/02 с присоединением заявки ¹ (23) Приоритет

Государственный комитет

СССР по делам изобретений н открытий

Опубликовано 2Ы082 Бюллетень ¹ 39

{53) УДК 681. 325 ° ..53 (088.8) Дата опубликования описания2ЮЫ2 (72) Авторы изобретения

В.В. Павличенко и М.И. Гольцов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО СЧЕТА КОЛИЧЕСТВА

ЕДИНИЦ (НУЛЕЙ) В ДВОИЧНОМ ЧИСЛЕ

Изобретение относится к вычислительной технике и может быть применено в системе защиты от ошибок двоичной информации, передаваемой между отдельными дискретными блоками вычислительных машин.

По основному авт.св. в 450160 известно устройство для параллельного счета количества единиц (нулей) в двоичном числе, содержащий и-разрядный входной регистр, входной регистр, Log>n груйй сумматоров, по п/2k сумматоров в каждой. группе (1 < к < Iog n), причем выход суммы последнего сумматора каждой группы и выход переноса сумматора пос" ледней К-ой группы соединены с входами соответствующих разрядов каждого регистра, входы каждого i-го сумматора К.-ой группы соединены с выходами переноса 2 i-го и (2 i-1) -го

"сумматоров (К-1)-ой группы и,с выходом суммы (i-1)-го сумматора К-ой группы, выходы 2 i-ro и (2 i-1)-го разрядов входного регистра соединены с входами 1-го сумматора первой группы. (1 ) .

Недостаток известного устройства состоит в его ограниченных функциональных возможностях. Этот недостаток обусловлен тем, что устройство выполняет только функции параллельного двоичного счетчика.

5 Целью изобретения является расширение функциональных воэможностей устройства за счет.преобразования исходного кода в помехоэащищенный эквивалентный код Бергера . Кодовое слово эквивалентного кода

Бергера включает в себя информационную часть и проверочную. Информационная часть представляет собой исходное и-разрядное двоичное слово, I5 а проверочная — двоичное число К равное. числу нулей в исходном двоичном слове, если старший разряд в нем имеет единичное значение, или двоичное число суммы двух чисел К„ и Ко, если старший разряд в исходном двоичном слове имеет нулевое значений. К в этом случае - также число нулей в исходном двоичном слове, а К1 = (2 - 1)-п,где имеет целое значение

25 такое, что выполняется условие:

min (2 - 1) у и

Указанная цель достигается тем, что устройство для параллельного счета количества единиц (нулей) в двоичном числе дополнительно содер968801

55 бО

65 жит элемент И, входы которого соединены с выходом старшего разряда входного регистра и управляющей шиной устройства, а выход подключен к третьим входам первых сумматоров тех групп, номера которых соответст вуют номерам единичных разрядов двоичного представления числа К (K> (2 — 1)-n; q — целое число;

min (2 — 1) )r и, (n - разрядность исходного числа).

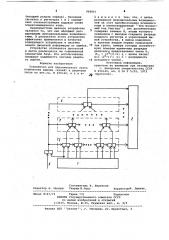

На чертеже представлена функциональная схема устройства.

Устройство содержит и-разрядный входной регистр 1, выходной регистр

2, сумматоры 3, соединенные в группы 4, 5, б, элемент И 7,. Управляющую шину S.

Устройство имеет следующую структуру связей: инверсные выходы 2 i-го и (2 1-1)-ro разрядов входного регистра 1 соединены с входами i"гО сумматора 3 первой группы 4 (i

1,...,n/2). В последующих группах.

5, б, 7 входы каждого j-ro суммато- ., ра 3 К-ой группы (К = 1,2,...eIogZn) соединены с выходами переноса 2 j-го и (2 ) -1)-ro сумматоров 3 (К-1)-ой группы и с выходом. суммы ()-1)-го сумматора 3 К-ой группы (j = 1,..., log>n-К) . Выход суммы последнего сумматора 3 каждой группы .(нумерация слева направо) и выход переноса сумматора 3 последней группы 6 соеди" иены со входами соответствующих разрядов выходного регистра 2. Первый вход элемента И 7 соединен с выходом старшего разряда входного регистра 1 (старший разряд регистра

1 находится слева), второй — с управляющей шиной 8, а выход соединен с третьим входом первого сумматора 3 соответствующих групп 4,5,6 сумматоров 3.

Подключение третьего входа первого сумматора 3 К-ой группы.к выходу элемента И 7 осуществляется в том случае, если сопоставленный этой группе 1-ый разряд двоичного числа К2 имеет значение, 1 . Младший разряд двоичного числа К сопоставляется первой группе 4 сумматоров 3, остальные разряды сопос.тавляются другим группам сумматоров

3 в соответствии с естественным возрастанием порядкового номера.

Входной регистр 1 предназначен для приема и хранения исходного двоичного слова.

Выходной регистр ? предназначен для хранения результата преобразования в двоичном коде.

Группы 4, 5, 6 сумматоров 3 представляют собой параллельный двоичный счетчик, который также осуществляет формирование проверочных разрядов кодового слова помехозащищенного кода.

Элемент И и шина 8 предназначены для задания режима работы устройства.

Устройство работает в двух режимах.

В первом этом режиме устройство осуществляет подсчет числа нулей в исходном двоичном слове,. записанном во входной регистр 1, Для задания этого. режима работы устройства на второй вход элемента И 7 подается по.шине 8 потенциальный сигнал с значением " 0 ° В этом случае на третьем входе первого сумматора 3 каждой группы 4, 5, б присутствует сигнал с значением 0 . Такое исходное состояние вышеописанных элементов обеспечивает первый режим работы устройства.

Второй режим работы устройства позволяет осуществлять преобразование исходного двоичного слова в кодовое слово помехозащищенного кода.

В этом режиме устройство осуществляется формирование сигналов проверочных. разрядов соответствующего кодового слова, которые записываются в выходной .регистр 2.

Для задания второго режима работы устройства на второй вход элемента

И 7 подается по шине 8 потенциальный сигнал с значением 1 . В этом режиме работы устройства значение сигнала на выходе элемента И 7 определяется значением сигнала старшего разряда входного регистра 1., Работу устройства во втором режиме функционирования рассмотрим на конкретном примере при преобразовании восьмиразрядных (n = 8) двоичных слов в кодовые слова помехозащищенного кода.

Конструкция устройства в этом случае соответствует, структуре,изображенной на чертеже без учета разрывов в связях.

Для рассматриваемого варианта третий вход первого сумматора 3 каждой группы 4, 5, б подключен к выходу элемента И 7, так как число К =7 в двоичном коде имеет вид 1 1 1.

Значение К =7 определено по формуле

К = (2@ — 1)-8 где q = 4, что сле 1 I () 1 дует из,условия: min (2 -1) 7r 8.

Пусть в регистре 1 записано слово 00111111 (старший разряд находится слева). На третий вход первого сумматора 3 каждой из групп 4, 5, 6 поступает сиГнал с значением 1 .

На первый и второй входы первого сумматора 3 первой группы 4 поступают сигналы с значением 1 . На первый и второй входы остальных сумматоров 3 первой группы 4 поступают сигналы 0 . В результате преобразования в регистр 2 записываются сигналы проверочных разрядов, определяемые двоичным словом 1001

968801

Составитель В. Березкин

Редактор A. Шандор Техред М. Надь Корректор М. Демчик

Заказ 8167/76 Тираж 731 Подписное

ВНИИПИ Государственного. комитета СССР

IIo делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

« l «»

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 (младший разряд справа) . Значения сигналов в регистрах 1 и 2 определяют соответствующее кодовое слово помехозащищенного кода.

Преимуществом данного устройства является то, что оно обладает расширенными функциональными возможностями. В результате этого устройство эффективно применяется в качестве кодирующего устройства в системе защиты двоичной информации от ошибок.

Устройство отличается простотой и легко. реализуется на современной элементной базе.. Его использование повышает надежность системы защиты от ошибок.

Формула изобретения

Устройство для параллельного счета количества единиц (нулей) в двоичном числе по авт.св. Р 450160, о т л ич а ю щ е е.с я тем, что, с целью расширения функциональных возможностей за счет преобразования исходного кода в помехозащищенный экв валент,ный код Feprepa, оно дополнительно содержит элемент Й, входы которого соединены с выходом старшего разряда входного регистра и управляющей шиной устройства, а выход подключен к третьим входам первых сумматоров

10 тех групп, номера которых соответствуют номерам единичных разрядов двоичного представления числа К . (К > = 2 "-1) -n, с - целое число;

min (-2 -1) n; n — разрядность

) 5 исходного числа) .

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство, СССР .

9,450160, кл. G 06 F 5/02, 1972

4 (прототип).