Модель нейронной сети

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву(22).Заявлено 20. 10; 80 (21) 2995952/18-24 }5< } М. Кл.З с присоединением заявки ¹ " (23) Приоритет "

С 06 G 7/60

Государственный комитет

СССР ио делам изобретений и открытий

Опубликовано 2310.82 ° Бюллетень ¹ 39 (53} УДК 681. 333 (088. 8) Дата опубликования описания 23.10.82

1н с т\дтдг т д .;

1 (72) Автор изобретения

ТЮХТИ ЕСИц

ЙВЯЗК}ТОЩ

С. A. Попов (71) заявитель (54) МОДЕЛЬ НЕЙРОННОЙ СЕТИ

Изобретение относится к моделированию нервной системы и может быть использовано в исследованиях нервной системы как запоминающего устройства и как устройства, перерабатывающего информацию. устройства, моделирующие нейронные сети, обладающие ассоциативной памятью, известны. Любое ассоциативное запоминающее устройство можно считать одним из таких устройств, моделирующим нейронную сеть как.минимум с функциональной, феноменологической стороны. Особый интерес для неврологии представляют такие устройства, которые построены иэ технических аналогов нервных клеток моделей нейронов.

Известна нейронная сеть L 1).

Однако эта многослойная сеть древовидная. Так, если число информационных входов в сети равно и, то число моделей нейронов первого слоя . должно быть равно или больше и, второго слоя - равно или больше п 2, третьего - n и т.д..Т.е. имеется степенная зависимость количества ней ронов от количества слоев сети.

Наиболее близкой к изобретению является модель нейронной сети, содержащая модели нейронов, каждая из которых состоит из триггера, нулевой вход которого подключен к входу сброса модели нейрона, единичный вход триггера соединен с выходом первого элемента И, входы которого подключены к входам элемента ИЛИ и соединены с информационным входом и выходом

10 записи - считывания модели нейрона соответственно, выход элемента ИЛИ подключен к первому входу второго элемента И, второй вход которого соединен с единичным выходом триггера, выход второго элемента И подключен к входу генератора. импульса, выход которого является выходом модели нейрона, модели многовходовых нейронов, каждая иэ которых состоит из сумматора, пряьые входы которого соединены с выходами модели многовходового нейрона, тормозящий вход которого подключен к инверсному входу сумматора, выход которого соединен с входом порогового элемента, выход кото25 рого подключен к генератору импульса, выход которого является выходом модели многовходового нейрона, управляющий вход порогового элемента соединен с входом регулирования по30 рога срабатывания модели многонхолс-

Эб8827

4 вого нейрона, и .модели тормозящих нейронов, каждая из которых состоит из генератора импульса, выход которого через инвертор подключен к выходу. модели тормозящего нейрона 1.2).

Иедостатком известного решения 5 является то, что в устройствах с. большим числом моделей нейронов в строке число элементов связи, т.е.

"запоМинающих входов" оказывается столь велико, что изготовление уст- 10 ройства становится затруднительным, Цель изобретения - упрощение модели ..

Укаэанная цель достигается тем, что в модели нейронной сети, содер-. жащей модели нейронов, каждая из которых состоит из триггера, нулевой вход которого подключен к входу сброса модели нейрона, единичный вход триггера соединен с выходом первого элемента И, входы которого подключены к входам элемента ИЛИ и соединены с информационным входом и входом записи — считывания модели нейрона соответственно, выход элемента ИЛИ

25 подключен к первому входу второго элемента И, второй вход которого соединен с единичным выходом триггера, выход второго элемента И подключен к входу генератора импульса, выход которого является выходом модели нейрона, модели многовходовых нейронов, каждая иэ которых состоит иэ сумматора, прямые входы которого соединены с входами модели многовходо- 3S вого нейрона, тормозящий вход которой подключен к инверсному входу сумматора, выход которого соединен с входом порогового элемента, выход которого подключен к генератору. импуль-4р са, выход которого является выходом модели многовходового нейрона, управляющий вход порогового элемента соединен с входом регулирования порога срабатывания модели многовходового нейрона, и модели тормозящих нейтронов,, каждая иэ которых состоит из генератора импульса, выход которого через инвертор подключен к выходу модели тормозящего нейрона, модели нейронов образуют матрицу п х щ, причем входы сброса моделей нейронов каждой i-1 (i = l, 2, ... „ и) строки подключены к i-ому разряду п разрядной шины сброса, каждый i-й разряд п разрядной шины записи — считывания соединен с входами записи — считывания моделей нейронов i-й, строки ичерез i-ю модель тормозящего нейрона с тормозящим вхо дом 1-й модели многовходового нейрона, выход которого подключен к (i+1)- 60 ому разряду шины записи — считывания, j -й (j = 1, 2, ..., m) разряд входной информационной шины соединен с информационными входами моделей нейронов

i-oro столбца, выходы которых подклю- 6g чены к j -ому разряду выходной информа-1 ционнойшины, выходымоделей нейронов

i-й строки соединены с соответствующими входами -й моделй многовходового нейтрона, вход регулирования порога срабатывания нейрона соединен с

i ""ым разрядом и-разрядной шины регулирования порога срабатывания.

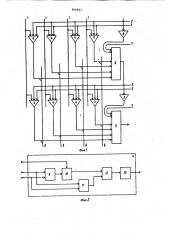

На фиг. 1 приведена структура модели нейронной сети; на фиг. 2 — структура модели нейрона; на фиг. 3 структура модели тормозящегo нейрона; на фиг. 4 — структурй многовходового нейрона.

Модель нейронной сети (фиг. 1) содержит входную разрядную информационную шину 1, п разрядную шину 2 записи — считывания, и разрядную шину

3 сброса, модели нейронов 4, модели . тормозящих нейронов 5, модели многовходовых нейронов 6, п разрядную шину 7 регулирования порога срабатывания и m разрядную выходную информационную шину 8.

Модель нейрона 4 (фиг . 2) содержит первый элемент И 9, триггер 10, элемент ИЛИ 11, второй элемент И 12 и генератор 13 импульса.

Модель тормозящего нейрона 5 (фиг. 3) содержит генератор 14 импульса и инвертор 15.

Модель .многовходового нейрона б (фиг..4) содержит сумматор 1б, поро- говый элемент 17 и генератор 18 импульса.

Модель работает следующим образом.

Запись информации. На входы соединенные с информационными входами моделей нейронов 4, поступает какоенибудь число в прямом и в обратном коде одновременно (например комбинация 0110, соответствующая числу 01).

На шину записи - считывания свободной ячейки (первой строки, например, первой ячейки) поступает сигнал записи от коммутатора (не показан).

В первой ячейке в состояние "1" переводятся элементы памяти второй и третьей модели нейрона 4. В дальнейшем модель нейрона, триггер которой перешел в состояние "1", вырабатывает сигнал как в том случае, когда сигнал поступает на ее информационный вход, так и в том случае, когда сигнал поступает на вход, соединенный с шиной 2 записи - считывания.

Пусть в первой ячейке заПисано двоичное число 01, т.е. записано

0110, а во второй двоичное. число 10 в прямом и в обратном коде, т.е.

1001.

Если теперь на информационные входы устройства поступает двоичное. число 01 в прямом и в обратном коде, т.е. 0110, то пусть оно записывается в очередную свободную ячейку. Одно968827

Формула изобретения временно возбуждается вторая и третья модели нейронов 4 в первой ячейке. Во второй ячейке не возбуждается ни одна иэ моделей нейронов 4.

Если порог возбуждения (срабаты. вания) модели нейрона 6 установлен таким, что она возбуждается при отсутствии сигнала на ее тормозящем входе и при наличии сигналов на 5ОВ ее.входов, соединенных с выходами моделей нейронов, эта модель возбуж- 10 дается в первой ячейке и посылает сигнал в шину "запись - считывание" второй ячейки. В результате воэбужда1отся первая и четвертая модели ней-рона 1 во второй ячейке. На выходах 15 сети вслед эа комбинацией 0110 с некоторой задержкой появляется комбинация сигналов 1001. Модель нейрона второй ячейки при этом не возбуждается, так как на ее тормозящем вхо" gp де будет сигнал с выхода модели тормозящего нейрона 5 второй ячейки.

Таким же образом при участии модели тормозящего нейрона предотвращается возбуждение модели нейрона той ячейки, в которую записывается информация.

Таким образом, благодаря .введен. ным связям между моделями нейронов резко упрощается модель нейронной . сетй,:, обладающей ассоциативной памятью.

Модель нейронной сети, содержащая модели нейронов, каждая из которых состоит иэ триггера, нулевой вход которого подключен к входу сброса модели нейрона, единичный вход тригге- 40 ра соединен с выходом первого элемента И, входы которого подключены к входам элемента ИЛИ и соединены с информационным входом и входом записи - считывания модели нейрона соот" g5 ветственно, выход элемента ИЛИ подключен к первому входу второго элемента И, второй вход которого соединен с единичным выходом триггера, выход второго элемента И подключен к входу генератора импульса, выход которого является выходом модели нейрона, модели многовходовых нейронов, каждая из которых состоит иэ сумматора, прямые входы которого соединены с входами модели многовходового нейрона, тормозящий вход которой под.ключен к инверсному входу сумматора, выход которого соединен с входом порогового элемента, выход которого подключен к генератору импульса, выход которого является выходом модели многовходового нейрона, управляющий вход порогового элемента соединен с входом регулирования порога срабатывания модели многовходового нейрона, и модели тормозящих нейронов, каждая из которых состоит из генератора импульса, выход которого через инвертор подключен к выходу модели тормозящего нейрона, о т л и ч а ю щ ая с я. тем, что, с целью упрощения модели, модели нейронов образуют матрицу и х m причем входы сброса моделей нейронов каждой Ый (i = 1, 2, n) строки подключены к 1-ому разряду и разрядной шины сброса, каждый i-й разряд и разрядной шины записи — считывания соединен с вхо.дами записи — считывания моделей нейронов i-й строки и через i-ю модель тормозящего нейрона с тормозящим входом i-й модели многовходового нейрона, выход которого подключен (1+1) -ому разряду шины записи — считывания, j-й (j 1, 2, ..., m) разряд входной информационной шины соединен с информационными входами моделей нейронов j-го столбца, выходы которых подключены к у-ому разряду выходной информационной шины, выходы моделей нейронов i-й строки соединены с соответствующими входами i-й модели многовходового нейрона, вход регулирования порога срабатывания нейрона соединен с i-ым разрядом и разрядной шины регулирования порога срабатывания.

Источники информации; принятые во внимание при экспертизе

1. Грановская Р. M. Ганзен В. A.

Одна из возможных моделей сети, отличающаяся ассоциативной памятью.

В кн. : Оперативные и постоянные запоминающие.устройства, М.-Л., "Энергия", 1964, .с. 179-186.

2 ° Кохонен Т. Ассоциативная память.

М., "Мир", 1980, с. 213 (прототип).

968827

Фиа 8

Составитель A. Яицков

Редактор Л. Лукач Техред A.Áàáèíåö Корректор М. Коста

Заказ 8177/78 Тираж 731 Подписное

ВНИИПИ Гс сударственного комитета СССР по делам изобретений и открытий.

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4