Устройство управления

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Iii) 970368 (61) Дополнительное к авт. свид-ву (22) Заявлено 24.02.81 (21) 3291500/18-24 (51)M.Кп з с присоединением заявки ¹â€” (23) Приоритет

C 06 F 9/22

Государственный комитет

СССР но делам изобретений и открытий

Опубликовано301082. Бюллетень № 40

Дата опубликования описания 30.10.82 (53) УДК 681.329 (088. 8) 1 (72) Авторы изобретения

Л .Н ° ÇâoÐûêèí и A.Ë.Ëàíöîâ (71) Заявитель (54) VCTPOACTBO yIIpABZIEII@g

Изобретение относится к вычислительной технике и может быть использовано при разработке процессоров широкого и специального назначения.

Известны устройства управления,имеющие регистровую память для оперативного доступа к данным, обладающие ограниченным быстродействием, обуслов- ленным необходимостью передачи резуль-)p тата обратно в регистровую память через промежуточный буферный регистр(1 ).

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее сумматор, блок ввода, выход которого соединен с первым входом центрального коммутатора, первый выход которого соединен с входом блока вывода, и дешифратор управ- лян щих.-сигналов, соединенный по выхоЦу с входом блока переключения регистров, первый выход которого соединен с управляющим входом первого регистра, а второй выход подключен к управляющему входу второго регистра (23. 25

Однако. необходимость предварительного запоминания результата в буфер-ном регистре перед его загрузкой в один иэ регистров, уменьшает быстродействие устройства. ЭЦ

Цель изобретения .— повьхаение бы стродействия.

Поставленная цель достигается тем, что в устройство управления, содержащее блок переключения регистров, первый и второй входы которого через дешифратор соединены с входом устройства, первый и второй выходы блока переключения регистров соединены с управляющими владами соответственно первого и второго основных регистров, выход входного регистра соединен с первым входом центрального коммутатора, первый выход которого соединен с входом выходного регистра, второй вход центрального коммутатора подключен к выходу сумматора, дополнительно введены два регистра и два коммутатора, причем выход первого дополнительного регистра подключен к первому информационному входу первого дополнительного коммутатора, выход которого соединен с первым входом сумматора, а выход второго дополнительного регистра соединен с первым информационным входом второго дополнительного коммутатора, выход которого подключен к второму входу сумматора, второй выход центрального коммутатора подключен к

9703б8 информационным входам первых и вторых дополнительных и основных регистров, выходы первого и второго основных регистров соединены с вторыми информационными входами соответ- ственно первого и второго дополни- 5 тельных коммутаторов, управляющие входы которых соединены с третьим и четвертым выходами блока переключения регистров, пятый выход которого соединен с управляющим входом первого дополнительного регистра, а шестой выход блока переключения регистров подключен к управляющему входу второго дополнительного регистра.

Кроме того, блок переключения ре- гистров содержит два счетных тригге)ра, элемент НЕ и шесть элементов И, причем первый вход первого элемента

И соединен с первым входом второго элемента И и с первым входом блока, второй вход первого элемента И соединен с вторым входом блока и через элемент НЕ с вторым входом второго элемента И, выход которого соединен с входом первого счетного триггера и с первыми входами третьего и четвертого элементов И, вторые входы которых соединены с соответствующими выходами первого счетного триггера, выходы третьего и четвертого элементов И соединены соответственно с вторым и шестым выходами блока, второй вход четвертого элемента И соединен с четвертым выходом блока, выход первого элемента И соединен с входом второго счетного триггера и с первыми35 входами пятого и шестого элементов И, вторые входы которых соединены с сооТветствующими выходами второго счетного триггера, второй вход шестого элемента И соединен с третьим выходом блока4 выходы пятого и шестого элементов И соединены соответственно с первым и пятым выходами блока.

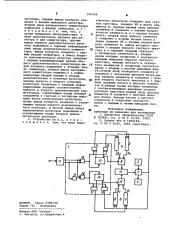

На чертеже показана структурная

° электрическая схема устройства. 45

Устройство управления содержит, блок 1 переключения регистров, центральный коммутатор 2, соединенный с входным регистром 3 и выходным регистром 4, два основных регистра 5 и б два дополнительных регистра 7 и 8 два дополнительных коммутатора 9 и

10, дешифратор 11 и сумматор 12.

Блок 1 переключения регистров содержит два счетных триггера 13 и 14, шесть элементов И 15-20 и элемент

Н 21.

Устройство работает следующим образом.

Через. управляющий вход устройства в дешифратор 11 вводится код опера- 60 ции, реализуемой вычислительным устройством. Дешифратор 11 на своем выходе формирует управляющие сигналы для всего устройства, которые поступают на входы блока 1. На первом 5 выходе дешифратора 11 формируется тактирующий сигнал, задающий время выполнения микрокоманды в устройстве.

На втором выходе дешифратора 11 формируется сигнал записи результата.

Этот сигнал выбирает регистр, в который должен быть помещен результат.

В течение времени с помощью счетных триггеров 13 и 14 в каждой из пар регистров 5, 7 и б, 8 выбирается ведущий и ведомый регистры.

Так, если счетные триггеры 13 и

14 находятся в состоянии "0", из регистра 5 и регистра б считывается информация, по которой в сумматоре

12 формируется необходимая функция.

Если счетные триггеры 13 и 14 нахо дятся в состоянии "1", то информация считывается из регистров 7 и 8.Считываемая из сумматора 12 информация через центральный коммутатор 2 записывается в один из регистров.

Ведущие регистры через соответствующие коммутаторы 9 и 10 подключаются к одному из входов сумматора

12. Результат с выхода сумматора 12 через центральный коммутатор 2 записывается. в один из ведомых регистров. После выполнения операции в сумматоре 12 и записи его в один из ведомых регистров, по заднему фронту тактирующего сигнала происходит переход в другое состояние того триггера, по предыдущему состоянию которого. была осуществлена запись результата.

В итоге, в управляемой этим триггером паре регистров прй выполнении следующей операции ведущего и ведомого регистров меняются: ведущий регистр становится ведомым, а ведомый — ведущим, т.е. теперь операнд ,будет считываться из регистра, в котором на предыдущей операции был занесен. результат. Иначе говоря, в каждый момент времени в устройстве определяются "плавающие" рабочий и буферный регистры.

Это позволяет осуществить так называемое однократное выполнение операций, при котором отсутствует необходимость выделения времени на запись результата в буферный регистр, что повышает быстродействие устройства.

Формула изобретения

1. Устройство управления, содержащее блок переключения регистров, первый и второй входы которого через дешифратор соединены с входом устройства, первый и второй выходы блока переключения регистров соединены с управляющими входами соответственно первого и второго основных регистров, выход входного регистра соединен с первым входом центрального ком 970368

ВНИИПИ Заказ 8

Тираж 731 Подп мутатора, первый выход которого соединен с входом выходного регистра, второй вход центрального коммутатора подключен к выходу сумматора, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него дополнительно введены два регистра и два коммутатора, причем выход первого дополнительного регистра подключен к первому информационному входу дополнительного кошута- 10 тора, выход которого соединен с первым входом сумматора, а выход второго дополнительного регистра соединен с первым информационным входом второго дополнительного коммутатора,вы- !5 ход которого подключен к второму входу сумматора, второй выход центрального коммутатора подключен к информационным входам первых и вторых дополнительных и основных регистров, 2О выходы первого и второго основных регистров. соединены с вторыми информационными входами соответственно первого и второго дополнительных коммутаторов, управляющие входы которых соединены с третьим и четвертым выходами блока переключения регистров, пятый выход которого соединен с управляющим входом первого дополнительного регистра, а шестой выход блока переключения регистров подключен к управляющему входу второго дополнительного регистра.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок переФилиал ППП "Патент", r. Ужгород, ул.Проектная,4 ключейия регистров содержит два счетных триггера, элемент НЕ и шесть элементов И, причем первый вход первого элемента И соединен с первым входом второго элемента И и с первым входом блока, второй вход первого элемента

И соединен с вторым входом блока и через элемент НЕ с вторым входом второго элемента И, выход которого соединен с входом первого счетного триггера и с первыми входами третьего и четвертого элементов И, вторые. входы которых соединены с соответствующими выходами первого счетного триггера, выходы третьего и четвертого элементов И соединены соответственно с вторым и шестым выходами блока,второй вход четвертого элемента И соединен с четвертым выходом блока,выход первого элемента И соединен с входом второго счетного триггера и с первымн входами пятого и шестого элементов И,вторые входы которых соединены с соответствующими выходами второго счетного триггера, второй вход шестого элемента И соединен с третьим выходом блока, выходы пятого и шестого элементов И соединены соответст-венно с первым и пятым выходами блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 302981, кл. G 06 F 15/00, 1969.

2. Патент ФРГ 9 1499184, кл. G 06 F 9/00, 1969 (прототип).