Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Соевтскик

Социалистических

Республик ф

//, г /

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 010431 (21) 3270224/18-24 (54) М. Кл.з

G 06 G 7/16 с присоединением заявки ¹ (23) ПриоритетГосударственный комитет

СССР по деаам изобретений и открытий (53) УДК 681. 335 (088. 8) Опубликовано 30.1082. 6юллетейь №" 40 .Дата опубликования описания 3Q10.82

A.A ° Шкиль и A,Н. Дигун (72) Авторы . изобретения (71) Заявитель

Институт .гидромеханики AH y (54) MHOEHTEJIbHO-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к области аналоговой вычислительной техники.

Известны устройства подобного. типа, содержащие блоки логарифмирования и антилогарифмирования (1).

Недостатками этих устройств является низкая точность работы и ограниченный диапазон рабочих частот.

Наиболее близким по технической сущности к предлагаемсму является множительно-делительное устройство, содержащее первый, второй и третий блоки логарифмирования,. выходы которых подключены к соответствующим входам сумматора, и блок антилогарифмирования, вход которого подключен к выходу сумматора (2).

Недостатком этого устройства является низкая точность работы,связанная с паразитным влиянием вход- . ных токов и напряжений смещения усилителей, а также ограниченный диапазон .рабочих частот устройства при малых уровнях входных сигналов.

Цель изобретения — повышение точности работы и расширение диапазона рабочих частот устройства.

Поставленная цель достигается тем, что в множительно-делительное устройство, содержащее первый, второй и третий блоки логарифмирования, блок антилогарифмирования и первый сумматор, выходы блоков логарифми5 рования подключены к соответствующим входам первого сумматора, выход которого подключен к входу бло-, ка антилогарифмирования, введены три блока сравнения, три блока умножения, источник опорного напряжения, второй сумматор, блок деления, выход которого является выходом устройства, а входы подключены соответственно к выходам блока антилогарифмирования и второго сумматора, первый вход первого блока сравнения и первый вход первого блока умножения объединены и являются первым входом. устройства, первый вход второго блока сравнения и первый вход второго блока умножения объединены и являются вторым входом устройства, первый вход третьего .блока сравнения и первый вход третьего блока умножения объединены и

25 являются третьим входом устройства, вторые входы блоков умножения подключены к выходам соответствующих блоков сравнения, вторые входы блоков сравнения подключены к соответЗО ствуюшим выходам источника опорного

970390

25

40 напряжения, выходы первого, второго и третьего блоков сравнения подключены соответственно к первому, второму и третьему входам второго сумматора, выходы первого, второго и третьего блоков умножения подключены соответственно к входам первого, второго и третьего блоков логарифмирования.

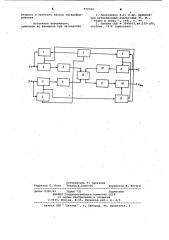

На чертеже приведена блок-схема множительно-делительного устройства.

Множительно-делительное устройст-. во содержит блоки 1 - 3 сравнения, блоки 4 - 6 умножения, источник

7 опорного напряжения, блоки 8 - 10 логарифмирования, блок 11 антилогарифмирования, сумматоры 12 и 13 и блок 14 деления.

Множительно-делительное устройство работает следующим образом.

В зависимости от величины входного сигнала Х на выходе блока 1 сравнения вырабатывается сигнал Х» такой, что при подаче его на второй вход блока 4 умножения на выходе последнего формируется сигнал

A = Х а 6 (А,„„.,„,А„„ х), SbN где (А„д„.„,А„„ох) — выбранный рабочий диапазон блока умножения; х A >x,. а

Иии

Аналогичным .образом масштабируются входные сигналы Y u Z.. Таким образом, на выходы блоков 8 — 10 логарифмирования поступают сбответственно сигналы

АВЫх = Х ах;

К, "вью = у a "

К

A = g,° . аКт.

Ьых

С выходов блоков логарифмирования на соответствующие входы первого сумматора 12 поступают сигналы

A+X =. Cn(a Y) р

Кх, А>Х Еп (аЧ. Е);

A> = Сп (а Х),.

ЬХ

С выхода первого сумматора на вход блока 11 антилогарифмирования подается сигнал

Aübх LNO

Кх+хч-к Х > ьых

++(v ,а с выхода блока антилогарифмирования снимается сигнал

1 й.Вй X.х+КЧ - k> q

Ь Х 7

Выходные снгналы блоков сравнения-К,КЧ и К поступают на входы второго сумматора 13, в котором осуществляется операция

К = Х+ 1 Ъ.

Значение сигнала К. подается на второй вход блока 14 деления, под

39

65 действием которого на выходе блока

14 формируется сигнал

Х К -К» д Вых Q " ХЧ ХЧ

BbIx ах 0" KvК 7 7

Использование новых элементов

,первого, второго и третьего блоков умножения, первого, второго и третьего блоков сравнения, второго сумматора и блока деления позволяет уменьшить паразитное влияние разности вхоДных токов и напряжений смещений входных усилителей, что сказывается на точности работы устройства в целом, и за счет увеличения уровня входного сигнала, подаваемого на вход блока логарифмирования, расширяется диапазон рабочих частот устройства.

Формула изобретения

Множительно-делительное устройст-. во, содержащее первый, второй и тре- тий блоки логарифмирования, блок антилогарифмирования и первый сумматор, выходы блоков логарифмирования подключены к соответствующим входам первого сумматора, выход кбторого подключен к входу блока антилогарифмирования, о т л и ч а ю щ ее с я тем, что, с целью повышения точности и расширения диапазона рабочих частот, в него введены три блока сравнения, три блока умножения, источник опорного напряжения, второй сумматор, блок деления, выход которого является выходом устройства, а входы подключены соответственно к выходам блока антилогарифмирования и второго сумматора, первый вход первого блока сравнения и первый вход первого блока умножения объединены и являются первым входом устройства, первый вход второго блока сравнения и первый вход второго блока умножения объединены и являются вторым входом устройства, первый вход третьего блока сравне-. ния и первый вход третьего блока умножения объединены и являются третьим входом устройства, вторые входы блоков умножения подключены к выходам соответствующих блоков сравнения, вторые .входы блоков сравнения подключены к соответствующим выходам источника опор- ного напряжения, выходы первого, второго и третьего блоков сравнения подключены соответственно к первому, второму и третьему входам второго сумматОра, выходы первого, второго и третьего блоков умножения подключены соответственно к входам первого, 970390

У!

Составитель Т. Сапунова

Редактор Е. Папп Техред A.Áàáèíåö ". Корректор В Бутяга

Заказ 8390/61 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 второго и третьего блоков логарифмирования.

Источники информации, принятые во внимание при экспертизе

3 б

1. Алекоеенко А.Г. и др. Применение прецизионных аналоговых ИС. М., Радио и связь, 1991., с. 94;

2. Патент США 9 3940603,кл.235-195, опублик. 1976 (прототип).