Усилитель считывания

Иллюстрации

Показать всеРеферат

(ii>970461

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. саид-ву(22) Заявлено 29.04. 81 (21) 3282911/18 24

{51) M. Кл.з с присоединением заявки ¹(23) Приоритет

6 11 С 7/00

Государственный комитет

СССР по делам изобретений и открытий (531УДК б81.327 °

° б (088.8) Опубликовано 3010.82. Бюллетень ¹ 40

Дата опубликования описания 30.10.82 (72) Авторы изобретения

Сидоренко Ю.A. Юхкменко, В.П. Чекалкин,- .-+ <( и С.Н. Исаева

:..р -грнтg0..

Т

В (71) Заявитель (54) УСИЛИТЕЛЬ СЧИТШАНИЯ

Изобретение относится к электронной и вычислительной технике и предназначено, в частности для исполь-. зования в интегральных полупостоянных запоминающих устройствах (ЗУ). : 5

Известны подобные устройства, используемые в ЗУ в качестве усилителей считывания, обеспечивающие усиление сигнала, поступающего с выбранного запоминающего элемента 10 накопителя до величины, достаточной для срабатывания посдедующих схем.

Один из известных усилителей считывания содержит триггер, состоящий из двух инверторов, перекрестно связанных между собой. Каждый йивертор включает ключевой транзистор и транзистор, являющийся нагрузкой, включенные последовательно. Нагрузки обоих интервалов соединены с 20 первым источником напряжения питания, а их ключевые транзисторы подключены через общий дополнительный транзистор, управляемый сигналом, подаваемым иа его затвор, ко второму источнику напряжения, причем между первым и втоЙрым выходом схемы триггера включенпоперечный транзистор (1).

Недостатками укаэанного усилителя считывания являются малая чувствительность и низкое быстродействие вследствие того, что узловые емкости числовых шин непосредственно связаны с входами усилителя.

Схема усилителя имеет два входа для приема информации из накопителя, в результате чего для обработки усилителя необходимо два входных сигнала, что затрудняет применение данных усилителей для считывания информации иэ ячеек накопителя, имеющих одну числовую шину.

Наиболее близкий по технической ,сущности к предлагаемому усилитель

;считывания содержит тркггерную схему, состоящую из двух инверторов,перекрестно связанных между собой, причем каждый из инверторов содержит ключевой транзистор, последовательно соединен ный с нагрузочньви транзистором,затвор и сток которого подключены к первому источнику питания, а исток ключевого транзистора соединен со вторым источником питания. Кроме тогЮ, между числовой шиной и соответствующим выходом триггера включен как минимум один барьерный транзистор, к стоку барьерного транзистора и числовой шине подключен сбросовый транзистор предварительной установки, на затвор которого поступает управляющий сигнал (2) .

970461

Недостатками известного усилйтеля являются низкая чувствительность усилителя из-эа конструктивных и.технологических неоднородностей парамет ров цепей нагрузки, подключаемых ко входу усилителя, а также то, что . 5 схема имеет два входа для,приема информации из накопителя, в результате чего ля обработки усилителя необходимо два входных сигнала, что затрудняет применение усилителя для счи-10 тывания информации из ячеек накопителя, имеющих одну числовую шину.

Цель изобретения — увеличение чувствительности и быстродействия усилителя считывания. !

Поставленная цель достигается тем, что в усилитель считывания, содержащий управляющий транзистор, транзистор сброса и два перекрестно,связанных инвертора, каждый из которых состоит из последоват ьио с единенн 2О ключевого и нагрузочного транзисто- . ров, затворы и стоки нагрузочных транзисторов подключены к первому источнику питания, барьерные транзисторы и транзисторы сброса,, введены два каскада, каждый из которых гостоит из зарядного, усилительного и разрядного транзисторов, причем стоки зарядных транзисторов каскадов подключены к первому источнику пи- . 30 тания, а истоки и затворы зарядных транзисторов соединены со стоками соответствующих транзисторов сброса и разряда, и истоками усилительных транзисторов, стоки которых подклю- 3$ чены к истокам нагрузочных транзисторов, затворы усилительных тарнзисторов подключены к истокам соответствующих барьерных транзисторов, затворы транзисторов сброса, и затвор одного 4О барьерного транзистора подключены к первой шине управления, затвор друго го барьерного транзистора подключен

lao второй шине управления, затвор другого барьерного транзистора подключен ко второй шине упр ления, а затвор управляющего транзистора— к третьей шине управления, истоки транзисторов сброса, разрядных и исток управляющего транзистора подклю. чены ко второму источнику питания, 50 сток управляющего транзистора подключен к стокам ключевых транэисторову а .стоки барьерных транзисторов объединены и являются входом усилителя считывания. 55

Транзисторы заряда выполнены со встроенным каналом.

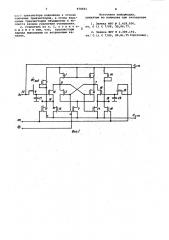

На фиг. l представлена принципиальная электрическая схема усилителя считывания1 на фиг. 2 - временная диаграмма управляющих н выходных сигналов.

Усилитель содержит нагруэочные транзисторы 1 и 2, ключевые транзисторы 3 и 4, управляющий транзистор 5, 65 выходы 6,7, один барьерный транзистор 8, зарядный транзистор 9, усилительный транзистор 10, транзистор 11 сброса, разрядный транзистор 12, другой барьерный транзистор 13, зарядный транзистор 14, усилительный транзистор 15, транзистор 16 сброса, транзистор 17 разряда, выходы 18 и

19, вход усилителя 20 шины.

Предлагаемый усилитель считывания запоминает напряжение, поступающее. по числовой шине на вход усилителя

20 в начельный момент времени, сравнивает его .с напряжением, поступающим на вход усилителя в процессе считывания,информации и усиливает полу-, чаемый при этом незначительный раэностный сигнал. Рассмотрим подробнее работу схемы, начиная с того момента времени, когда на затворы транзисторов 11,,13 и 16 поступает первый, управляющий сигнал Ф 1, напряжение которого равно Лог.О, на затвор транзистора 8 поступает второй управляющий сигнал Ф1, напряжение которого равно Лог.О, а на зат,вор транзистора 5 поступает запус-. кающий сигнал Ф 1, напРяжение которого равно Лог.l . В результате этого стробируемый триггер, выполненный на транзисторах 1-5 включается запускающим сигналом Ф 1 и устанавливается в состояние, определяемое информацией, считанной из.ячейки накопителя. С выходов триггерной схемы 6 и 7 сигнал поступает на затворы транзисторов 12 и .17, вследствие чего на одном из выходов усилителя считывания формируется напряжение Лог.О, а на другом — Лог.1! . После того, как на выходах усилителя 18 и 19 считывания сформировался сигнал, приходит второй управляЮщий сигнал Ф1м напряжение которого равно Лог.l, и происходит предварительный заряд числовой шины, подключенной к входу

20 усилителя, до нулевого напряжения, которое через открытый транзистор 8 передается на емкость Cl, Когда на затвор транзистора 8„ управляемого вторым управляющим сигналом Ф 1 д < приходит напряжение Лог.О, он запирается и на емкости Cl запоминается напряжение, соответствующее исходному состоянию числовой шины. Одновременно с этим на затворы транзисторов 11,13 и 16 поступает. первый управляющий сигнал Ф 1, напряжение которого равно Лог.l и начинается новый цикл считывания информации из ячеек накопителя ЗУ. Информационный сигнал, считываемый из ячейки, формируется на входе 20 усилителя и через открытый транзистор 13 передается на емкость С2. Таким образом, на затворе транзистора 15 устанавли вается напряжение, определяемое ин формационным сигналом, считываемым

970461 из ячейки, а на затворе транзистора

10 устанавливается напряжение, определяемое предварительным зарядом ем. кости числовой шины. Транзисторы 11 и 16 открыты и подключают истоки транзисторов 10 и 15 к источнику напряжения 0„ q,g, в результате чего образуются два делителя напряжения; первый из транзисторов 1, 10, 11 и 9, второй из транзисторов 2, 15, 16 и

14, в которых усилительные транзисто- 10 ры 10 и 15 играют роль переменных сопротивлений.

Геометрические размеры транзисторов 10 и 15 подобраны таким образом, что при изменении входного сигнала в пределах нуль вольт, они работают в линейном режиме и их коэффициент усиления по напряжению равен 3. На выходах б и 7 устанавливаются уровни напряжений; определяемые проводи-. мостью транзисторов 10 и 15. С приходом отпирающего напряжения на затвор транзистора 5, напряжение на выходах 6 и 7, предварительно установленное до прихода запоминающего сигнала 1, обеспечивает надежный переброс триггера в заданное состояние.

Если в процессе предварительного усиления потенциал на выходе 6 оказался выше потенциала в узле 7, то при поступлении отпирающего на- . пряжения на затвор транзистора 5 потенциал на выходе 6 быстра возрастает, а на выходе 7 продолжает понижаться. Понижение потенциала на выходе 7 приводит к уменьшению прово- 35 димости транзистора 12 и увеличению потенциала на выходе 18 усилителя считывания за счет тока зарядного транзистора 9. Транзистор 10 запирается и в дальнейшем не влияет на по» 4Q тенциал .на выходе 6. Возрастание потенциала на выходе б приводит к отпиранию транзисторов 4 и 17, при этом напряжение на выходе 19 усилителя считывания уменьшается, в результате чего увеличивается проводимость транзистора 15, что приводит. к снижению потенциала на выходе 7.

Таким образом, предварительно установленное напряжение на выходах 6 и 7 с приходом запускающего сигнала фl обеспечивает надежный переброс триггера в заданное состояние, Лавинообразный процесс опрокидывания триг- гера завераается тогда, когда на вы» ходе б триггера устанавливается максимальное напряжение, равное

Формула изобретения

1. Усилитель считывания, содержа- . щий управляющий транзистор, транзистор сброса и два перекрестно связанных инвертора, каждый иэ которых состоит из последовательно соединенных ключевого и нагруэочного транзисторов, затворы и стоки нагрузочных транзисторов подключены к первому источнику питания, барьерные транзисторы и транзисторы сброса,о т л и ч а юшийся тем,что,с целью повышения быстродействия и чувствительности усилителя считывания,он содержит два каскада, каждый из которых состоит иэ зарядного, усилительного и разрядного транзисторов, причем стоки зарядных .транзисторов каскадов подключены к первому источнику питания, а истоки и затворы зарядных транзисторов соединены со стоками соответствующих транзисторов сброса и разряда и истоками усилительных транзисторов, стоки которых подключены к истокам нагрузочных траизисторов, затворы усилительных транзисторов подключены к истокам соответствующих барьерных транзисторов, затворы транзисторов сброса и затвор одного барьерного транзистора подключены к первой шине управления, затвор другого барьерного транзистора подключен к второй. шине управления, а затвор управляющего транзистора — к третьей шине управления, истоки транзисторов сброса, разрядных и исток управляющего транзистора подключены к второму источнику питания, сток управляю1 б" и.я.1 nop " "nop >4 р

1 где 0 — пороговое напряжение тран- 60 пор эистора с индуцированным каналом;

Ч вЂ” уровень Ферми, равный 0,59;

K — коэффициент влияния подложки. 6$

При этом на противоположном выходе триггера 7 формируется напряжение, равное напряжению источника U. „ =

=U =U> z. Через 100-150 нс после переброса триггера на затвор транзис,тора 8 поступает отпирающий потенциал второго управляющего сигнала Ф 1, в результате чего затвор транзистора

10 и запоминающая емкость Сl подключаются к входу усилителя. Схема возвращается в исходное состояние и вновь готова к приему считываемой информации.

Таким образом, разделение во времени процесса считывания с помощью управляющих и запускающего сигналов и применение данной схемы усилителя сЧитывания приводит к увеличению быстродействия на ЗОВ, уменьшению потребляемой мощности в 1,5 раза и получению чувствительности усилителя 150200 мВт.

Предлагаемое техническое решение использовано в изделии, ожидаемый эффект от применения которого составит 863,1 тыс. руб при годовом объеме выпуска 10 тыс. шт. схем в год.

970461 фМ2. / ц "o транзистора подключен к стокам ключевых транзисторов, а стоки барьерных транзисторов объединены и являются входом усилителя считывания.

2..усилитель по п. 1, о т л и ч аю шийся тем, что, транзисторы 5 заряда выполнены .со встроенным каналом .

Источники информации, принятые во внимание при экспертизе

1. Заявка ФРГ Р 2.418.936, .кл. G ll С 7/00, 30,06.77.

- 2. Заявка ФРГ Р 2.309.192, кл. G 11 С 7/00, 09 01.75 (прототип), 970461

b7

1S f3

Составитель В.. ГордоноваРедактор А. Власенко Техред В.Кастелевич Корректор A- Ференц

Закаэ 8397/64 Thtpaa 622 Подписное

ВНИИПК Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, й-35, Раувакая наб., д. 4/5

Филиал ППП Патент, r. уигород, ул. Проектная, 4