Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советскик

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6!) Дополйительное к авт. саид-ву(22) Заявлено 30.04.81 (21) 328 908/18-24 jj)) М. Кд.З с присоединением заявки ¹ (23) ПриоритетG 1l С 11/00

Государственный комитет

СССР ио делам изобретений и открытий

Опубликовано 3(11(182. Бюллетень № 40

t$3) УДК 681.327 (0&8. 8) Дата опубликования описания 30.10. 82 (72) Авторы изобретения

А С - горшков, E.Ô. Науман, Ю.д. luyheHH и В.И. Служеникин (7!) Заявитель (54 ) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам.

Известно оперативное запоминающее устройство (ОЗУ), содержащее модули памяти, синхронизирующий Ъ енератор, вспомогательный адресный регистр .и узел управления, причем каждый модуль памяти содержит накопитель, ддресные и разрядные формирователи и переключатели, усилители воспроизведения, регистры адреса и числа, узел синхронизации, формирователь етробов, схему контроля по суетности, схему исправления кода и буферные регистры, (1) .

Недостатком этого устройства является отсутствие импульсного (коммутируемого )питания элементов и узлов электронного обрамления в модулях памяти, что приводит к дополнительному потреблению мощности ОЗУ.

Наиболее близким техническим ре-. шением к изобретению является оперативное запоминающее устройство, содержащее модули оперативной памяти и узел управления памятью, выходы и вход которого подключены соответственно к группе шнн Обращения, к двум группам адресных и информационных шин, каждый модуль оперативнрй памяти содержит накопитель, первый вход которого соединен с выходом формирователя адресных токов, а выход и второй вход его соединены с разрядньм блоком, другие входы и выход которого соединены соответственно с третьим выходом распределителя импульсов, с первым выходом коммутатора питания, двумя выходами второго коммутатора питания и двумя группами информационных шин, входы формирователя адресных токов соединены, соответственно с второй группой адресных шин„ со вторыми выходами распределителя импульсов и первого коммутатора питания, третий выход которого соединен с первым входом распределителя импульсов, первые входы коммутаторов питания и шифратора соединены с соответствующими выходами блока питания, второй вход второго коммутатора питания соединен с четвертым выходом распределителя импульсов, второй вход которого сое25 динен с группой шин Обращения, а третий †. с первым выходом шифратора, второй вход которого соединен с первой группой адреснь;с шин (2).

Однако это устройство не обеспе30 чивает снижения мощности, потребля970462

Поставленная цель достигается тем,(0 что в оперативном запоминающем устройстве, содержащем блок управления, / источник питания и блоки памяти, каждый из которых состоит из накопителя, первый вход которого соединен с выходом формирователя адресных токов, а выход и второй вход накопителя соединены с одними из входов и выходов разрядного блока, другие входы и выходы которого соединены соответствен- 20 но с первыми выходами распределителя импульсов и первого коммутатора, выходаМи Второго коммутатора, информационными выходами и входами блока управления, входы формирователя ад-, 25 ресных токов соединены соответственно с одним из адресных выходов блока управления, со вторыми выходами распределителя импульсов и первого коммутатора, третий выход которого сое- щ дннен с первым входом распределителя импульсов, первые входы коммутаторов и шифратора соединены с первым выводом источника питания, второй. вход второго коммутатора соединен с третьим выходом распределителя импульсов, второй вывод источника питания подключен к третьему входу второго коммутатора, второй вход распределителя импульсов подключен к первому выходу шифратора, третий вход 40 распределителя импульсов и вторОй вход шифратора соединены соответственно с выходом ™Обращение блока управления и с другим адресным выходом. блока управления, в ка дый блок 45 памяти введены элемент задержки, усилитель, элемент ИЛИ, триггер и элемен И, первый и второй входы которого подключены соответственно ко второму выходу шифратора и выходу 5О элемента задержки, первые входы элемента задержки и элемента ИЛИ подключены ко входу Обращение " блока управления, второй вход элемента ИЛИ соединен с.четвеРтым выходом Распре". делителя импульсов, выход элемента И соединен с первым входом триггера, .второй вход которого соединен с выходом элемента ИЛИ, выход триггера подключен к первому выходу усилителя, выход которого соединен со вторым входом первого коммутатора, втоРые входы элемента задержки и усилителя и третьи входы триггера, элементов И и ИЛИ соединены с первым выводом источника питания.

65 емой ОЗУ в режиме обращения, так как во. время обращения к данному

ОЗУ питающие напряжения подаются на все блоки и элементы электронного обрамления, что вызывает повышенное потребление мощности ОЗУ большой ин- 5 формационной емкости.

Цель изобретения — снижение пот,ребляемой устройством мощности.

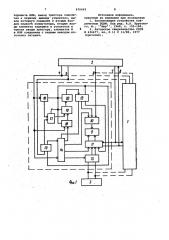

На фиг. 1 изображена функциональная схема оперативного запоминающего устройства; на фиг. 2 — временные диаграммы, поясняющие работу этого .устройства.

Устройство (фиг. 1) содержит бло-. ки 1 памяти, блок 2 управления, источник 3 питания, Блок 2 имеет выход 4 Обращение, адресные выходы

5 и 6, информационные выход 7 и вход

8. Каждый блок 1 содержит накопитель

9. формирователь 10..адресных токов, разрядныо блок 11, первый 12 и второй 13 коммутаторы, распределитель

14 импульсов, шифратор 15, элемент 16 задержки, элемент И 17, элемент

ИЛИ 18, триггер 19 и усилитель 20.

Устройство работает следующим образом.

В перИод обращения к устройству по интерфейсным связям (данные связи на фиг. 1 не показаны) в блок 2 управления от внешних устройств подаются байты адреса, байт слова только при выполнении операции Запись, а также сигнал признака операции, которые фиксируются в блоке 2.

Байты адреса определяют номер блока 1 памяти и адрес ячеек памяти, к которым осуществляется обращение в выбранном блоке 1.

Сигнал признака операции определяет основные операции ОЗУ, т.е. Запись или Считывание .

Блок 2 организует обращение к блокам 1 согласно принятому от внешних устройств коду адреса и признака операции.

С выхода 4 блока 2 в блоки 1 поступают сигналы начального сброса

НСБР, СТАРТ (фиг. 2) и сигнал признака операции. Выдача байтов адреса, байта слова, а также сигнала признака oneрации в блоки 1 .осуществляется по сигналу НСБР. Параллельный код адреса, поступающий с выхода 5 блока 2, подается на входы шифратора 15. Количество разрядов адреса зависит от числа блокоВ 1 в структуре ОЗУ. Номер конкретного блока 1 набирается в шифраторе 15 с помощью элементов коммутации в двоичном коде. При совпадении кода адреса с номером блока 1 на выходах шифратора 15 формируется сигнал A положительной полярности (фиг. 2) .

Параллельный.код адреса, поступающий с выхода 6 блока 2, определяет адрес ячеек памяти в выбранном блоке 1. Сигнал КСБР подается на первые входы элемента 16 задержки и элемента ИЛИ 18. Этот сигнал через элемент

ИЛИ 18 подается на вход триггера 19.

По переднему фронту сигнала НСБР осуществляется установка триггера 19 в исходное 0 -состояние после включения питания всего устройства и подтверждение исходного состояния

970462 триггера 19 в процессе работы в каждом цикле обращения. Задержанный сигнал начального сброса НСБРЗ с выхода .,элемента 16 задержки поступает на второй. вход элемента И 17.

Сигнал A с выходов шифратора 15 5 подается на вход распределителя 14 импульсов и на первый вход элемента И 17. Этот сигнал разрешает установку триггера 19 в 1 -состояние по переднему фронту сигнала НСБРЗ и 10 обращение к выбранному блоку 1 по переднему фронту сигнала СТАРТ. На выходе триггера 19 формируется сигнал С положительной полярности, который через усилитель 20 обеспечивает включение первого коммутатора 12, а, следовательно, и подачу питающего напряжения к распределителю 14 им-. пульсов, к формирователю 10 адресных токов и к разрядным формирователям О токов, которые являются частью разрядного блока 11. По спаду импульсного сигнала НСБР осуществляется установка элементов распределителя 14 импульсов в исходное состояние. 25

С приходом сигнала СТАРТ в выбранном блоке 1 осуществляется запуск распределителя 14 импульсов и организуется цикл обращения Тц. Распределитель 14 импульсов формирует в цикле З-О обращения сигналы управления формирователем 10 адресных токов, разрядным блоком 11 и вторым коммутатором

13. Второй коммутатор 13 включается по,сигналу D положительной полярности и обеспечивает подключение пита- ющих напряжений к другой части разрядного блока (усилители считывания) только на время, необходимое для считывания информации.

После окончания цикла обращения 40 распределитель 14 импульсов формирует сигнал В положительной полярности, который подается на вход элемента

ИЛИ 18

По переднему фронту сигнала В,. 45 поступающему с выходов элемента

ИЛИ 18 на вход триггера 19, осуществляется установка его в исходное 0 -состояние и осуществляется выключение первого коммутатора 12. у

Таким образом, длительность сигнала

С определяется интервалом времени между передними фронтами сигналов

НСБРЗ и В. В режиме хранения информации питающее напряжение постоянно подключено к шифратору 15, триггеру

19, усилителю 20, к элементу 16 задержки и к элементам И 17, ИЛИ 18.

При необходимости питающие напряжения подаются на элементы накопителя

9, которые обеспечивают режим хране- ® ния информации.

С выхода 7 блока 2 перед началом обращения (по переднему фронту НСБР) при выполнении операции Запись ° на информационные входы разрядного 65 блока 11 всех блоков 1 поступает байт слова из блока 2 управления.

После выполнени ; операции Считывание байт слова с выходов разрядного блока 11 выбранного блока 1 поступает на вход 8 блока 2.

Технико-экономическое преимущество предлагаемого устройства заключа-: ется в снижении потребляемой устройством мощности, которое составляет около ЗОВ.

Формула изобретения

Оперативное запоминающее устройство, содержащее блок управления, источник питания и блоки памяти, каждый из которых состоит из накопителя, первый. вход которого соединен с выходом формирователя адресных токов, а выход и второй вход накопителя соединены с одними из входов и выходов разрядного блока, другие входы и выходы которого соединены

1соответственно с первыми выходами распределителя импульсов и первого коммутатора, выходами второго коммутатора, информационными выходами и входами блока управления, входы формирователя адресных токов соединены соответственно с одним из адресных выходов блока управления, с вторыми выходаии распределителя импульсов и первого коммутатора, третий выход которого соединен с первым входом распределителя импульсов, первые входы коммутаторов и шифратора соединены с первым выводом. источника питания, второй вход второго коммутатора соединен .с третьим выходом распределителя импульсов, второй вывод источника питания подключен к третьему входу второго коимутатора, второй вход распределителя импульсов подключен к первому выходу шифратора, третий вход распределителя импульсов и второй вход шифратора соединены соответственно с выходом Обращение блока управления и с другим адресньва выходом блока управления, о т л и— ч а ю щ е е с я тем, что, с целью снижения потребляемой устройством мощности, в каждый блок памяти введены элемент задержки, усилитель, элемент ИЛИ, триггер и элемент И, первый и второй входы которого подключены соответственно к второму выходу,шифратора и выходу элемента задержки, первые входы элемента задержки и элемента ИЛИ подключены к входу Обращение блока управления, .второй вход элемента ИЛИ соединен с четвертью выходом распределителя импульсов, выход элемента И соединен с первым входом триггера, второй вход которого соединен с выходом

970462 элемента ИЛИ, выход триггера подклю-; чен к первому;выходу усилителя, вы:ход которого соединен с вторым входом первогЬ коммутатора, вторые .входы элемента эадераки и усилителя и третьи входы триггера, элементов И и ИЛИ соединены с первым выводом источника питания.

Источники информации, принятые во внимание при экспертизе

1. Запоминающие устройства современных ЭЦВИ. Под ред. А.A. Крупского, N., Мир, 1968, с. 155-160.

5 2. Авторское свидетельство СССР. Р 636677, кл.» Q 11 С 11/00, 1977 (прототип) .

970462

НС5Р J

Составитель В. Рудаков

Редактор А. Власенко ТехредЛ.Пекарь Корректор й. Демчик

Заказ 8397/64 Тираж 622 . Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4