Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<п>970465 (61) Дополнительное к авт. свид-ву(22) Заявлено 23.04. 81 (21) 3278023/18-24 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 30.10.82. Бюллетень ¹ 40

Дата опубликованИя описания 30.10.82

151) М. Кп.з

0 11 С 11/00

Государственный комитет

СССР по делам изобретений и открытий

t ($3) УДК 681. 327. б (088.8) (72) Автор изобретения

В.И.Ыепель (71) Заявитель

{54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к промышлен ности средств связи и может быть использовано при построении телевизионной аппаратуры цифровой обработки видеосигналов, например устройств шумодавления, устройств видеоэффектов и др., работающих в вещательном телевизионном стандарте.

Известно устройство памяти с избирательным доступом, содержащее матрицу запоминающих элементов, состоящую из отдельных запоминающих ячеек, выходы которых подключены к входам мультиплексора, выход которого является выходом устройства. Входы запоминающих ячеек подключены квходу устройства. Управляющие входы запоминающих ячеек подключены к выходам устройства адресации, на вход которо.го поданы синхроимпульсы 1 .

Недостатком этого устройства яв- ляется низкое быстродействие. Этот недостаток обусловлен тем, что при подключении входов запоминающих ячеек к входу устройства быстродействие устройства определяется быстродействием ячеек памяти. Реализация запоминающего устройства большого. объема хранимой информации возможна на запоминающих элементах динамическою типа использующих МОП структуры. Такие ячейки памяти не позволят получить требуемое быстродействие запоминающего устройства. Быстродеиствие запоминающего элемента ограничено его входной емкостью.

Наиболее близким к предлагаемому является цифровое запоминающее устройство., содержащее запоминающую матрицу, состоящую иэ запоминающих ячеек, выходы которых подключены к входам мультиплексора, выход которого является выходом устройства. Входы запоминающих ячеек подключены к вы15 ходам регистра. Входы регистра соединены с выходами демультиплексора, вход которого является входом устройства. Управляющие входы запоминающих ячеек подключены к первому выходу

2О.устройства управления, на вход которого поданы синхроимпульсы. Второй выход устройства управления соединен с тактовым входом регистра. На вход ,устройства управления и на управляю25 щие входы демультиплексора и мульти-. плексора выданы синхросигналы L2f.

Недостатком этого устройства яв.ляется низкое быстродействие. Этот недостаток обусловлен тем, что при подключении выходов запоминающих яче970465 ек ко входам мультиплексора в режиме считывания, быстродействие снижается за счет задержки вывода информации на время, определяемое скоростью поиска требуемого запоминающего элемента запоминающих ячеек. На выходе 5 мультиплексора считываемая информация появляется через интервал време- ни, определяемый временем поиска адреса требуемого запоминающего элемента и временем задержки считывания информации, что приводит к низкому быстродействию устройства.

Цель изобретения — повыыение быстродействия запоминающего устройства.

Поставленная цель достигается тем,ig что в запоминающее устройство,. содержащее матричный накопитель, демультиплексор, выходы которого подключены к соответствующим входам регистра, блок управления, первый вход которого подключен к управляющим входам ячеек памяти накопителя, а второй — к тактовому входу регистра, мультиплексор, выход которого является выходом уст - ройства, вход блока управления,мультиплексора и один из входов демультиплексора являются входом синхронизации устройства, а другой вход демультиплексора является информационным входом устройства, введен дополнител ный регистр, выходы которого подключены к соответствующи.и входам мультиплексора, при этом информационные входы каждои пары ячеек памяти накопителя объединены и подключены к соответствующим выходам регистра, а 35 выходы упомянутых пар ячеек памяти объединены и подключены к соответствующим входам дополнительного регистра, тактовый вход которого подключен ко второму входу блока управления. 4П

Каждая ячейка памяти накопителя содержит запоминающие элементы,. информационные входы которых объединены и являются входом ячейки памяти, выходы запоминающих элементов объеди-4 иены и являются информационными -выходами ячейки памяти, Вхо управления запоминающих Элементов подключены к соответствующим выходам де ифратора, вход которого является управляющим входом ячейки памяти.

Блок управления содержит счетчик, вход которого является входом синхронизации устройства, сумматор, вход которого подключен к выходу счетчи -а, а выходы сумматора и счетчика являются соответственно первым и вторым выходами блока управления.

Такое построение предлагаемого устройства позволяет повысить быст- 60 родействие за счет того, что в процессе обращения к первой запоминающей ячейке производится запись в и запоминающий элемент, а считывание производится из и+2 запоминающего элемента, причем информация переносится в дополнительный регистр, где производится промежуточное хранение этой информации. В следующий период обращение производится н второй запоминающей ячейке, причем производнтся запись в и-1 запоминающий элемент, а считывание из и+1 запоминающего элемента (A2, б, 10, 14...). Таким образом, в дополнительном регистре информация, подлежащая выводу, появляется до начала считывания, т.е. производится компенсация времениг необходимого для поиска требуемого запоминающего элемента. При поступлении команды считывания информация считывается не из запоминающих элементов, а из дополнительного регистра и переносится в мультиплексор выход которого является выходом устройства. При этом задержка вывода информации определяется не временем поиска адреса и вывода информации из запоминающего элемента, а только быстродействием дополнительного регистра.

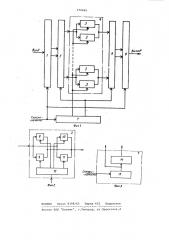

На фиг.1 представлена структурная схема запоминающего устройства, на фиг.2. — структурная ахема ячейки памяти запоминающего устройства, на фиг.3 - структурная схема блока уп равления запоминающего устройства.

Запоминающее устройство содержит демультиплексор 1 (фиг.1), вход которого является входом устройства, а выходы соединены с соответствующими входами регистра 2. К каждому выходу регистра 2 подключены два входа ячеек 3 памяти накопителя 4. Выходы каж", дых двух ячеек 3 памяти подключены к соответствующему входу дополнительного регистра 5, выходы которого соединены с входами мультиплексора б. Выход мультиплексора б является выходом устройства. На тактовые входы демультиплексора 1, мультиплексора б и блока 7 управления поданы синхросигналы от синхрогенератора. Первый выход блока 7 управления подключен к управляющим входам ячеек 3 памяти.

Ячейка 3 памяти (фиг.2) состоит из запоминающих элементов 8-11, входы которых подключены к входу ячейки 3 памяти. Выходы запоминающих элементов

8- 11 подключены к выходу ячейки 3 памяти. Управляющие входы запоминающих элементов 8- 11 подключены к соответ-. ствующим выходам дешифратора 12, вход которого подключен к управляющему входу ячейки памяти 3. Запоминающие элементы 8-11 выполнены, например, в виде МОП-прибора, хранение информации в котором происходит на емкости затвора.

Блок 7 управления (фиг.3) состоит из двоичного счетчика 13, выполненнЬ го, например, на последовательно

970465.!(прототип). включенных триггерах. На вход счетчика 13 поданы синхросигналы. Выход счетчика 13 подключен к входу сумматора 14. Выход сумматора 14 подключен к первому выходу блока 7 управления, ко второму выходу которого подключен выход счетчика 13.

Предлагаемое устройство работает следующим образом.

На вход демультиплексора 1 посту,пает цифровая информация. На выходах (демультиплексора 1 информация разде ляется на ряд каналов, которая переносится в регистр 2, производящий промежуточное хранение поступающей информации. С выходов регистра 2 информация поступает в ячейки 3 памяти накопителя 4. На тактирующие входы демультиплексора 1, мультиплексора б и на вход счетчика 13 блока 7 управления поступают синхросигналы от синхрогенератора. Сигналы управления в виде кодовых комбинаций поступают с выхода счетчика 13 блока 7 управления на тактирующие входы регистра 2 и дополнительного регистра 5, а также на вход сумматора 14. Сигналы управления c,íûõoäà сумматора 14 блока управления 7 поступают на входы дешифраторов 12 ячеек памяти 3. На вы-. ходах дешифратора 12 ячейки 1 памяти формируются сигналы управления запоминающими элементами 8-11. Поступающая на вход ячейки 3 памяти информация записывается и считывается в том запоминающем элементе 8-11, на управляющий вход которого поступил сигнал управления с соответствующего выхода дешифратора 12 ячейки 3 памяти. Сигнал с выхода запоминающего элемента

8 <9-11) поступает на выход ячейки

3 памяти накопителя 4. С выходов каж-: дой пары ячеек 3 памяти оигналы поступают на соответствующие входы дополнительного регистра 5, в котором происходит хранение информации до поступления команды считывания из запоминающего устройства. После поступления команды "Считывание" хранимая в дополнительном регистре 5 информация поступает на входы мультиплексора б, выход которого является выходом устройства. Команды управления, формируемые на выходах дешифратора.

Использование предлагаемого цифрового. запоминающего устройства позволит вести разработку надежной и быстродействующей аппаратуры цифровой обработки видеосигнала. Примене-.. ние цифрового запоминающего устройства позволит использовать динамические

МОП запоминающие элементы, которые не обладают требуемым быстродействием. Однако пЬ сравнению с другими типами запоминающих .элементов они обладают в 10 раз меньшей мощностью потребления, прострй технологией прс . иэводства (3 технологические операции), и в 4 раза большей степенью интеграции. Промышленное проиэводсгво предлагаемого устройства не требует дефицитных материалов и может быть реализовано с использованием серийно выпускаемых комплектующих иэделий. формула изобретения

1. Запоминающее устройство, содер10 жащее матричный накопитель, демультиплексор, выходы которого подключены к соответствующим входам регистра, блок управления, первый вход котброго подключен к управляющим входам

f5 ячеек памяти накопителя, а второй к тактовому входу регистра, мультиплексор, выход которого является выходом устройства, вход блока управления, мультиплексора и один иэ входов демультнплексора являются входом синхронизации устройства, а другой вход демультиплексора является информационным входом устройства, о т л и ч аю щ е е с я тем, что, с целью ïîâûшения быстродействия устройства, оно содержит дополнительный регистр, выходы которого подключены к соответст" вующим входам мультиплексора, при этом информационные входы каждой пары ячеек памяти накопителя объединены и подключены к соответствующим вйходам регистра, а выходы упомянутых пар ячеек памяти объединены и подклю= чены к соответствующим входам дополнительного регистра, тактовый вход

35 которого подключен к второму входу блока управления.

2. Устройство по г..1, о т л и ч а ю щ е е с я тем, что ячейка памяти накопителя содержит запоминаю-

40 щие элементы, информационные входы которых объединены и являются входом ячейки памяти, выходы запоминающих элементов объединены и являются информационными выходами ячейки памя45 ти, входы управления запоминаюцих элементов подключены к соответствующим выходам дешифратора, вход которого является управляющим входом ячейки памяти. .50 3. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что блок управления содержит счетчик, вход которого является входом синхронизации устройства, сумматор, вход которого подключен к выходу счетчика, а выходы сумматора и счетчика являются соответственно первым и вторым выходами блока управления.

Источники информации, принятые во внимание при экспертизе

О 1. Заявка Франции Р 2379133, кл. G 11 С 11/34, опублик. 1979.

2. Кривошеев M.H. Цифровое телевидение. М., "Связь", 1980, с. 122-128