Запоминающее устройство с обнаружением и исправлением ошибок

Иллюстрации

Показать всеРеферат

О П И С А Н И E

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик

lu>970475 (6!) Дополнительное к авт. свид-ву (22) Заявлено 04.12. 80 (21) 3253836/18-24 с присоединением заявки Йо— (23) Приоритет—

Опубликовано 3010.82. Бюллетень Hо 40

Дата опубликования описания 3Q1082 Ù М. Nn.

G 11 С 29/00

Государственный комитет

СССР по делам изобретений и открытий

{53) УДК 681.327 (088.8) (72) Авторы изобретения

И.Л.Касиян и В.С.Кейбаш (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ

И ИСПРАВЛЕНИЕМ ОШИБОК

Изобретение относится к запоминающим устроиствам.

Известно запоминающее устройство, содержащее главную память, блок контроля данных и дополнительную память, где неисправные ячейки главной памяти обнаруживаются блоком контроля данных, который присваивает им адреса замещения в дополнительной памяти, причем обращение по этим адресам происходит каждый раз при обращении к соответствующим ячейкам главной памяти, а использование данных на выходе главной и дополнительной памяти определяет вентильная схема в зависимости от адресного обращения к работающей или неисправной ячейке главной памяти (1 7.

Недостатком этого устройства является низкая надежность, вследствие одновременного обращения к главной и дополнительной памяти при отказе ячейки главной памяти и отсутствия контроля и защиты данных, запомненных в дополнительной памяти, а так-. же увеличение затрат машинного времени вследствие одновременного обращения к главной и дополнительной памяти.

Наиболее близким к изобретению является запоминающее устройство с контролем данных, содержащее блок управления, арифметический блок, блок обнаружения и коррекции ошибок, первый, второй и третий регистры, причем вход блока обнаружения и коррекции ошибок соединен со входом устройства, первый выход — с первым входом третьего регистра, второй выход — со входом блока управления и первым входом арифметического блока, второй вход которого подключен к первому выходу блока управления, третий вход: - к выходу третьего регистра, первый выход — ко входу первого ре-, гистра, выход которого соединен с первым вьходом устройства ) 27.

Недостатками этого устройства являются низкая его надежность в связи с необходимостью проведения коррекции одной и той же ошибки при каждом обращении по адресу, содержащему ошибку, и кроме того, увеличенные затраты машинного времени. Цель изобретения — повышение надежности запоминающего устройства.

Поставленная цель достигается тем, что в запоминающее устройство с обнаружением и исправлением ошибок;

970475 со в — îðûìè входами счетчика циклов, с -летчика ошибок и селектора, второй выхоц формирователя сигналов блокировки подключен к первому входу фор.— ирователя сигналов записи, второй вход которого соединен с выходом первого буферного регистра, а выход подключен к другому входу накопителя, выходы второго и третьего буферных регистров и счетчика циклов соецинены соответственно со входами формирователя сигналов блокировки и другими Входами блока местного управления.

Блок местного управления содер;.,ит элемент И, первый формирователь адресных сигналов и последовательно соединенные второй формирователь адресных сигналов, счетчик адреса, накопитель, регистр микрокоманд и дешифратор, причем выходы регистра микрокоманд соединены со входами второго формирователя адресных команд, управляющий вход счетчика адреса подключен к выходу элемента И, одни из вых",дев дешифратора соединены с од55 содержащее регистр адреса, накопитель, выходной регистр, блок обнаружения ошибок, буферные регистры и арифметический блок, причем выходы регистра адреса подключены к одним из входов накопит еля, информационные выходы которого подключены ко входам выходного регистра, первый выход которого сое,цинен с первым входам блока обнаружения ошибок, одни из входов арифметического блока подключены соответственно ко второму выходу выходного регистра и выходам буферных регистров, первые входы которых соединены с первым выходом блока обнаружения ошибок, один из выходов арифметического блока соединен со вторым входом первого буферного регистра, введены селектор, счетчик ошибок, счетчик циклов, блок местного управления, формирователь сигналов блокировки и формирователь curíал0в записи, причем первый вход селектора соединен со вторым выходом блока обнаружения ошибок, второй вход которого подключен к одному из выходов счетчика ошибок, другие выходы которого соединены со вторыми входами второго и третьего буферных регистров, входы регистра адреса подключены к первым выходам селектора, блока местного управления и формирователя сигналов бАокировки,второй и третий выходы селектора соединены соответственно с первым входом счетчика ошибок и одним из входов блока местного управления, второй вы-35 ход которого соединен с первым входом c÷åò÷èêà циклов, третий выход блока местного управления подключен к другому входу арифметического блока,. другой выход которого соединен ними иэ входов формирователей адресных сигналов, другие выходы дешифратора и выходы первого формирователя адресных сигналов являются выходами блока, входами которого являются входы элемента И и первого формирователя адресных сигналов и один из входов счетчика адреса.

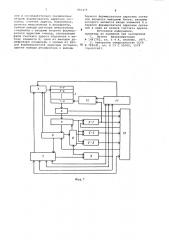

На фиг.1 изображена структурная электрическая схема запоминающего устройства с обнаружением и исправлением ошибок, на фиг.2 — структурная электрическая схема блока местно го управления.

Устройство (фиг.1) содержит накопитель 1, состоящий из нескольких зон 1-1, 1-2, 1- и (где п - целое число), одна из которых резервная, регистр 2 адреса, выходной регистр

3, блок 4 обнаружения ошибок, первый

5-1, второй 5-2 и третий 5-3 буферные регистры, селектор б, блок 7 местного управления, счетчик 8 ошибок, счетчик 9 циклов, арифметический блок 10, формирователь 11 сигналов блокировки, формирователь 12 сигналов записи.

Блок 7 местного управления (фиг. 2) содержит первый формирователь 13 адресных сигналов, элемент И 14, второй формирователь 15 адресных сигналов, счетчик адреса 16, накопитель

17, регистр 18 микрокоманд и дешифратор 19.

Формирователь 13 содержит, в свою очередь, элементы И 20, элементы ИЛИ

21 и элементы И 22.

Устройство работает следующим образом.

Накопитель 1 выполнен в виде нескольких зон 1-1, 1-2, 1-п, каждая из которых содержит определенное число слов и имеет контрольный код, запомненный по фиксированному адресу, а по разрядам контрольных кодов в свою очередь определяется их контрольный код и также запоминается по фиксированному адресу.

Одна из зон памяти выполнена резервной, емкость резервного поля памяти определяется по интенсивности отказов элементов памяти и периода машинного времени между вмешательствами извне (например, замена отказавших элементов при технологических обслуживаниях) или всего требуемого фонда машинного времени, если вмешательства извне невозможны.

При отсутствии ошибки в считанном слове блок 4 обнаружения ошибок не возбуждается, и слово с выходного регистра 3 через арифметический блок

10 поступает по назначению программы.

При обнаружении ошибки в считанном слове блок 4 запоминает адрес ошибочного слова в регистре 5-2 и передает управление селектору Е, который принимает решение о к:и кте—

970475 ре ошибки — сбой или отказ, например, многократным считыванием.

В случае отказа селектор 6 устанавливает счетчик 8 ошибок в положение

"один" и передает управление блоку 7, который осуществляет считывание контрольного кода именно той зоны памяти, где произошел отказ, помещает его в регистр 5-1, устанавливает содержимое счетчика 9 циклов 4, равное числу слов зоны (0), и лоочередно н по- IO рядке возрастания (убывания) считывает все слова зоны.

Арифметический блок 10 вычитает содержимое выходного регистра 3 из содержгмого регистра 5-1 и результат f5 помещает в регистр 5- 1. Перед чтением слова арифметический блок 10 сравнивает адрес слова с содержанием регистра 5-2 (адрес ошибочного слова) и в случае их совпадения изменяет адрес очередного слова на единицу н порядке возрастания (убывания) адресов. Таким обРазом, обращение по адресу ошибочного слова не происходит. Содержимсе советчика 9 циклов 25 изменяется в порядке убынания (возрастания) и при считывании всех слов н зоне и их вычитании из контрольного кода в регистре 5-1 находится правильное значение ранее ошибочного считанного слова, т.е. восстановленное слово. При этом по содержимому счетчика 9 циклов управление передается формирователю 11, который через формирователь 12 разрешает запись содержимого регистра 5-1 (восстановленного слона) в резервной зоне памяти, присваивает ему адрес отказавшего слова, блокирует дальнейшее обращение по отказавшему адресу í зоне памяти и передает управление при- 40 остановленной программы.

В случае обнаружения ошибок при считывании одного иэ контрольных кодов, селектор 6 точно также определяет характер ошибки — сбой или отказ, 45 и н случае отказа устанавливает счетчик 8 ошибок в состояние "два" ошибка в контрольном коде, адрес ошибочного контрольного кода при этом запоминается в регистре 5-3, и 5О передает управление блоку 7. Последний организует точйо такой же процесс, с отличительной разницей считывания контрольного кода контроль-. ных кодов и устанавливает счетчик 9 циклов равным числу контрольных кодов. После носстанонления контрольного кода счетчик 8 ошибок устанавливается в состояние "один", счетчик

9 циклов равным числу слов и зоне (О), и выполняется процесс носстанонления слова.

Технико-экономическое преимущество предлагаемого устройства состоит в том, что оно способ:o исправлять столько обнаруженных ошибочных слов, 65 сколько их можно запомнить в резернной зоне памяти.

Формула изобретения

1. Запоминающее устройство с Обнаружением и исправлением ошибок, содержащее регистр адреса, накопигель, выходной регистр, блок обнаружения or:.èáoê, буферные регистры и арифметический блок, причем выходы регистра адреса подключены к одним иэ входов накопителя, информационные выходы которого подключены к входам выходного регистра, первый выход которого соединен с первым входом блока обнаружения ошибок, одни из вхо дов арифметического блока подключены соответственно к второму выходу выходного регистра и выходам буферных регистров, первые входы которых соединены с первым ныходом блока обнаружения ошибок, один иэ выходов арифметического блока соединен с вторым входом первого буферного регистра,отличающееся тем, что, с целью повышения надежности, н него введены селектор, счетчик ошибок, счетчик циклон, блок местного управления, формирователь сигналов блокировки и формирователь сигналов записи, причем первый вход селектора соединен с вторыми выходом блока обнаружения ошибок, второй вход которого подключен к одному из выходов счетчика ошибок, другие выходы которого соединены с вторыми входами второго и третьего буферных регистров, входы регистра адреса подключены к первым выходам селектора, блока местного управления и формирователя сигналов блокировки, второй и третий выходы селектора соединены соответ— ственно с первым входом счетчика ошибок и одним из входов блока мест ного управления, второй выход которого соединен с первым нходом счетчика циклов, третий выход блока местного управления подключен к другому входу арифметического блока, другой выход которого соединен с вторыми входами счетчика циклов, счетчика ошибок и селектора, второй выход формирователя сигналов блокировки подключен к первому входу формирова.-, теля сигналов записи, второй вход которого соединен с выходом первого буферного регистра, а выход подключен к другому входу накопителя, выходы второго и третьего буферных регистров и счетчика циклов соединены соответственно с входами формир< вателя сигналов блокировки и другими входами блока местного управления.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок местного управления содержит элемент И, первый формирон ател ь адрес ных си гна970475 лов и последовательно соединенные второй формирователь адресных сигналов, счетчик адре са, накопитель, регистр микрокоманд и дешифратор, причем выходы регистра микрокоманд соединены с входами второго формирователя адресных команд, управляющий вход счетчика адреса подключен к выоду элемента И, одни из выходов дешифратора соединены с одними из входов формирователей адресных сигналов, 10 другие выходы дешифратора и выходы первого формирователя адресных сигналов являются выходами блока, входами которого являются входы элемента И и первого формирователя адресных сигналов и один иэ входов счетчика адреса.

Источники информации, принятые во гнимание при экспертизе

1. Патент Великобритании

Р 1 491702, кл. G 4 А, опублик. 1977.

2. Авторское свидетельство СССР

М 769641, кл..G 11 С 29/00, 1979 (прототип).

Составитель В.Рудаков

Редактор A.Âëàñåíêî Техред A.A÷ Корректор М.Шарснли

Заказ 8398/65 Тираж 622 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

133035, Москва, E-35, Раушская наб., д.4/5

Филиал ППП. "Патент", г.ужгород, ул.Проектная, 4