Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик

«s>970478 (61) Дополнительное к авт. свид-.ву(22) Заявлено 15. 04 ° 81 (21) 3275293/18- 24 (ф jМ Кд 3 с присоединением заявки ¹6 11 С 29/00

Государственный комитет

СССР но делам изобретений и открытий (23) ПриоритетОпубликовано301082. Бюллетень № 40

Р31УДК 681.327 (088. 8) Дата опубликования описания 301082

В.С.Борисов, A.Â.Êóçíåöîâ, Б.С.Цыбак (72) Авторы изобретения (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

Изобретение относится к запоминающим устройствам (ЗУ).

Известно запоминающее устройство с самоконтролем, содержащее основной и резервный накопители, блок постоянной памяти, блоки переадресации Щ.

Основным недостатком этого устройства является необходимость программирования блока постоянной памяти в процессе производства.

Наиболее близким техническим решением к изобретению является ЗУ, содержащие накопитель, соединенный с входным и выходным регистрами, элементы И и схемы сравнения.

Принцип работы этого ЗУ состоит в следующем.

Каждое слово сразу же после его записи в накопитель по заданному адресу считывается в выходной регистр и поступает на устройство обнаруже- ния ошибок. При отсутствии ошибок или их необнаружении цикл записи заканчивается ° При обнаружении ошибок запи-. санное в накопитель слово инвертируется (заменяется на дополнение), факт инверсии слова обозначается записью.

"1" в специальном разряде записываемого слова, на этом цикл записи за-.канчивается.

При выборке считанное из накопителя слово инвертируется, если в его индикаторном разряде оказывается символ "1" и не инвертируется, если "0".

Таким образом, исправление двоичных постоянных отказов (дефектный запоминающий элемент. ЗЭ постоянно находится в состоянии "0" или "1" независимо от того, что в него записывается) основано на предложении, что обрабатываемая информация, представленная в инверсной форме, не содержит ошибок (2).

Недостатком этого ЗУ является то, что большая часть постоянных отказов кратности 2 и выше, то есть групповых, в ячейках накопителя не корректируется и приводит к ошибкам считываемой информации. Это снижает надежность устройства.

Цель изобретения — повыаение надежности ЗУ, а именно обеспечение безошибочных режимов, записи, хранения информации в накопителе, любое слово которого имеет до 1 t w 3 смеж ных дефектов указанного выше типа, Поставленная цель достигается тем, что в запоминающем устройстве с самоконтролеи, содержащее накопитель, 970478

4 адресный блок, входной и выходной регистры, схемы сравнения и элементы И, причем одни входы накопителя подключены к выходам адресного блока, другие — к выходам входного регистра, а выходы накопителя соединены со входами выходного регистра,i-е по модулю t выходы входного и выходного регистров соединены со входами

i-й схемы сравнения (где i 0 1,..., -1, а t - число смежных дефектных 1Q запоминающих элементов в ячейке памяти накопителя), выход которой подключен к i-м по модулю t счетным входам входного регистра, à j-й выход выходного регистра соединен с одним из входов j-oro элемента И, другой вход которого является управляющим, а выход подключен к j-м по модулю t счетным входам выходного регистра (где j 0, 1, ..., t-1).

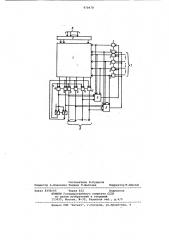

На чертеже изображена функциональная схема запоминающего устройства. устройство содержит накопитель 1, адресный блок 2, входной регистр 3, выходной регистр 4, схему 5 сравнения элементы И(,6.

Запись информации происходит следующим образом.

Двоичное кодовое слово х=(х,... х„); Х ° =0,1; 1 i Ф и длины и, йервые

t компонент которого равны нулю, а остальные 1 =и-t являются информационными, записывается во входной регистр 3, через вход 7 последнего. Из входного регистра 3 слово переписыва-35 ется в накопитель 1 по. заданному адресу, поступающему на вход 8. После этого осуществляется контрольное считывание слова из накопителя 1 н вы-, ходной регистр 4. Слово x =(x,...õ„)

1 х> =0,1, поступающее в выходной регистр 4, может отличаться от исходного слова из-за сбоев и отказов.

После контрольного считывания н ныходной регистр 4 в 1-й схеме 5,сравнения (l 1,...,t) происходит поразрядное сравнение символов х.1 и хдля всех i- 1„ 1 +t< 1 +2t, ... Если хотя бы для одной такой пары символов х(/х„, то все компоненты кодового

I слова х с номерами .i=1„1 at, 1+2t,..... иннертируются путем посылки единицы с выхода 1-й схемы 5 сравнения на соответствующие счетные входы

l входного регистра 3. Если х„.=х(для всех 1=1,, 1+й 1л2с, то эта группа ком-55 понент слова х с номерами i= i< 1+t<-14

+2 t не инвертируется. Эта операция ныполняется параллельно всеми 1 схе" мами 5 сраннения, После ее завершения новое кодовое слово у=(у,...у ) 60 у =0,1, сформированное во входном регистре 4, переписывается н накопитель 1 по тому же адресу. Заметим, что при наличии не более с смежных постоянных дефектов в и-разрядной,65 ячейке памяти накопителя и отсутствии случайных сбоев при записи и считывании кодовое слово у будет хранить ся н ЗУ без ошибок.

При считывании слово у из ячейки накопителя 1 с заданным адресом,нак обычно, считывается в выходной регистр 4, после чего. по первым t символам слова у осуществляется .восстановление исходного слова. Для этого tj-й контрольный символ у () 1,t)

Ф через элемент И 6 подается на счетные входы выходного регистра 4 с номерами j, j t j 2t;... Если у. l, а это имеет место только в тех случаях, когда при записи символы х. слова х с номерами j, j t, j 2t,. ° . были инвертиронаны, то символы считанного из накопителя слова у с номерами J

jet j +2t,... повторно инвертируются.

Таким образом, после выполнения указанных выше инверсий для всех j=

2,...,t в выходном регистре 4 оказывается исходное слово х, последние К символов которого являются ин.формационными и направляются на выходы 9 устройства.

Предлагаемое запоминающее устройство отличается повышенной нн1дежностью, так как в нем осуществляется предварительный контроль числа ошибок, возникающих из-за отказов и сбоев в ячейках памяти запоминающего устройства.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, адресный блок, входной и выходной регистры, схемы сравнения и элементы и, причем одни входы накопителя подключены -к выходам адресного блока, другие - к выходам входного регистра, а выходы накопителя соединены с входами выходного регистра, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в

НЕМ 1 -Е По модулю 4 выходы входного и выходного регистров соединены с входами 1-й схемы .сравнения (где

О, 1, ..., t-1, а 4- число смежных дефектных запоминающих элементов н ячейке памяти накопителя), выход которой подключен к i-м по модулю 1 счетным входам входного регистра, а

j-выход выходного регистра соединен с одним из входов -го элемента И, -другой вход которого является управляющим, а выход подключен к 1-м по модулю Ф счетным входам выходного регистра где 3 =О, 1, ..., -1

Источники информации, принятые во внимание при экспертизе

1. "Электроника", 9 2, 1980, с.3843»

2. Патент CItlA 9 3768071, кл. 340-146.1, опублик. 1973 (прототип).

970478

Составитель В.Рудаков

Редактор A.Âëàñåíêî Техред T.Ìàòo÷êà Корректор, И. Шароши

Заказ 8398/65 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4