Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

OrlИСAnHE

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик

< «970479 (61) Дополнительное к авт. свид-ву(22) Заявлено20.04.81 (21) 3276987/18-24

Р1 М К з с присоединением заявки ¹G 11 С 29/00

Государственный комнтет

СССР по делам нэобретеннй н открытнй (23) ПриоритетОпубликовано 30.1082. Бюллетень ¹40 (Щ УДК681. 327 (088 .8) Дата опубликования описания 301082 (72) Авторы изобретения

В.Н.Горшков и В.В.Воронов (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ

КОНТРОЛЕМ

Изобретение относится к запомина ющим устройствам.

Известно запоминающее устройство с автономным контролем, содержащее адресный блок памяти, соединенный с первым ассоциативным блоком памяти, второй ассоциативный блок памяти, один из входов которо:о соединен с первым входом адресного блока памяти, блок управления, выходы которого подключены к управлякядим входам ассоциативных блоков памяти P1).

Недостатками этого устройства являются сложность и малая информационная емкость.

Наиболее близким техническим решением к изобретению является запоминающее устройство с автономным конт ролем, содержащее адресный блок памяти, соединенный с первым ассоциативным блоком памяти, второй ассоциативный блок памяти, один иэ входов которого соединен с первым входом адресного блока памяти, блок управле ния, выходы которого подключены к управляющим входам ассоциативных блоков памяти, первый коммутатор, входы которого подключены соответственно к первому выходу блока деыифратора и к выходу адресного блока памяти, а выходы — к другим входам второго ассоциативного блока памяти, выходы которого- соединены Со входом блока дешифратора и одним из входов второго коммутатора, др;гой вход которого подключен к выходу блока дешифраторов, а выход — ко входу адресного блока памяти (2 1.

10 Недостатком этого устройства является то, что при отказах разрядов ячеек адресного блока памяти необходимо запоминать во втором ассоциативном блоке памяти номера отказавших разрядов и значения соответствующих им информационных сигналов, что приводит к увеличению объема второго ассоциативного блока памяти,.т.е. к усложнению устройства и снижению

его информационной емкости.

Цель изобретения — упрощен ие устройства.

Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее ад25 р сный накопитель, уси ители, реги. р

Слова, регИстр адреса, дешифраторы, блок управления и ассоциативные накопители, управляющие входы которых соединены с выходами блока управле-ния, а адресные входы — с входами

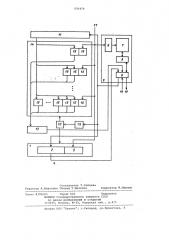

970479 регистра адреса, выходы которого подключены к адресным входам адресного накопителя, информационные входы и выходы которого соединены с одними из выходов и входов усилителей, другие входы и выходы которых подключены к 5 одним из информационных выходов и входов регистра слова, первый управляющий вход которого соединен с выхо;, дом первого ассоциативного накопите- ля, выходы второго ассоциативного на-)Q копителя подключены к входам дешифратора, вход блока управления является управляющим входом устройства, введены шифраторы и пороговый элемент, входы которых соединены с другими ин-15 формационными выходами регистра сло-, ва и информационными входами первого ассоциативногЬ накопителя, причем выходы шифраторов подключены к .информа< ционным входам второго ассоциативного накопителя, выходы дешифраторов сое-. динены с -вторым управляющим входом регистра слова, а выход порогового элемента является управляющим выходом устройства. на чертеже приведена электрическая схема устройства.

Устройство содержит первый ассоциа тивный накопитель 1 с информационной

;частью 2, адресной частью 3, выходоМ 4 и управляющим входом,5 регистр б . 30 адреса, адресный накс@итель 7, регистр 8 слова, выполненный на триггерах со счетным входом, y<ãèëèòeëè 9, блок 10,управления, шифраторы 1э1, дешифраторы 12, пороговый элемент . 35

13, второй ассоциативный накопитель

14 с приэнаковой частью 15 и адресной частью 16, предназначенных соответственно для записи номеров отка- ° завших разрядов и адресов отказавщих 4 ) ячеек памяти адресного накопителя.

На чертеже обозначены адресные 17 и информационные 18 входы и .информационные выходы 19 устройства.

45 устройство работает следующим образом.

Выявление разрядов, в которых эаписываемая информация не совпадает с характером отказа, производится во время записи информации в адресный накопитель 7. При этом адрес, поступающий на вход 17, записывается .в адресную часть 3 накопителя 1. За-,, писываемое слово со входа 18 поступат в регистр 8 и заносится в накопитель 7 через усилители 9 и в информа<-" ционную часть 2 накопителя 1. Затем производится считывание записанного слова (с.-восстановлением информации) из накопителя 7 на регистр 8. Если в 60 ячейке накопителя 7 по адресу, установленному на входе 17, нет отказов, или характер всех отказов совпадает с записываемой информацией, то во всех разрядах регистра 8 будет нулевой код. При этом содержимое информа ционной части 2 накопителя 1, соответствующее адресу на входе 17, и сам адрес из адресной части 3 стира ются. На вход 17 подается адрес следующей ячейки, аналогично производит .ся запись нового слова.

Если в ячейке накопителя 7 по адт ресу, установленному на входе 17,,есть отказы, характер которых не совпадает с записываемой информаци,,ей, то в соответствующих разрядах регистра 8 будет единичный код. Кол+ чество таких разрядов назовем кратсностью ошибки и обозначим через у

Далее возможны два случая.

Если ф,у Д вЂ (где n - -количество разрядов слова, записываемого в адресный накопитель 7), то на выходе порогового элемента 13 выдается еди;ничный сигнал, поступающий в блок 10, который блокирует стирание содержи", мого в накопителе 1, соответствующего .адресу, установленному на входе 17, <т.е. в накопителе 1 хранятся адрес ячейки накопителя 7:, в которой име-. ютсяаотказы, и слово, предназначенное для записи в эту ячейку.

Еапи P у — „, то ее эыэоде ээе . мента 13 выдается нулевой сигнал, :поступающий в блок 10. При этом блоМ

10 вырабатывает управляк<щий сигнал, :по которому содержимое информацион-. ,"ной,части 2, соответствующее адресу

<<на входе 17, и сам адрес из адресно@ части 3 накопителя 1, стираются. Од:новременно в адресную часть 16 накопителя 14 записывается адрес, посту" пающий на вход 17, а через шифратор

11 в признаковую часть i3 заносятся ,номера отказавших разрядов накопите-, ля 7, характер отказов в которых не, совпадает с записываемой в них информацией.

При считывании информации из запоминающего устройства по адресу, ус- .тановленному на входе 17, происходит. .одновременное обращение как к накопителю 7, так и к ассоциативным накопителям 1 и 14. Если адрес считы.ваемого слова содержится в накопите-, ле 1, то передача информации в регистр 8 из накопителя 7 Н< произво". дится. При этом содержимое информаци .онной части 2, соответствующее уста" новленному на входе 17 адресу, выда ется на выход 4 и записывается в ре гистр 8. После этого считываемое слово поступает на выход 19.

Если адрес считываемого слова содержится в накопителе 14, то в регистр 8 считывается информация из накопителя 7 через усилители 9. Затем: .содержимое признаковой части 15 на, копителя 14, соответствующее адресу на входе 17, передается в дешифрато ры 12. При этом на выходах дешифраторов 12 формируется единичный код в

970479 тех разрядах, характер откаэон в ко+ торих не совпадает с записываемой в них информацией. Этот код поступает на вход регистра 8 и инвертирует соответствующие разряды. После этого на выход 19 поступает неискаженное слово.

При отсутствии в накопителях 14 и 1 адреса, поданного на вход 17, ироимбдитея СЧитыианиЕ Н регистр-.8 ,информации иэ накопителя 7 через усцлители 9 с последующей выдачей иа выход 19 устройства.

В предлагаемом устройстве сокращается объем памяти ассоциативного накопителя. Необходимый объем приэнаковой части. накопителя более чем в два раза меньше, чем в известном.

Таким образом, технико-зкономическое преимущество предлагаемого ,устройства заключается н его упрощении .по сравнению с известныи.

Формула изобретения

Запоминающее устройство с автономным контролем, содержащее адресный накопитель, усилители, регистр слова, регистр адреса, дешифраторы, блок уп :равления и ассоциативные накопители, ;управляющие входы которых соединены с выходами блока управления, а адресные входы †. с входаии регистра адре.-са, выходы которого подключены к ад- ресныи входам адресного накопителя, информационные входы и выходы которого соединены с одними иэ выходов и входов усилителей, другие входы н ныходЫ которых подключены к одним иэ информационных выходов и входов регистра слова, первый управляющий вхоц которого соединен с выходом первого ассоциативного накопителя, выходы . второго ассоциативного накопителя подключены к входаи дешифратора, вход блока управления является управляюиу6ч входом устройства, о т л и ч а ющ е е с я тем, что, с целью упрощения, в него введены шифраторы и поро13:,гоный элемент, входы которых соеди нены с другими информационными выходами регистра слова и информационными входами первого ассоциативного накопителя, причем ныходы шифраторов

;@ подключены к информационным входам второго ассоциативного накопителя, .

:выходы дешифраторон соединены с вторим управляющим входом регистра ñëîва, а выход порогового элемента яв. ляется управляикцим выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

В 529490, кл. G 11 С 29/00, 1976.

2 ° Авторское свидетельство. СССР

9 744738, кл. G 11 С 29/ОО, 1978 (прототип).

970479

Составитель Т.Зайцева

Редактор A.Âëàñåíêo Техред Т.Маточка

Корректор M.Øàðîøè

Заказ 8398/65 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.Ужгород, Ул.Проектная, 4