Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик

9? 0481 (61) Дополнительное к авт. саид-ву (22) Заявлено 15. 04. 81 (21) 3278750/18-24 с присоединением заявки М(23) ПриоритетОпубликовано 301082. Бюллетень М2 40

Р }М К з

G 11 С 29/00

Государственный комитет

СССР по делам изобретений и открытий (33} УДК .681. 327 (088. 8) Дате опубликования описания 30.1082 (72) Автор. изобретения

И.П.Бурдиян (71) заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ПИЛЯ ТИ

Изобретение относится к запомина ющим устройствам и может быть применено для контроля блоков постоянной памяти.

Известно устройство для контроля блоков памяти, в котором при записи (считывании) информации в оперативное запоминающее устройство формируется контрольный разряд, равный сумме контрольных разрядов адреса и ело" ва, что позволяет обнаружить чтение по неправильному адресу, а также искажение информации(Ц .

Недостатком этого устройства является его сложность. Наиболее близким техническим решением к изобретению является устройство для контроля блоков памяти, содержащее формирователь сигналов регенерации, регистры адреса, блок управления, блок местного управления, триггер, формирователь сигналов записи и считывания, формирователь тестовых сигналов, схему сравнения, регистр числа, блок. останова, элементы И, элемент НЕ и коммутатор (.2 ).

Недостатком этого устройства является ййзкая точность контроля ад-!

Ресной части постоянных запоминаю,щих устройств.

Цель изобретения - повышение точ.ности контроля устройства.

Поставленная цель достигается тем, что в устройство для контроля блоков памяти, содержащее генератор тактовых импульсов, выход которого подключен к первому входу первого элемента И, первый триггер, блок установки эталонов, выход которого соединен с первым входом схемы сравнения, и формирователи импульсов, выходы которых являются управляющими выходами устройства, введены счетчики, второй триггер, блок контроля четности, блоки свертки адреса, вто.Рой и третий элементы И, причем вхо ды первого счетчика подключены к выходу первого элемента И и входам формирователей импульсов, выходы первого счетчика подключены к входам первого блеска свертки адреса и являются адресными выходами устройства, информационными входами которого являются одни из входов блока контроля четности, другой вход которого является контрольным входом устройства и соединен с одним из входов второго .блока свертки адреса, другой вход которого подключен к выходу первого блока свертки адреса, а выход — к

970481

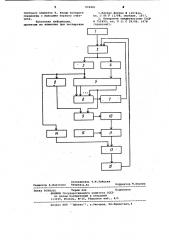

На чертеже представлена функцио(нальная схема. предлагаемого устройства.

Устройство содержит генератор тактовых импульсов, первый элемент И 2, первый счетчик 3, формирователи 4 импульсов, проверяемый блок 5 памяти.

Устройство содержит также блок б контроля четности, первый триггер 7, первый 8 и второй 9 блоки свертки адреса, второй счетчик 10, схему 11 сравнения,,блок 12 установки эталонов, второй 13 и третий 14 элементы

И и второй триггер 15.

Устройство работает следующим об,разом.

Производится пуск генератора 1 (цепи пуска и начальнрго сброса условно непоказаны),и импульсчерез элемент И2 поступает на входысчетчика 3 и

Формирователей, 4, которые формируют по амплитуде и длительности необходимые сигналы управления (обращение, чтение и т,п.) Считанная информация с проверяемого блока 5 контролируется на четность блоком б, При нечетной информации триггер 7 устанавли- 40 вается в 1, и 0 с нулевого выхода триггера 7 поступает на второй вход элемента И 2, при этом происходит останов. Счетчик 3 указывает адрес сбоя. Контрольный разряд, т.е. разряд, дополняющий до четности информацию в блоке 5, поступает на один из входов блока 9, на другой вход которого с выхода блока 8 поступает контрольный разряд адреса, и на выходе блока 9 формируется комби« нированный контрольный разряд. Счет« чик 10,подсчитывает число единиц комбинированного контрольного разря да по всему массиву информации блока

5 памяти. Это число сравнивается схемой 11 сравнения с эталоном, установленным на блоке 12.

Эталон для каждого блока 5 памяти определяется на этапе записи информации в него и представляет собой константу, которую и устанавливают вручную в блоке 12. При считывании информации по последнему адресу из блока 5 на выходе многовходового элемента И 14 появляется 1,кото 6.«

Формула изобретения устройства и соединен с одним из входов второго блока свертки адреса, другой вход которого подключен к вывходу второго счетчика, выход которого соединен с вторым входом схемы сравнения, выход блока контроля четности подключен к входу первого триггера, нулевой выход которого соединен с вторым входом первого элемента

И, третий вход которого подключен к нулевому выходу второго триггера, вход которого соединен с выходом второго элемента И, входы которого подключены соответственно к ьыходу схе- 1О мы сравнения и к выходу третьего элемента И, входы которого соединены с выходами первого счетчика. рая попадается на первый вход элемента И 13.

Если значение счетчика 10 равно эталону, установленному в блоке 12, то на выходе схемы 11 сравнения бу«дет сигнал 0 и триггер 15 не установится в 1, т.е. сбоя нет.

В противном случае сигнал 0 с нулевого выхода триггера 15 поступает на третий вход элемента И 2 и происходит останов, устройства по неисправности адресной части проверяемого блока. Таким образом, устройство, выполняет контроль блока 5 памяти при считывании из него информации на его рабочей частоте в динамическом режиме, что повышает точность контроля.

Устройство особо эффективно при контроле блоков постоянной памяти, контроль адресной части которых в динамическом режиме на рабочей частоте проверяемого блока представляет значительные трудности.

Устройство для контроля блоков памяти, содержащее генератор тактовых импульсов, выход которого подключен к первому входу первого элемента И, первый триггер, блок установки эталонов, выход которого соединен с первым входом схемы сравнения, и формирователи импульсов, выходы которых являются управляющими выходами устройства, о т л и ч а ющ е е с я тем, что, с целью повышения точности контроля, в него введены счетчики, второй триггер, блок контроля четности, блоки свертки адреса, второй и третий элементы И, причем входы первого счетчика подключены к выходу первого элемента И и входам формирователей импульсов, выхбды первого счетчика подключены к входам первого блока свертки адреса и являются адресными выходами. устройства, информационными входами которого являются одни из входов блока контроля четности, другой вход которого является контрольным входом ходу первого блока свертки адреса, а выход — к входу второго счетчика, выкод которого соединен с вторым sxoдом схемы сравнения, выход блока контроля четности подключен к входу первого триггера, нулевой выход которого соединен с вторьм входом первого элемента И, третий вход которого подключен к нулевому выходу второго триггера, вход которого соединен с выходом второго элемента И, входы которого подключены соответственно к выходу схемы сравнения и к выходу

970481

Составитель Т.М. Зайцева

Редактор A.Власенко Техред A.Ач Корректор М.шарси:п1

Закаэ 8398/65. Тираж 622 Подпн сное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, X-35, Раушская наб., 4/5

Филиал ППП Патент, r.Óæãород, ул.Проектная,4.третьего элемента И, входы которого соединены с выходами первого счетчика.

Источники информации, :принятые во внимание при экспертизе

1.Патент Англии 9 1297836, кл, G 06 Р 11/08, опублик. 1977.

2. Авторское свидетельство СССР

М 752499, кл, G 11 С 29/ОО, 1978 (прототип) .