Предоконечный каскад блока управления мощным переключательным транзистором

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (u>970588 (б1) Дополнительное к авт. свид-ву— (22) Заявлено 0804.81 (21) 3270876/24-07 с присоединением заявки М?— (23) Прыоритет—

Опубликовано 30.1082. Бюллетень Ио 40

Дата опубликования описания 301082 () М К 3

Н 02 h1 1/08

Государственный комитет

СССР но делам изобретений и открытий (И} УДК б21.314..572(088.8) И.Г.Фильцер, Г.С.Найвельт и A.Â.Киселев (72) Авторы изобретения

И Г .q Н, " .) 1 К1Ц« ( (71) Заявитель (5 4 ) П РЕДО КОНЕЧНЫЙ КАСКАД БЛОКА УПРАВЛЕНИЯ МОЩНЫМ

ПЕР ЕКЛЮЧАТЕЛЬНЫМ ТРАНЗИСТОРОМ

Изобретение относится к преобразовательной технике и может быть использовано в системах управления тиристорами и транзисторами преобразователей электрической энергии.

Известны устройства для управления тиристором, содержащие усилитель, выходной каскад, резисторы, диоды и кон. денсаторы (1).

Недостатком данных устройств является значительная потеря мощности, обусловленная недостаточным быстродействием.

Наиболее близок к предлагаемому по средствам и достигаемому результату предоконечный каскад блока управления мощным транзистором, содержащий первый И -p- Н-транзистор и второй р-и-р-транзистор, эмиттеры которых подсоединены к клемме для подключения базы мощного транзистора, клемма для подключения коллектора которого подсоединена к катоду первого диода, подсоединенного анодом к базам первого и второго транзисторов, коллекторы которых соответственно через первый и второй резисторы подсоединены к клеммам для подключения источника питания, при этом клемма для подключения источника управляющего напряже ния подсоединена к первому выводу третьего резистора, второй вывод которого подсоединен через последовательно соединенные второй диод и четвертый резистор к эмиттеру третьего

P->-P-транзистора, клемме для подключения положительного вывода первого источника питания и одновременно через последовательно соединенные третий диод и пятыи резистор к базе первого и -р-И-транзистора, которая соединена через шестой резистор с клеммой для подключения отрицательного вывода второго источника питания, причем база и коллектор третьего р-и-р-транзистора подсоединена соответственно .к анодам второго и третьего диодов (2).

Недостатком известного устройства является значительная длительность времени выключения мощного транзистора, что приводит к потере мощности.

Цель изобретения — повышение быст родействия предоконечного каскада.

Поставленная цель достигается тем, что каскад снабжен дополнительным

И-р-п-транзистором, первым и вторым .дополнительными резисторами и конден=атором, один вывод которого соеди30 нен с клеммой для подключения источ970588 ника управляющего напряжения, а второй вывод через первый дополнительный резистор — с базой дополнительного транзистора, коллектор которого соединен с базой первого транзистора, а эмиттер — с клеммой для подключения минусового вывода второго источника питания и одновременно через второй дополнительный резистор с его базой.

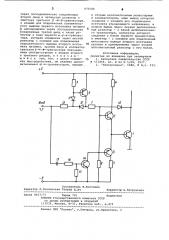

На чертеже приведена принципиальная электрическая схема предоконечно- 10

ro каскада блока управления мощным транзистором.

Предоконечный каскад содержит клеммы для подключения мощного транзистора 1, эмиттерные повторители на транзисторах 2 и 3, ограничивающие резисторы 4 и 5, ключевой транзистор 6, нагруэочные резисторы 7 и 8, резистор 9 утечки, диоды 10-12, входной резистор 13, транзистор 14 ускоренного выключения, дифференцирующий конденсатор 15, ограничивающий резистор 16 и резистор 17 утечки.

База мощного переключательного транзистора 1 соединена с эмиттерами транзисторов 2 и 3. Между коллектором транзистора 2 и первой шиной питания включен резистор 4. Между коллектором транзистора 3 и второй шиной питания включен резистор 5. К базам транзисторов 2 и 3 подсоединен анод диода 10. его катод подключен к коллектору транзистора 1. Эмиттер транзистора б соединен с клеммой для подключения положительного вывода первого источника питания. 35

Между базой и эмиттером транзистора б включен резистор 9 утечки. Между коллектором транзистора 6 и базами транзисторов 2 и 3 подключен резистор 7. Между базами тран- gQ зисторов 2 и 3 и второй шиной питания подсоединен резистор 8. К базе транзистора б подключен анод диода 11, а к коллектору — анод диода 12. Катоды диодов 11 и 12 че- 45 реэ резистор 13 соединены с клеммой для подключения источника управляющего напряжения. Коллектор транзистора 14 соединен с базами транзисторов 2 и 3, а эмиттер — с клеммой для подключения минусового вывода второго источника питания. Между базой транзистора 14 и входом устройства последовательно включены резистор 16 и конденсатор 15. Между базой и эмит ером транзистора 14 подключен резйс- 55 тор 17 утечки. Коллектор транзистора 1 подключен к внешней нагрузке.

На схему предоконечного каскада по отношенио к эмиттеру транзистора

1 подается два низковольтных напряже. 60 ния питания +E и -Е. В режиме ожидания все транзисторы схемы, кроме транзистора 3, закрыты. На базе транзистора 1 поддерживается отрицательное запирающее напряжение вследствие деиствия эмиттерного повторителя, выполненного на транзисторе 3. Ток, потребляемый по цепям питания, в этом режиме равен тепловым токам утечки транзиСторов схемы. При поступлении входного отрицательного импульса открывается транзистор б. Диоды 11 и 12 обеспечивают ненасыщенный режим открытого транзистора б. Ток коллектора транзистора б через резистор 7 и эмиттерныи повторитель 2 попадает в базу транзистора 1, что приводит к его открыванию. Появляется ток в цепи коллектора транзистора 1 и в цепи внешней нагрузки. Диод 10 обеспечивает ненасыщенный режим транзистора 1.

Транзистор 3 во время действия входного импульса оказывается закрытым, так как к его переходу эмиттер-база приложено закрывающее напряжение.

Передний фронт входного импульса, пройдя через дифференцирующий конденсатор 15 и резистор 16, прикладывается в виде кратковременного всплеска отрицательной полярности к базе транзистора 14. При окончании входного импульса выключается сначала транзистор б, а затем транзисторы 2 и 1.

Задний фронт входного импульса, пройдя через дифференцирующий конденсатор

15 и резистор 16, вызывает кратковременное открывание транзистора 14.

Вследствие этого в рассматриваемый момент времени происходит форсированное, ускоренное выключение транзисторов 2, б и мощного транзистора 1.

После закрывания транзистора 14 транзистор 1 удерживается в закрытом состоянии благодаря току транзистора 3.

Далее схема возвращается в исходное состояние.

Использование изобретения обеспечивает существенное уменьшение времени выключения мощного транзистора, что приводит к снижению потерь на коммутацию.

Формула изобретения

Предоконечный каскад блока управления мощным переключательным транзистором, содержащий первый и -ритранзистор и второй р -и-р-транзистор, эмиттеры которых подсоединены к клемме для подключения базы мощного транзистора, клемма для подключения коллектора которого подсоединена к катоду первого диода, подсоединенного к базам первого и второго транзисторов, коллекторы которых соответственно через первый и второй резисторы подсоединены к клеммам для подключения источников питания, при этом клемма для .подключения источника управляющего напряжения подсоединена к первому выводу третьего резистора, второй вывод которого подсоединен

970588

Составитель В.Костюхин

Редактор Л.Пчелинская Техред Д.Ач

Корректор И.Ватрушкина

Заказ 8417/71 Тираж 721

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Филиал ППП "Патент", r.Óæãoðoä, ул.Проектная, 4 через последовательно соединенные второй диод и четвертый резистор к змиттеру третьего P -и- -транзистора, к клемме для подключения положительного вывода первого источника питания и одновременно через последовательно соединенные третий диод и пятый ре зистор к базе первого n -p- -транзистора, которая соединена через шестой резистор с клеммой для подключения отрицательного вывода второго источНика питания, причем база и коллектор третьего p - -p-транзистора подсоединены соответственно к анодам второго и третьего диодов, о т л и ч а ю— шийся тем, что, с целью повышения быстродействия, он снабжен дополнительным И -р -и-транзистором, первым, и вторым дополнительным резисторами и конденсатором, один вывод которого соединен с клеммой для подключения источника управляюшего напряжения, а второй вывод через первый дополнительный резистор †. с базой дополнительного транзистора, коллектор которого соединен с базой Первого транзистора, а эмиттер — с клеммой для подключения минусового вывода второго источника

10 питания и одновременно через второй дополнительный резистор с его базой.

Источники информации,,принятые во внимание при экспертизе

15 1. Авторское свидетельство СССР

:Р 571859, кл . Н 02 M 1/08, 1977.

2. "Электроника", 1980, М 8,с. 111.