Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

Союз Советских

Соцнапнстнческнх

Респубпнк

АНИЕ (III

ABT©PCKOMY CBHQETHlbCTBV (61) Дополнительное к авт. спид-ву (53)М. Кл.

Н 03 D 3/04 (22) Заявлено 07.04.81 (2l ) 3271328/18-09 с присоединением заявки М

3Ъоударствсниый комитет

СССР (23) Приоритет ио делом изаоретеиий и открытий

ОпУбликовано 30,10.82. Бюллетень М 40 (53) УДК 621.376..4(088.8) Дата опУбликования описания 30,10.82

fl т

В. А. Соловьев, М.В. Баркалов и В. B. Бтячков

I"

Московский ордена Трудового Красного Знамени текстильный институт им. A. Н. Косыгина т. (72) Авторы изобретения (7I) Заявитель (54) ФАЗОВЫЙ ДИСКРИМИНАТОР

Изобретение относится к измерительной технике и может быть использовано для измерения разности фаз двух напряжений.

Известен фазовый дискриминатор, содержащий четыре элемента И, инвертор, сумматор и блокирующий 1 Ж -триггер, j-вход которого соединен с выходом первого элемента И, а %,-вход - с выходом второго элемента И,. а его выходы соединены с первыми входами третьего, четвер-т0 того элементов И, соответственно, выходЫ которых подключены к входам сумматора, выход которого является выходом устройства, а первый вход второго элемента И через инвертор подключен к источ15 нику опорного сигнала (1 ) .

Однако известный фазовый дискриминатор обладает невысокой точностью и недостаточно надежен. Это объясняется тем, 20 что длительность импульсов напряжения, поступающих на входы сумматора, в атом фазовом дискриминаторе равна сумме времени, соответствуюшего фазовому сдвигу

2 между опорным и сравниваемым сигналами, и времени задержки распространения сигнала, обусловленного инерционностью инверторов опорного и сравниваемого сигналов элементов И. Особенно большие ошибки измерения фазового сдвига, опорного и сравниваемого сигналов этим фазовым дискриминатором будут при одинаковом порядке времени, соответствующем фазовому сдвигу, и времени задержки распространения сигнала.

Цель изобретения — повышение точности и надежности. Поставленная цель досгигается тем, что в фазовый дискриминатор, содержащий четыре элемента И, инвертор, сумматор и блокирующий 1Ф -триггер, 1 -вход которого соединен с выходом первого элемента

И, à к-вход — с выходом второго элемента И, а выходы соединены с первыми входами третьего и четвертого элементов И, соответственно, выходы которых подключены к входам сумматора, выход которого является выходом устройства, а первый

3 97063 вход второго элемента И через инвертор подключен к источнику опорного сигнала, введен фазовый с -триггер, -вход zoторого соединен с источником входного сигнала, а Ф -вход - с источником опорного сигнала и первым входом первого элемента И, при этом прямой выход фазового jW -триггера соединен с вторыми входами первого и третьего элементов И, а его инверсный выход - с вторыми входами второго и четвертого элементов И.

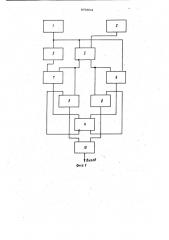

На фиг. 1 изображена структурная электрическая схема фазового дискриминатора; на фиг. 2 - врем4нные диаграммы, поясняющие работу схемы. !5 Фазовый дискриминатор содержит источники 1 и 2 опорного и входного сиг» налов, фазовый и блокирующий jW-триггеры 3 и 4, инвертор 5, четыре элемента 6 — 9 И и сумматор 10. ао

Фазовый дискриминатор работает следующим образом.

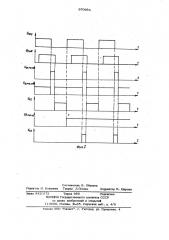

Предположим, что напряжение входного сигнала О вход отстает по фазе от напря- 25 жения опорного сигнала U опор (фиг. 2).

Задними фронтами импульсов опорного сигнала осуществляется перевод фазового триггера 3 в состояние, в котором на его прямом выходе будет напряжение, соот- р ветствуюшее логической "1", а на1инверсном выходе — логическому "0", а задними фронтами импульсов входного сигнала осуществляется перевод его в противоположное состояние. При этом на его прямом выходе возникает последовательность импульсов Оф тр пр длительность которых пропорциональйа фазовому сдвигу напряжений входного и опорного сигналов, а на инверсном выходе - инвертированная 4п последовательность этих же импульсов

О ф тр инр На выходе первого элемента

6 И установится логический "0", а на выходе второго элемента 7 И появится последовательность импульсов Ои g. Зад- 4 ним фронтом первого из этих импульсов осуществится перевод блокирующего триггера 4 в состояние логической 1" на его прямом выходе Us .Р др и логического 0 на инверсном выходе. На выходе четвертого элемента И 9 устанавливается логический "0", а на выходе третьего элемента 8 И появляется последовательность импульсов 0 @ поступающая с прямого выхода фазового -триггера

3. Эта последовательность импульсов по5$ ступает на первый вход сумматора 10, напряжение на выходе которого прямо пропорционально длительности импульсов, 4 поступающих,на его входы, . а полярность зависит от того, на какой из входов подаются эти импульсы, Работа дискриминатора при оперех<ении входным сигналом опорного происходит аналогичным образом.

Время задержки сигналов на элементах дискриминатора не влияет на точность и надежность работы схемы, поскольку опорный и входной сигналы поступают непосредственно на 4 - и j -входы фазового триггера 3, а последовательность импульсов с выхода фазового j% -триггера 3 через третий или четвертый элементы

8 и 9 И, поступают на вход сумматора

lO. Причем время задержки сигнала логическим элементом 8 И или 9 И также не влияет. на длительность этих импульсов, а влияет только на величину задержки поступления импульсов на вход сумматора 10. Поэтому напряжение на выходе сумматора 10 прямо пропорционально фазовому сдвигу между опорным и входным сигналами, а его полярность зависит от знака разности этих сигналов.

Таким образом, предлагаемый фазовыйдискриминатор имеет более высокую точность и надежность. формула изобретения фазовый дискриминатор, содержащий четыре элемента И, инвертор, сумматор и блокирующий % -триггер, -вход которого соединен с выходом первого элемента И, а -вход - с выходом второго элемента И, а выходы соединены с первыми входами третьего и четвертого элементов И соответственно, выходы которых подключены к входам сумматора, выход которого является выходом устройства, а первый вход второго элемента И через инвертор подключен к источнику опорного сигнала, отличающийся тем, что, с целью повышения точности и надежности, в него введен фазовый триггер, -вход которого соединен с источником входного сигнала, à k --вход — с источником опорного сигнала и первым входом первого элемента И, при этом прямой выход фазового j9 -триггера соединен с вторыми входами первого и третьего элементов И, а его инверсный выход - с вторыми входами второго и че вертого элементов И, Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 720680, кл. Н 033 3/04, 1980 (прототип) .

970634, Составитель B. Обровец

Редактор H. Ковалева Техред Л.Пекарь Корректор М. Шароши

Заказ 8420/73 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/S

Филиал ПГ1П "Патент", r. Ужгород, ул. Проектная, 4