Операционный усилитель

Иллюстрации

Показать всеРеферат

<п>970638

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. саид-ву (22) Заявлено 29.12.80 (21) 3227497/18-09 с присоединением заявки М (53)M. Кл.

Н 03 F 3/45

9кудврстеевим6 квинтет

СССР во лелем изобретении и открытий (23) Приоритет

Опубликовано 30.10 82. Бюллетень JA 40

Дата опубликования описания 30.10.82 (53) УДК 621.375.

° 024 (088.8) (72) Авторы изобретения

В. С. Рысин и В. А. Ткаченко (7! ) Заявитель (54) ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ

Изобретение относится к электронной технике и может быть использовано в операционных усилителях, компараторах и других устройствах аналоговой техники.

Известен операционный усилитель, содержащий первый и второй дифференпиаль ные каскады и эмиттерный повторитель, нагрузка которого выполнена в виде по следовательно соединенных диода и гене ратора тока, причем первый дифференциаль.то иый каскад выполнен по каскадной схеме с реэистивными нагрузками, между базами его входных транзисторов встречно включены эмиттерные переходы защитных транзисторов, коллекторы которых объединены и подсоединены к одному выводу первого резистора, базы выходных транзисторов первого дифференциального каскада подключены к точке соединения

Генератора тока и диода нагрузки эмиъ- . терного повторителя, вход которого подключен к эмиттерам входных транзисторов первого дифференциального каскада, при этом второй дифференциальный каскад выполнен с цепью коррекции и подключен к выходу первого дифференциального каскада )l) .

Однако известный операционный усилитель имеет низкое быстродействие.

Бель изобретения - повышение быстро действия.

Поставленная цель достигается тем, что в операционный усилитель введен дополнительный транзистор, база которого подключена к базам выходных транзисторовв первого дифференцильного каскада, эмиттер- к другому выводу первого резистора и через второй резистор к выходу эмитУерного повторителя, коллектор. - к общей точке .реэистивных нагрузок . первого дифференциального каскада, которая псдключена к шине питания черж цепь смещении, состоящую иэ последовательно соединенных дополнительных диода и резистора.

3 97063

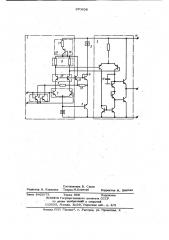

На чертеже представлена принципиаль иая электрическая схема предлагаемого операционного усилителя, Операционный усилитель содержит первый 1 и второй 2 дифференциалъные каскады и эмиттерный повторитель 3, нагруз- ка которого выполнена в виде последовательно соединенных диода 4 и генерато,ра 5 тока, причем первый дифференциаль:ный каскад 1 выполнен по каскадной схе- 10 ме с резистивными нагрузками 6, между базами ei o входных транзйсФоров 7 встреч,но включены эмиттерные переходы защитных транзисторов 8, коллекторы кото- рых объединены и подсоединены к одному 1$ вь воду первого резистора 9, базы выходных транзисторов 10 первого дифференциального каскада 1 подключены к точке соединения генератора тока 5 и диода 4 нагрузки эмиттерного повторителя 3, вход 26

Которого подключен к эмиттерам входных транзисторов 7 первого дифференциального каскада 1, при этом второй дифференциальный каскад 2 выполнен с цепью коррекции 11 и подключен к выходу первого 2$ дифференциального каскада 1. База дополнительного транзистора 12 подключена к базам выходных транзисторов 10 первого дифференциального каскада 1, эмиттер — к другому выводу первого ре- $р зистора 9 и через второй резистор 13 к выходу эмиттерного повторителя 3, коллектор - к обшей точке резистивных нагрузок 6 первого дифференциального каскада 1, которая подключена к шине питания 14 через цепь смещения 15, состоя шую из последовательно соединенных дополнительных диода 16 и резистора 17.

Операционный усилитель работает следующим образом.

46

В режиме малого сигнала коллекторные токи защитных транзисторов 8 отсутствуют. Поэтому выбором номинала второго резистора 13 и тока генератора

5, создацшего падение напряжения на диоде 4, коллекторный ток дополнительно го транзистора 12, а следовательно, и ток покоя второго дифференциально о каскада 2 можно сделать достаточно низким.

В режиме большого сигнала защитные транзисторы 8 открываются, их коллекторные токи создают падение напряжения ,на втором резисторе 13 другой полярности. Это приводит к резкому увеличению коллекторного тока дополнительного тран-.

$$ зистора 12, и следовательно, к увеличению тока второго дифференциального кас8 ф када 2. Конденсатор цепи коррекции 11 быстро заряжается большим током второ» го дифференциального каскада 2. В результате быстродействие всего операционного усилителя возрастает.

Таким образом, поскольку дополнительный транзистор в режиме большого сигнала обеспечивает увеличение тока второго дифференциального каскада, то конденсатор цепи коррекции заряжается быстрее, что обеспечивает увеличение быстродействия всего операционного усилителя. формула изобретения ю

Операционный усилитель, содержащий первый и второй дифференциальные каскады и эмиттерный повторитель, нагрузка . которого выполнена в виде последовательно соединенных диода и генератора тока, причем первый дифференциальный каскад выполнен по каскадной схеме с резистивными нагрузками, между базами его входных транзисторов встречно включены эмиттерные переходы защитных транзисторов, коллекторы которых объединены и подсоединены к одному выводу первого реэис тора, базы выходных транзис торов первого дифференциального каскада подключены к точке соединения генератора тока и диода нагрузки эмиттерного повторителя, вход которого подключен к эмиттерам входных транзисторов первого дифференциального каскада, при этом второй дифференциальный каскад выполнен с цепью коррекции и подключен к выходу первого дифференциального каскада, о тл и ч а ю ш и и с я тем, что, с целью повышения быстродействия, введен дополнительный транзистор, база которого подключена к базам выходных транзисторов первого дифференциального каскада, эмиттер - к другому выводу первого резистора и через второй резистор к выходу эмиттерного повторителя, коллектор - к обшей точке резистивных нагрузок первого дифференциального каскада, которая -подключена к шине питания через цепь смещения, состояшую из последовательно соединенных дополнительных диода и резистора, Источники информации, принятые во внимание при экспертизе

1. Аналоговые и цифровые интегральные схемы . Под ред. С. В. Якубовского, М., Советское радио", 1979, с. 217219 (прототип).

970638

Составитель В. Серов

Редактор H. Ковалева Техред М.Койтура Корректор Я. Шароши

Заказ 8420/73 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам:изобретений и открытий

113035, Москва, Ж-З8, Раушская наб., д. 4/5

Филиал ППЛ "Патент, r. Ужгород, ул. Проектная, 4