Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик (»)970677 (61) Дополнительное к авт. сеид-ву (22) Звявлеио 03. 04. 81 (21) 3270262/18-21 с присоединением заявки Но (23) Приоритет

Опубликовано ЗОШ82. Бюллетень Мо 40

Р )М К з

Н 03 К 13j17

Государственный комитет

СССР по делам изобретений и открытий (3 3) УДК 6 81. 325 (088. 8) Дата опубликования описания,30.10. 82 (71) Заявитель (54) АНАЛОГО-ЦИФРОВОИ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к устройствам преобразования амплитуд аналоговых сигналов в цифровой код и применяется в составе устройств измерения амплитудных значений сигналов произвольной формы.

Известен аналого-цифровой преобразователь, содержащий источник опорного напряжения, цифро-аналоговый преобразователь, регистр последовательного приближения и компаратор, первый вход которого связан с выходом цифро-аналогового преобразователя, а со вторым соединен зажим, на который поступает измеряемый сигнал 1 1)..

Известен аналого-цифровой преобразователь, содержащий цифро-аналоговый преобразователь, регистр последовательного приближения, компаратор, первый вход которого связан с выходом цифро-аналогового преобразо вателя, а со вторым соединен зажим на который поступает измеряемый сигнал, источник опорного напряжения и элемент подстройки, соединенный с, третьим входом компаратора 1.2 .

Недостатком известных устройств является низкая точность преобразования и быстродействия.

Цель изобретения - расширение динамического диапазона измеряемых сигналов и повышение точности и быстродействия преобразования.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий регистр последовательного приближения,цифро-аналоговый преобразователь, выход которого соединен с первым входом компаратора, второй вход которого соединен с выходом элемента подстройки, первый вход которого соединен с выходом источника опорного напряжения, второй выход которого соединен с первым входом цифро-аналогового преобразователя, введены и-разрядный сдвиговый регистр, и элементов ИЛИ,реверсивный и разрядный счетчик, элемент ввода кода, элемент сдвига кода, элемент И, триггер управления, коммутатор, генератор калибровочных импульсов и генератор команд, первый вход которого соединен с входом и-разрядного сдвигового регистра, и-выходов которого через элементы ИЛИ соединены с входами элемента подстройки и с первыми входами п-разрядного реверсивного счетчика, а (n +1)-й выход через триггер управления - с первым входом

970677 элемента сдвига кода и первым входом генера-.ора команд, второй выход котороги соединев с вторым входом элемента сдвига кода„ третий вход которого соединен с выхоцом компаратора и с первым входом элемента И„ первый выход — с вторым входом реверсивного счетчика, а второй выход - c вторым входом генератора команд, третий выход которого соединен с вторым входом элемента И, четвертый выход - с пер- 10 вым входом элемента ввода кода, пя ,тый вход — с первым входом коммутатора, второй вход которого соединен с выходом генератора калибровочных импульсов, третий вход - с входной шиной, а выход — с третьим входом компаратора, при этом выходы реверсивного счетчика соединены с вторыми входами элементов ИЛИ, причем выход элемента И соединен с входом регистра последовательного приближения, выход которого соединен с вторым входом элемента ввода кода, выход которого соединен с вторым входом цифроаналогового преобразователя. 25

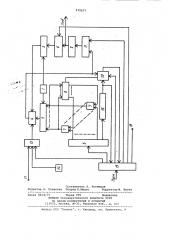

На чертеже представлена блок-схема предлагаемого прео бразов ателя .

Преобразователь состоит из источника 1 опорного напряжения, регистра

2 последовательного приближения, цифро-аналогового преобразователя 3, компаратора 4, элемента подстройки 5, п»разрядного сдвигового регистра б, и элементов ИЛИ 7, и-разрядного реверсивного счетчика 8, элемент 9 ввода, З5 элемент 10 сдвига кода, элемент И 11 триггера 12 управления, коммутатора

13 генератора 14 калибровочных импульсов, генератора 15 команд, шину

16 синхронизации, входную шину 17. 40

Первый выход генератора 15 команд соединен с входом сдвигового регистра б, п выходов последнего через элементы ИЛИ 7 подключены к входам элемента подстройки и входам реверсивного счет45 чика 8, и выходов которого соединены с вторыми входами соответствующих элементов ИЛИ 7, а (n+1)-й выход сдви гового регистра б через триггер 12 управления соединен с входом элемента

10 сдвига кода, первый выход послед. него соединен с (п+1)-м входом реверсивного счетчика 8, второй выход — с входом генератора 15 команд, а второй вход - c вторым выходом генератора 15 команд. Выход триггера 12 управления соединен с вторым входом генератора

15 команд.

Третий выход генератора 15 команд соединен с входом элемента И 11, выход которого через регистр 2 после- ОО довательного приближения и элемент 9 ввода соединен с входом цифро-аналогового преобразователя 3, а четвертый выход - соединен с вторым входом элемента 9 ввода. Выходы источника 1 65 опорного напряжения соединены соответственно к входам элемента подстрой ки 5 и цифро-аналогового преобразователя 3, выход которого соединен с вторым входом компаратора 4, первый и третий входы последнего соединены с выходами соответственно коммутатора

13 и элемента 5 подстройки, а выходс третьим входом элемента 10 сдвига кода и первым входом элемента И 11.

Пятый выход генератора 15 команд соединен с третьим входом коммутатора

13, второй вход которого соединен с выходом генератора 14 калибровочных импульсов, а первый соединен с шиной

17, на которую поступает измеряемый сигнал. Шестой выход генератора 15 команд соединен с шиной 16.

Преобразователь работает следующим образом.

Первоначально генератор 15 команд устанавливает в исходное состояние сдвиговый регистр 6, регистр 2 последовательного приближения, реверсивный счетчик 8 и триггер 12 управления, и производится подстройка аналого-цифрового преобразователя.

Генератор 15 команд записывает единицу в старший разряд сдвигового регистра б, которая через элемент

ИЛИ 7 поступает на вход старшего и-го разряда элемента 5 подстройки, выполненного в виде цифро-аналогового преобразователя. Сигнал с выхода последнего поступает на вход компаратора 4. Генератор 15 команд опрашивает состояние компаратора 4 и, если величина корректирующего сигнала на выходе элемента подстройки 5 велика, элемент 10 сдвига кода генерирует сигнал, .по которому генератор 15 команд выполняет сдвиг кода в регистре б, подключая к входу компаратора 4 корректирующий сигнал, соответствующий включенному (п- 1) -ому разряду элементу 5 подстройки .

Если первоначально подключенный к входу компаратора 4 корректирующий сигнал окажется недостаточным, то элемент 10 сдвига кода формирует команду записи единицы в соответствующий разряд реверсивного счетчика 8, а затем, сдвинув код в регистре б, подключает к входу компаратора 4 корректирующий сигнал, соответствующий включенному следующему (n-I) "ому разряду, на входе элемента 5 подстройки.

Процесс повторяется, реализуя последовательное приближение кода в реверсивном счетчике 8 и соответствующего ему корректирующего сигнала на выходе цифро-аналогового преобразователя 5 к необходимым для приведения компаратора 4 в нулевое состояние °

После этого сигналом с (n+1)-го выхода сдвигового регистра б триггер 12 управления устанавливается в еди нич970677 ное состояние, а элемент 10 сдвига кода блокирует сдвиговый регистр 6 и переводит реверсинный счетчик 8 в режим отслеживания записанного н него двоичного кода, В дальнейшем в моменты коррекции нулевой точки компаратора 4 код в реверсивном счетчике 8 претерпевает изменения, равные 1 единице его младшего разряда ° Соответственно и корректирующий сигнал на выходе цифро-аналогового преобра- 10 зователя 5 изменяется на величину, 20

В дальнейшем генератор 15 команд разрешает элементу 9 ввода подключить

50 равную +1 единице его младшего разряда. Одновременно единичный сигнал с триггера 12 поступает на генератор

15 команд, а последний через элемент

И 11 записывает единицу в старший разряд регистра 2 последовательного приближения и разрешает прохождение измеряемого сигнала через коммутатор

13 на вход компаратора 4, если измеряемый сигнал не импульсный или подает на шину 16 синхронизации команду, синхронизирующую появление импульсного измеряемого сигнала. к цифро-аналоговому преобразователю

3 старший разряд регйстра 2 последовательного приближения, а по состоянию компаратора 4 после его подключения выполняет необходимое изменение кода в регистре 2 последовательного приближения, реализуя последовательное приближение кода к искомой величи не .

Если при реверсивном отслеживании нулевой точки компаратора 4 элемент

10 сдвига кода зафиксирует несколько последовательных команд изменения кода в одном направлении, например три, что может иметь место при сбое, генератор 15 команд переводит в исходное состояние триггер 12 управления, часть разрядов сдвигового регистра 6 и реверсивного счетчика 8, а затем выполняет алгоритм последовательного приближения кода цифроаналогового преобразователя 5 к эначению, соответствующему нулевой точке компаратора, после чего найденный код корректируется с дискретно-!

;стью +1 младшего разряда аналогично описанному выше.

Предлагаемый преобразователь повышает точность преобразования аналоговых сигналов н цифровой код, быстродействие преобразования за счет ускорения процесса отслежинания нулевого состояния компаратора, расширяет динамический диапазон измеряемых сигналов.

Формула изобретения

Аналого-цифровой преобразователь, содержащий регистр последовательного приближения, цифро-аналоговый преобразователь, выход которого соединен с первым входом компаратора, второй вход которого соединен с выходом элемента подстройки, первый вход которого соединен с первым выходом источника опорного напряжения, второй выход которого соединен с первым входом цифро-аналогового преобразователя, отличающий с я тем, что, с целью расширения динамического диапазона измеряемых сигналов, а также повышения точности и быстродействия преобразования, в него введены и-разрядный сдвнговый регистр, п элементов ИЛИ, ренерсивный и-разрядный счетчик, элемент ввода кода,элемент сдвига кода, элемент И, триггер управления, коммутатор, генератор калибровочных импульсов и генератор команд, первый выход которого соединен с входом и-разрядного сднигового регистра, п выходов которого через элементы ИЛИ соединены с входами элемента подстройки и первыми входами п-разрядного реверсивного счетчика, а (и+1)-й выход через триггер управления — c первым входом элемента сдни га кода и первым входом генератора команд, второй выход которого соединен с вторым входом элемента, сдвига кода, третий вход которого соединен с выходом компаратора и с первым входом элемента И, первый выход - с вторым входом реверсивного счетчика, а второй выход — с вторым входом генератора команд, третий выход которого соединен с вторым входом элемента И, четвертый выход — с первым входом элемента ввода кода, пятый вход — c первым входом коммутатора, второй вход которого соединен с выходом генератора калибровочных импульсов, третий вход — с входной шиной, а выход - с третьим входом компаратора„ при этом выходы реверсивного счетчика соединены с вторыми входами элементов ИЛИ, причем выход элемента И "îåäèíåí с входом регистра последовательного приближения, выход которого соединен с вторым входом элемента ввода кода, выход которого соединен с вторым входом цифро-аначогоного преобразователя.

Источники информации, принятые во внимание при экспертизе

1, Контрольно-измерительная техника. 1979, Р 28,,с. 11-14.

2. Вопросы радиоэлектроники. Серия ЗВТ, 1976, Р 10, с. 26-32 (прототип) .

970677

Составитель A. Кузнецов

Редактор Н. Ковалева Техред К.Мыцьо Корректор М. Коста

Заказ 8424/75 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал IIIIII "Патент", r. Ужгород, ул. Проектная, 4