Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву (22) 3aseneHo 13 ° 04. 81 (21) 3271760/18-21 с присоединением заявки ¹(23) Приоритет

Н 03 К 13/17

Государственный комитет

СССР но делам изобретений н открытий

Опубликовано 301082 Бюллетень Мо 40

РЗ) УДК 681. 325 (088. 8) Дата опубликования описания30.10.82 (72} Автор изобретения

Е.Г.Шевченко (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к автоматике и вычислительной технике, и может быть использовано для преобразования напряжения в цифровой код.

Известен аналого-цифровой преобразователь, содержащий делитель напряжения, аналоговые ключи, усилители, генераторы тока, устройство управления, .устройство сравнения, триггеры и элемент ИЛИ (1).

Недостатками указанного аналогоцифрового преобразователя являются сложность настройки и низкая надежность

Известен аналого-цифровой преобразователь, содержащий входной ключ,. подключенный к входу усилителя, устройство сравнения, первый вход которого соединен с выходом усилителя, второй вход - с выходом источника опорного напряжения, первый и второй ключи, первые входы которых соединены с входом усилителя, вторые входы - с выходом усилителя, а выходы — с первыми обкладками первого и второго запоминающих конденсаторов, третий и четвертый ключи, первые входы которых соединены с выходоМ усилителя, а выходы — с первыми обкладками третьего и четвертого запоминающих конденсаторов, пятый и шестой ключи, первые входы которых соединены со вторыми входами третьего и четвертого ключей соответственно, а выходы — с вторыми обкладками первого и второго запоминающих конденсаторов, седьмой и восьмой ключи, первые входы которых соединены с шиной нулевого потенциала, а выходы— с вторыми обкладками третьего и четвертого запоминающих конденсаторов (2 1.

В этом преобразователе реализован алгоритм поразрядного уравновешивания, причем разряду кода присваивается нулевое значение при сравнении удвоенного напряжения, полученного в предыдущем цикле преобразования на выходе усилителя, с первым опорным напряжением U а единичное значение при сравнении разности удвоенного напряжения, полученного в предыдущем цикле преобразования и второго опорного напряжения U< = 2U4 с первым опорным напряжением.

Выходная информация представляется в виде последовательного кода.

Недостатками известного аналогоцифрового преобразователя являются

970679 невысокая точность иэ-эа повышенных рабочих напряжений на зарядных конденсаторах и требование для работы двух источников опорных напряжений.

Пель изобретения — повышение точности работы устройства. 5

Укаэанная цель достигается тем что в аналого-цифровой преобразователь, содержащий входной ключ, подключенный к входу усилителя, устройство сравнения, первый вход кото- JQ рого соединен с выходом усилителя, второй вход — с выходом источника опорного напряжения, первый и второй ключи, первые входы которых соединены с входом усилителя, вторые входы — с выходом, усилителя, а выходыс первыми обкладками первого и второго запоминающих конденсаторов, третий и четвертый ключи, первые входы которых соединены с выходом усилителя, а выходы — с первыми об-" кладками третьего и четвертого запоминающих конденсаторов, пятый и шестой ключи, первые входы которых соединены с вторыми входами третьего и четвертого ключей соответственно, а выходы — c вторыми обкладками первого и второго запоминающих коиденсаторов, седьмой и восьмой ключи, первые входи которых соединены с шиной нулевого потенциала, а выходыс вторыми обкладками третьего и .четвертого запоминающих конденсаторов, введены два дополнительных ключа, входы которых соответственно подключены к выходу источника опорного напряжения и к шине нулевого потенциала, а выходы — к вторым входам пятого, шестого, седьмого и восьмого ключей.

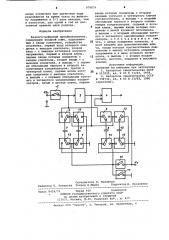

На чертеже представлена электричес 40 кая схема предлагаемого устройства.

Устройство содержит ключ 1, входной ключ 2,усилитель З,устройство 4 сравнения, ключи 5 и б, запоминающие кон; денсаторы 7-10 и ключи 11-17. 45

Устройство работает следующим образом.

Для реализации алгоритма последовательного поразрядного кодирования входное напряжение П сравнивается 1О с опорным напряжением Бо. Если входное напряжение меньше опорного, то старшему разряду кода присваивается нулевое значение, а напряжение U> удваивается и снова сравнивается с опорным напряжением.

Если входное напряжение больше опорного, то старшему разряду кода присваивается единичное значение, а разность входного и опорного напряже- 60 ния U -П удваивается и снова сравнивается с опорным напряжением.

Таким образом, в каждбм такте напряжение, поданное на вход преобразователя, сравнивается с опорным напряжением и удваивается, если определенный код в данном такте равен нулю, или удваивается разность напряжений на входе преобразователя и опорного напряжения, если код равен единице, Удвоенное напряжение снова подается на вход преобразователя для определения кода следующего разряда.

В первом такте происходят следующие коммутации.

Входной ключ 2 замыкается и соединяет внешний Источник входного сигнала с входом усилителя 3, имеющего единичный коэффициент усиЛения и большое входное сопротивление. Напряжение

И с выхода усилителя поступает на один из входов устройства 4 сравнения. Устройство сравнения определяет старший разряд кода. Если U .. < U старший разряд кода равен нулю, если

U 3 Uö - то единиц@. Этот процесс занимает незначительную по времени часть такта, так как запоминающие конденсаторы на выходе усилителя отключены. При получении на выходе устройства.сравнения единичного кода срабатывает ключ 16 и включает запоминающие конденсаторы 7 и 9 между выходом усилителя и источником опорного напряжения, а при получении нулевого кода ключ 17 включает запоминающие конденсаторы 7 и 9 между выходом усилителя и шиной нулевого потенциала.

Эапоминающие конденсаторы 7 и 9 заряжаются в первом случае до напряжения U>> - Бо, а во втором случае до напряжения, равного U> .

Во втором такте размыкаются входной ключ 2 и ключ 16 при единичном коде или ключ 17 при нулевом коде, а запоминающие конденсаторы 7 и 9 включаются последовательно ключами 5, 13 и 11, 1 между входом усилителя 3 и шиной нулевого потенциала. При этом на вход усилителя подается напряжение 2П -М„или 20@ в зависимоcTH от полученного кода разряда. Одновременно срабатывают ключи б, 10, 12, 14, включая запоминающие конденсаторы 8 и 10 параллельно.

При получении кода разряда на выходе устройства сравнения срабатывает один из ключей 16 или 17 в зависимости от полученного кода и подключает запоминающие конденсаторы 8 и 10 между выходом усилителя и источником опорного напряжения или шиной нулевого потенциала в зависимости от полученного кода.

В последующих тактах процесс повторяется до получения кода младшего разряда. При получении кода младшего разряда включается входной ключ 2 и процесс преобразователя начинается сначала.

В предлагаемом аналого-цифровом преобразователе, последовательно включенные запоминающие конденсаторы на

970679

Формула изобретения

Составитель В. Махнанов

Редактор Н. Ковалева Техред К.Мыцьо Корректор В. Прохненко

Заказ 8424/75 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 входе усилителя при единичном коде разряжаются эа время такта на величину напряжения в 2-3 раза меньшую, чем в известном, при одной и той же постоянной времени цепи разряда.

Аналого-циФровой преобразователь, содержащий входной ключ, подключенный к входу усилителя, устройство 10 сравнения, первый вход которого сое динен с выходом усилителя, второй вход - с выходом источника опорного напряжения, первый и второй ключи, первые входы которых соединены с 15 входом усилителя, вторые входы - с выходом усилителя, а выходы — с первыми обкладками первого и второго запоминающих конденсаторов, третий и четвертый ключи, первые входы которых соединены с выходом усилителя, а выходы - с первыми обкладками третьего и четвертого запоминающих конденсаторов, пятый и шестой ключи, первые

+Я входы которых соединены с вторыми входами третьего и четвертого ключей соответственно, а выходы - с вторыми обкладками первого и второго запоминающих конденсаторов, седьмой и восьмой ключи, первые входы которых соединены с шиной нулевого потенциала, а выходы - с вторыми обкладками третьего и четвертого запоминающих конденсаторов, отличающийся тем, что, с целью повышения точности, в него введены два дополнительных ключа, входы которых соответственно подключены к выходу источника опорного напряжения и к шине нулевого потенциала, а выходы — к вторым входам пятого, шестого, седьмого и восьмого ключей.

Источники инФормацин, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 617832, кл. Н 03 К 13/02, 1978 °

2. Авторское свидетельство СССР

9 739732, кл. Н 03 К 13/02, 1980 (прототип).