Стартстопный электронный приемник

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИЯЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублии (ti>970720 (61) Дополнительное к авт. свид-ву (51)M. Кл.

Н 04 1. 17716 (22) Заявлено 09.04.81 (21) 327 1462/18-09 с присоединением заявки М (23) Приоритет

Ркударствеиный комитет

СССР ао делам изобретений и открытий (53) УДК621.394..62 (088.8) Опубликовано 30.10.82, Бюллетень № 40

Дата опубликования описания 30.10.82

Ьт,д, Научно-исспедоватепьский и опытно-конструкторский,инс1итут автоматизации черной метаппургии (71) Заявитель (54) СТАРТСТОПНЫЙ ЭЛЕКТРОННЫЙ ПРИЕМНИК

Изобретение относится к эпектросвязи.

Известен стартстопный эпектронный приемник, содержащий входной согласуюший бпок, задающий генератор и поспедоватепьно соединенные депитепь частоты

5 и распредепитепь, выходы которого подкпючены к первым входам бнока эпементов И, выходы которого соединены со входами накопитепя, а также триггер1 1).

Однако в известном приемнике недостаточная помехоустойчивость.

Ilem изобретения - повышение помехоустойчивости.

Указанная цепь достигается тем, что в стартстопный эпектронный приемник, содержащий выходной согпасуюший бпок, задающий генератор и поспедоватепьно соединенные депитепь частоты и распре,депитепь, выходы которого подкпючены к первым входам бпока эпементов И, выхо- 20 ды которого соединены со .входами нако» питепя, а также триггер,,введены два эпемента ИЛИ и интегратор, первый вход которого соединен с выходом задающего генератора и с первым входом депитепя часToTbI, второй вход которого соединен со вторым входом распредепитепя и с выходом первого эпемента ИЛИ, первый вход которого соединен с выходом входного согпасуюшего бпока и со вторым входом интегратора, выход которого подкпючен ко вторым входам бпока эпементов И, при этом допопнитепьные выходы распредепитепя подкпючены ко входам второго эпемента ИЛИ, выход которого соединен со входом триггера, выход которого подкпючен ко второму входу первого эпемента

ИЛИ, а второй выход депитепя частоты соединен с третьим входом интегратора.

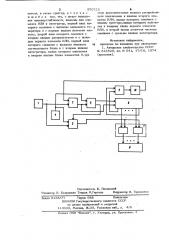

На чертеже изображена структурная эпектрическая схема предпагаемого устройства.

Устройство содержит входной согпасующий бпок 1, эпемент ИЛИ 2, интегратор 3, задающий генератор 4, депитепь

5 частоты, распредепитепь 6, бпок 7

97072

8, эпемент

3 эпементов И, накопитель

ИЛИ 9; триггер 10, Устройство работает спедуюшим образом.

При приеме стартового симвопа сигнап с выхода входного согпасуюшего бпока 1 поступает через эпемент ИЛИ 2 на установочный вход депитепя 5 частоты, на счетный вход которого поступают импупьсы опорной частоты с выходе задающего генератора 4. Стартовый симвоп устанавпивает депитепь 5 частоты в режим счета, и он начинает считать входные импупьсы. Еспи дпитепьность стартового сигнапа будет соответствовать критерию обнаружения сигнапа, то на первом выходе депитепя частоты 5 появится импупьс, который поступит на первый sxoa распредепитепя 6. Сигнап с выхода эпемента

ИЛИ 2 также опредепяет режим работы

20 распредепитепя 6, как и депитепя 5 частоты. Еспи сигнеп, соответствующий стартовому симвопу, будет иметь дпитепьность меньшую, чем T/2, где Х вЂ” дпитепьность эпементарного симвопа, то на пер25 вом выходе депитепя 5 частоты импупьс не появится, а снятие этого сигнапа с установочного входа депитепя 5 частоты устанавпивает его и распредепитепь 6 в

0". Устройство готово к,приему спедуюшего стар го симво . Таврим Обра- 30 зом устройство осуществпяет защиту от пожного старта (защиту от действия помехи, имеющей дпитепьность, меньшую чем С/2).

Еспи стартОвый сигнап имеет дпитепь- 35 ность бопьшую,чем Г/2, то первый импупьс, поступивший с выхода депитепя 5 частоты на вход распредепитепя 6, появится на первом выходе распредепитепя

6 и через эпемент ИЛИ 9 он поступит на вход триггера 10. Триггер 10 срабатывает, сигнап с его выхода поступает на первый вход эпемента ИЛИ 2 и дапьше на установочный вход депнтепя 5 частоты. Этот сигнап удерживает депитепь 45

5 частоты в режиме счета, который переходит в цикпический режим работы. Период спедования импупьсов с первого выхода депитепя 5 частоты равен дпитепьности Г. Эти импупьсы сдвинуты относи- 50 тепьно границ эпементарных посыпок на вепичину, которая равна дпитепьности дискретного интегрирования стартового симвопа. Это время ф,> /2 (0,5-0,7 )Х

Импу пьс, соответствующий концу прННВМВ- 55 емого знака (соответствующий стоповой посыпке принимаемой стартстопной комбинации), поступает с выхода распредепите0 4 пя 6 на второй вход эпемента ИЛИ 9 и дапее на вход триггера 10, который этим импупьсом возвращается в исходное состояние. 3епитепь 5 частоты и распредепитепь 6 устаневпиваются в нупевое состояние, и устройство готово к приему спедуюшей кодовой комбинации.

Во время приема кодовой комбинации на втором выходе депитепя 5 частоты появпяются импупьсы, сдвинутые относитепьно передней границЬ эпементарного симвопа на время г= 0,9 Х... Этн импупьсы поступают на третий вход интегратора 3, на первый вход которого поступает опорная частота с выхода задающего ге- нератора 4, а на второй вход поступает принимаемая информация с входного согпасуюшего бпока 1. Интегратор 3 осушествпяет дискретное интегрирование принимаемой информации, подсчитывая копичество импупьсов с задающего генератора 4 во время приема посыпок единичного уровня. Еспи подсчитанное количество импульсов соответствует дпитепьности действия единичной эпементарной посыпки Ф. Оба, то на выходе интегратора 3 появпяется единичный уровень сигнапа. Поступающие на третий вход интегратора 3 импупьсы со второго выхода распредепитепя 6 спу" жат дпя обнупения счетчика интегратора

3 а конце приема эпементарной посыпки.

С выхода интегратора 3 сигнапы поступают на вторые входы бпока 7 эпементов И, на первые входыкоторых поступают стробируюшие импупьсы с выходов распредепитепя 6. Интегрированные значения симвопов принимаемой стартстопной комбинации записываются через бпок

7 эпементов И в накопитепь 8.

Таким образом, в предпагаемом устройстве осушествпяется зашита от пожного старта, т.е. защита от воздействия импупьсной помехи ипи прерывания канапа связи, время действия которых k 0 > а также дискретное интегрирование эпементарных симвопов принимаемой комбинации. Все это позвопяет повысить помехоустойчивость приема.

Форму па изобретения

Стартстопный эпектронный приемник, содержащий входной согпасуюший бпок, задающий генератор и поспедоватепьно соединенные депитепь частоты и распредепитепь, выходы которого подкпючены к первым входам бпока эпементов И, выходы которого соединены с входами нако5 9707 питепя, а также триггер, о т п и ч аю m и и с я тем, что, с цепью повышения помехоустойчивости, введены два эпемента ИЛИ и интегратор, первый вход которого соединен с выходом задаюшего ге- нератора и с первым входом депитепя частоты, второй вход которого соединен с вторым входом распредепитепя и с выходом первого элемента ИЛИ, первый вход которого соединен с выходом входного 1о согпасуюшего бпока и с вторым входом интегратора, выход которого подкпючен к вторым входам бпока эпементов И, при

20 6 этом допопнитепьные выходы распредепитепя подкпючены к входам второго эпемента ИЛИ,. выход которого соединен с входом триггера, выход которого подкпючен к второму входу первого эпемента

ИЛИ, а второй выход депитепя частоты соединен с третьим входом интегратора.

Источники информации, принятые во внимание прн экспертизе

1. Авторское свидетепьство СССР

¹ 513520, кп. Н 04 l 17/16, 1974 (прототип ).

Составитепь Б. Попянский

Редактор Н. Безродная Техред.М.Гергель Корректор В. Прохиенко

Заказ 8428/77 Тираж 688 Подписное

ВНИИПИ Государственного комитета СССР по депам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Фипиан ППП Патент", г. Ужгород, уп, Проектная, 4