Устройство для контроля схем управления тиристорными преобразователями частоты

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пи972415 (61) Дополнительное к авт. спид-ву (22) Заявлено 03.10.80 (23) 2988147/18-21 с присоединением заявки ЭЙ (23) Приоритет

Опубликовано 07.11.82. Бюллетень РЙ41

Дата опубликования описания 07.11.82 (5l)M. Кд.

G 01 R 23/00

Гооударетвсниый коиитет по делам иаабретеиий и открытий (53) ЩК 621.301..93 (088.8) (72) Авторы изобретения

В. Л. Грузов и А. С. Завьялов (71) Заявитель

Вопогойский политехнический институт (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СХЕМ УПРАВЛЕНИЯ

ТИРИСТОРНЫМИ ПРЕОБРАЗОВАТЕЛЯМИ

ЧАСТОТЫ

Недостаток известного устройства закпючается в том, что оно обнаруживает топько одиночные ошибки в контропиру емой поспедоватепьности импупьсов, появ о пение кратных ошибок им не обнаруживается.

Бель изобретения - повышение достоверности контропя.

Поставленная цепь достигается тем, 15 что в устройстве, содержащем триггеры, соейиненные между собой через входные погические элементы И в бпок регистров сдвига, и выходной эпемент И, чиспо триггеров бпока регистров сдвига увепичено до чиспа контропируемых канапов и в устройство введены триггер перекпючения, допопнитепьный погический эпемент И и йопопни те пьный триггер, при1

Изобретение относится к эпектроизмеритепьной технике и может быть испопьзовано при диагностике тиристорных преобразоватепей частоты.

Известно устройство дпя контроля поспедоватепьности импупьсов, которое содержит триггеры контропя и памяти и три схемы совпадения, соединенные таким образом, что позвопяет в серии поспейоватепьных импульсов, идуших непрерывно„ контропировать появпение в опредепенный момент времени каждого импупьса и, при отсутствии хотя бы одного из них, выдавать сигнапы неисправности (11.

Н ейос та т ком да нного ус трой ства явпяется небопьшие функционапьные возможности, закпючаюшиеся в том, что контроль импупьсов некоторого одноканапьного устройства требует допопнитепьных импульсов синхронизации.

Наибопее бпизким по технической сущности к предпагаемому является устройство дпя контропя поспедоватепьности импупьсо», состояшее из триггеров, образуюших регистр сдвига, входных погических эпементов, соейиняюших триггеры между собой и управпяемых сигнапами контропируемой поспедоватепьности, и бпока сравнения ) 2).

3 97 24 чем вход триггера переключения соединен с выходом первого входного логического элемента И, а его выходы соединены с управляюшими входами первого входного логического элемента И и допопнительного входного логического элемента И, основные входы которых подключены к первому входу блока контроля, выход последнего соединен с ВхоАВМН Aoiloлнительного триггера, выходы которого соединены с 10 входами выходного логического элемента

И и входного логического элемента И последнего триггера регистра, соединенного инверсным выходом с другим выходом выходного логического элемента И. 15

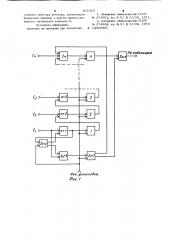

На фиг. 1 приведена функциональная схема устройства; на фиг, 2 - временные диаграммы.

Устройство содержи т триггеры 1, 3, .", p, образуюшие регистр сдвига, рр входные логические элементы И И+1, И+2, ..., 2д на которые поступают вход.»ые сигналы С4, C>, ..., С, дополнительный триггер 26+1, триггер переключения

2р+2, дополнительный входной логический 25 элемент И 2И+3, выходной логический элемент И 2и+4.

Устройство работает следуюшим образом.

Сигнал начальной установки (фиг. 26) Зр устанавливает все триггеры в исходное положение, это происходит в произвольный момент времении Ьо, 9 момент времени k когда появляется импульс С4 (фиг. 2,а4) на»ервом входе устройства триггера 1 (фиг. 2,a„) переходит в состояние "1", разрешая тем самым прохождение импульса С через входной логический элемент И И+2 на вход триггера 2,.

По заднему фронту импульса С„триггер переключения 2И+2 переходит в состояние "О (фиг. 2г).

В момент времени появляется сигнал С (фиг. 2,а ) на втором входе устройства и»ереводит триггер 2 в состоя- 45 ние 1" (фиг. 2,в ), что разрешит прохождение импульса С у через входной логический элемент И И+3 на вход триггера 3 и так далее (входные сигналы С, ..., C> показаны iia фи . 2,a . - .. аи, a co- 50 стояние триггеров 3, ..., g — на фиг. 2в

3,...,ви), Если в контролируемой последовательности импульсов не было пропусков или изменения в порядке следования, то к мо- 55 менту- времени - - когда появится очеред4! ной импульс С на первом входе устройства, послед»ий триггер регистра и будет находиться в состоянии 1 ", а дополнительный триггер 21 +1 в момент времени $ перейдет в состояние "1 (фиг.2д), так как триггер переключения 2p+2 пропустит импульс С 4 через дополнительный входной логический элемент И 28+3 на вход дополнительного триггера 2л+1. Последний сигналом со своего инверсного выхода закроет входной логический эле-мент И 2 последнего триггера И регистра, а также подает сигнал логической ."1 на один из входов выходного элемен.та И 2„ +4, ко второму входу которого подключен инверсный выход триггера М.

Отсутствие сигнала логической 1 на выходе выходного элемента И 2и+4 свидетельствует об отсутствии нарушений в контролируемой последовательности импульсов. После момента времени 4 входные сигналы уже не смогут изменить состояние триггера 1а которое и опреде ляет результат контроля. Таким образом, контроль выполняется в течение только

Л одного периода контролируемой последовательности импульсов (с момента времени +1 по kp ).

Предлагаемое устройство позволяет быстро обнаружить неисправный блок системы управления преобразователем.

Форму ла изобре тени я

Устройство для контроля схем управпения тиристорными преобразователями частоты, содержашее триггеры, соединенные между собой через входные логические элементы И в блок регистров сдвига, и выходной элемент И, о т п и ч а ю— ш е е с я тем, что, с целью повышения достоверности контроля, число триггеров блока регистров сдвига увеличено до числа контролируемых кана лов, в устройство

BBeAeHbI триггер переключения, дополнительный входной логический элемент И и дополнительный триггер, причем вход триггера переключения соединен с выходом первого входного логического элемента И, а его выходы соединены с управляюшими входами первого входного логического элемента И и дополнительного входного логического элемента И, основные входы которых подключены к первому входу блока контроля, выход»oc»еинего соединен с входом дополнительного триггера, выходы которого соединены с входами выходного логического элемента

И и входного поги еского элеменга И»o—

5 972415 4 спеднего триггера регистра, соединенного 1. Авторское свидетепьство СССР йнверсным выходом с другим входом вы- ¹ 374691, кп. G 01 R 31/28, 1971. ходного погического эпемента И. 2. Авторское свидетепьство СССР

Источники информации, ¹ 374558, кп. (01 Q 31/28, 1974 принятые во внимание при экспертизе (прототип).

Нач. цстакабка

Риг. /

97243 5

Составите пь В, Бочаров

Р;дактор g. Пипиненко Техред А.Бабинен корректор !. Бокшан

Заказ 8509/34 Тираж 7 17 Подписное

ВНИИПИ Государственного комитета СССР по депам изобретений и открытий

3 13035, Москва, Ж-35, Раушскаи наб., д. 4/5

<1>ипиап ППП "Патент, r, Ужгород, уп. Проектная,