Устройство для управления вводом-выводом информации

Иллюстрации

Показать всеРеферат

О.В. ><уравлев, В.И. Корнейчук, Ф.В. - Новиков, В,Н. Сорокко и l0.À. Ще гель с кий (72) Авторы изобретения

Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социахщстической революции (7!.) Заявитель (4) УСТРОйетВО ДЛЯ УПРАВЛСНИЯ ВВОДОИВНВОДОИ ИНфОРИА(ИИ

Изобретение относится к автоматике и вычислительной технике и может быть использовано для организации об мена информацией в системах коллективного пользования вычислительными . ресурсами, информационно-поисковых системах и проч.

Известно устройство для ввода-вывода информации, содержащее процессор, блок памяти, блок сопряг. ения и блок формирования тактовых сигналов с их связями (1 ).

Недостатком данного устройства яв. ляется ограниченные функциональные возможности при вводе больших массивов данных от наиболее приоритетных пользователей °

Наиболее близким по технической сущности к предлагаемому является устройство для ввода-вывода информации, содержащее блок обработки инструкции процессора, регистр связи с процессором, регистр масок, блок анализа приоритетов, регистр запросов, 2 блок выдачи адреса, блок выдачи дан- ° ных, подканалы по числу устройств ввода-вывода, каждый из которых содержит регистр управляющих слов, формирователь управляющих сигналов, ре5 гистр записи, регистр чтения, управляемый счетчик машинных тактов с их связями (2).

Недостатком известного устройства являются ограни ченные функциональные возможности.

Цель изобретения - расширение функциональных возможностей устройства путем организации приоритетного режима обмена информацией с внешними устройствами.

Укаэанная цель достигается тем, что в устройство для ввода-вывода ин-. формации, содержащее первый, второй и третий счетчики, формирователь импульсов, первый и второй регистры, введены первый, второй, третий и четвертый элементы И, группа элементов И, третий регистр, распределитель

3 .9724 ,импульсов, одновибратор, блок сравнения, первый, второй и третий дешифраторы, элемент ИЛИ, коммутатор и триггер, первый вход которого является первым входом устройства, второй вход соединен с выходом первого счетчика, прямой выход - с первым входом первого элемента И, инверсный выход - с первым входом устройства, второй вход первого элемента И соединен с выходом >е формирователя импульсов, с первым входом второго элемента И и с первыми входами элементов И группы, а выходс входами первого и второго счетчиков и с первым входом первого регист" 1

;ра, второй вход которого подключен к входу второго регистра и является вторым входом устройства, а выход - к первому входу распределителя, второй вход которого соединен с выходом вто- 2о рого счетчика, а выходы являются выходами первой группы устройства, выходы элементов И группы являются выходами устройства второй группы,. выход второго элемента И соединен с первым 25 входом третьего элемента И и с первым входом третьего регистра, второй вход которого подключен к выходу элемента ИЛИ, третий вход соединен с первым входом устройства, четвертый вход - зо с первым. входом третьего счетчика и с выходом одновибратора, первый выход - с вторым выходом устройства, второй выход - с входом первого дешифратора, прямой выход которого является третьим выходом устройства, а инверсный выход подключен к второму входу второго элемента И, входы группы элемента ИЛИ являются входами устройства первой группы, выход второго регистра соединен с первым входом блока сравнения, второй вход которого подключен к выходу коммутатора, первый выход является четвертым выходом устройства и соединен с входом одновибратора и с первым входом четвертого элемента И, второй выход - с вторым входом третьего элемента И, выход которого подключен к второму входу третьего счетчика, выход которого соединен с вторым входом четвертого элемента И, с выходом коммутатора и с входом второго дешифратора, выходы которого подключены к вторым входам элементов И группы, выход четвертого элемента И является пятым выходом устройства, входы коммутатора являются входами устройства второй группы.

94 4

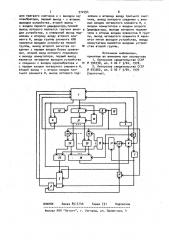

На чертеже приведена структурная схема устройства.

Устройство содержит процессор 1, первый и второй регистры 2 и 3, триггер 4, третий регистр 5, блок 6 сравнения, одновибратор 7, первый элемент И 8, первый дешифратор 9, первый счетчик 10, второй элемент И 11, второй счетчик 12, формирователь импульсов 13, элементы И группы 14, третий элемент И 15, четвертый элемент И 16, третий счетчик 17, коммутатор 18, второй дешифратор 19, терминалы 20, распределитель 21, элемент ИЛИ 22.

Устройство работает следующим образом.

Процессор 1 согласно программе устанавливает либо режим чтения, либо режим записи информации.

В режиме записи информации в термиалы 10 1 по информационной шине передает первую информационную посылку в регистр 2, в котором -я ячейка закреплена за i-м терминалом 20. Затем по шине установки процессор посылает сигнал, переводящий триггер 4 в состояние, разрешающее прохождение тактовых импульсов с формирователя 13 через элемент 8 на входы счетчика 10, счетчик 20 и сдвиговый вход регистра 2. В результате чего распределитель 21, управляемый счетчиком 12, содержимое ячеек регистра 2 поступает в соответствующие терминалы 20. В момент выдачи с регистра 2 последнего символа со счетчика 10 снимается сигнал, устанавливающий триггер 4 в состояние, запрещающее поступление тактовых импульсов через элемент 8, а с инверсного выхода триггера 4 формируется сигнал прерывания по записи, по которому процессор 1 выставляет .в регистр 2 новую,дозу информации. Операции продолжают ся до момента снятия режима записи информации.

В режиме чтения информации с терминалов 20 с выходной информационной шины процессора 1 s регистр 3 заносится код, соответствующий минимальному приоритету терминала 20, либо признак медленного терминала 20; затем по шине установки с процессора 1 снимается код, приводящий регистр 5 в исходное (нулевое ) сотояние,причем маркер записывается в первый разряд этого регистра. Если в маркерном разряде регистра 5 нулевой код, то с инверсФормула изобретения а выход - к первому входу распределителя, второй вход которого соединен с выходом второго счетчика, а выходы являются выходами первой группы устройства, выходы элементов И группы являются выходами устройства второй группы, выход второго элемента И соединен с первым входом третьего элемента И и с первым входом третьего регистра, второй вход которого подключен к выходу элемента ИЛИ, третий вход соединен.с первым входом устройства, четвертый вход - с первым вхо5 972"9 ного выхода дешифратора 9 снимается сигнал, разрешающий прохождение тактовых импульсов с Формирователя 13 через элемент 11. Тактовый импульс поступает на сдвиговый вход регистра 5, подготавливая его к приему кода с очередного терминала 20. Этот же сигнал"при условии, что код в регистре 3 большее или равен коду запроса, поступающему от терминала 20 через О коммутатор 18 в блок 6, переводит счетчик 17 в новое состояние, дешифрируемое дешифратором 19, как разрешение на подключение тактового сигнала от формирователя 13 через -й эле- 1$ мент 14 в -й терминал 20. В результа: те с терминала 20 считывается через элемент 22 код символа, записывающийся в регистр 5. Если код запроса с этого терминала 20 не превышает код 2о в регистре 3, то операции считывания по символу с каждого терминала 20 про. должаются до момента появления в последнем разряде регистра 5 кода маркеqa. В этот момент с инверсного выход 2

" дешифратора 9 снимается сигнал, запре щающий прохожде«ие тактовых импульсов через элемент 11, а с прямого выхода дешифратора 9 формируется сигнал прерывания процессора 1, по кото-.30. рому содержимое регистра 5 по информационной шине поступает в процессор 1.

Операция чтения продолжается после поступления по установочной шине процессора 1 кода установки в регистр 5. и

Если в процессе режима чтения обнаружен код запроса терминала 20, превышающий код, хранящийся в регистре 3, то с блока 6 снимается сигнал, запрещающий изменение адреса в счет- ац чике 17, а с другого выхода блока 6 попоступает сигнал в процессор 1 на его прерывание и разрешающий поступление кода адреса через элемент 16 в процессор 1, чем обеспечивается идентификация принимаемой информации. В этом случае считывание проводится так же, как и было показано, но символы в регистр 5 записываются только от одного, выбранного терминала 20.Опрос р остальных терминалов 20 продолжается после снятия запроса от терминала, имеющего высший приоритет. В этот момент одновибратор 7 по заднему фронту импульса Формирует в маркерном раз ряде регистра 5 для очищения его от ,информации и сбрасывает счетчик 17 в нуль. После поступления сигнала по .шине установки процессора 1 на регистр 5 устройство продолжает операции в режиме считывания.

При работе с терминалами одного типа изобретение позволяет использовать режим приоритетной выборки информации, что особенно важно в условиях автоматизированных систем управле" ния, где возникновение экстремальных ситуаций требует обработки в первую очередь информации и узла управления, являющегося источником этой ситуации, при условии, что остальные поль зователи обслуживаются равномерно.

Устройство для управления вводомвыводом информации, содержащее первый, второй и третий счетчики, Формирователь импульсов, первый и второй регистры, о т л и ч а ю щ е е с я тем, что, с целью расширения Функциональных возможностей путем органиэации приоритетного режима обмена информа" цией с внешними устройствами, в него введены первый, второй, третий и чет" вертый элементы И, группа элементов И, третий регистр, распределитель импульсов, одновибратор, блок сравнения, первый, второй и третий дешибра торы, элемент ИЛИ, коммутатор и триггер, первый вход которого является первым входом устройства, второй вход соединен с выходом первого счетчика, прямой выход - с первым входом первого элемента И, инверсный выход - с первым входом устройства, второй вход первого элемента И соединен с выходом формирователя импульсов, с первым входом второго элемента И и с первыми входами элементов И группы, а выход - с входами первого и второ" го счетчиков,и с первым входом первого регистра, второй вход которого подключен к входу второго регистра и является вторым входом устройства, Подписное

ВНИИПИ Заказ 8517/40 Тираж 731

° » филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

7 97249 дом третьего счетчика и с выходом одновибратора, первый выход " с вторым, выходом устройства, второй выходс входом первого дешифратора, прямой выХод которого является третьим выходом устройства, а инверсный выход подключен к второму входу второго элемента И, входы группы элемента ИЛИ являются входами устройства первой группы, выход второго регистра со- 10 единен с первым входом блока сравнения, второй вход которого подключен к выходу коммутатора, первый выход является четвертым выходом устройства и соединен с входом одновибратора и 15 с первым входом четвертого элемента И, второй выход - с вторым входом третьего элемента И, выход которого подключен к второму входу третьего счетчика, выход которого соединен с вторым входом четвертого элемента И, с входом коммутатора и входом второго дешифратора, выходы которого подключены к вторым входам элементов И группы, выход четвертого элемента И является пятым выходом устройства, входы коммутатора RBllAQTcR входами устройства второй группы.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 596938, кл. G 06 F 3/04, 1978, 2. Авторское свидетельство СССР

Ю 693362, кл. G 06 F 3/04, 1979 (прототип).