Программируемое логическое устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик!

>972500 (б1) Дополнительное к авт. свид-ву— (22) Заявлено 27. 02. 81 (21) 325171б/18-24 с присоединением заявки ¹â€” (23) Приоритет—

Опубликовано 071182. Бюллетень ¹ I 41

И11 М. g>.

6 Об F 7/ОО

Государствеииий комитет

СССР

ho делам. изобретений и открытий (И) УДК б81. .3(088.8) Дата опубликования описания 07. 11.82

Р

1

Ф

Ю.A.Hóçóíoâ, H.Н.Шипилов и Н.И.Бородин (72) Авторы изобретения (71 ) Заявитель (54) ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОИСТВО

Изобретение отйосится к вычислительной технике и может быть использовано, s частности, при разра ботке больших интегральных схем, (БИС) °

Известно логическое уотройство —, программируемое логические матрицы (ПЗЖ), размещаемые на одном кристал ле и содержащие матрицы логических элементов И, ИЛИ и триггеры flj, Недостатком этого устройства яв» ляется его низкая универсальность, обусловленная стандартным назначением внешних выводовг одна часть выво дов в них используется в качестве входов, а другая — в качестве выходов устройства.

Наиболее близким,к предложенному по технической ущности „является программируемый логический блок, содержащ@й матрицу основных и дополнительных логических элементов И, элементы ИЛИ и синхронизируемые триггеры

IX) .

Недостаткам известного устройства является ограниченность его примене ния, обусловленная однозначным распределением функций внешних выводов.

Одна группа выводов в устройстве ис пользуется в режиме "Вход устройст ва ", другая — только в режиме " 8N"" ход триггера", и,лншь третья группа выводов может использоваться как в режиме "Вход устройства", так и s

,режиме "Выход элемента ИЛИ". С помощью такого- устройства нельзя, например, реализовать комбинационнуго схему с числом выходов, йревышагощим число выводов третьей группы, поскольку выходные сигналы на выводах . второй группы будут запаздывать иа

:один такт относительно сигналов на выводах третьей группы. Кроме того, на соотношение числа входов и выхо15:дов схем, для реализации которых ,прегргазиачено устройство, нвлагаются кесткие ограничения. Все это сужает область применения устройства.

Цель изобретения — расширение об-: ) ласти устройства за счет перераспределения функций внешних выводов.

Поставленная цель достигается теиг, что программируемое лагцчеслгое устройство, содержащее многофункциональный логический элемент, содержит коммутирующие блоки, первЫй и второй вхо. дЫ каждого из которых подключены к. информационным выходай многофункцио нального логического. элемента со - ветственно, третин вход каждого ком972500 мутирующего блока подключен к входу синхронизации устройства, четвертый вход каждого коммутирующего блока подключен к внешнему выводу устройства, первый и второй выходы каждого коммутирующего блока соединены с 5 входами многофункционального логического элемента соответственно, при этом каждый коммутирующий блок содержит триггер, переключатели и комму. татор, управляющий вход которого 1О подключен к первому входу коммутирующего блока, второй вход которого подключен к информационному входу триггера и входу. первого переключа-. теля, выход которого подключен к пер-15 вому информационному входу коммутатора, к первому выходу коммутирующего блока и выходу второго переключателя, вход которого подключен к выходу триггера, вход синхронизации которо- Э)

rn подключен к третьему входу коммутирующего блока, четвертый вход которого подключен к второму информационному входу коммутатора, выход которого подключен к второму выходу ком" 25 мутирующего блока.

Коммутатор содержит элементы И и

HE причем первый информационный вход коммутатора подключен к первому входу первого элемента И, второй 30 вход которого подключен к управляюще.лу входу коммутатора и к входу элемента HF,, выход которого подключен к первому входу второго элемен-. та И, второй вход которого подключен З5 к выходу первого элемента И и к второму информационному входу коммутатора, выход которого подключен к выходу второго элемента И, Каждый коммутирующий блок содержит триггер, информационный вход которого подключен к второму входу блока, вход синхронизации — к третьему входу блока, а выход, через один переключатель — к первому информационному входу коммутатора, 45 соединенному также с первым выходом блока и, через другой переключательс вторым входом блока. Управляющий вход коммутатора соединен с -первым входом блока, его второй информацион- 50 ный вход - с четвертым входом блока, а выход - со вторым выходом блока.

Коммутатор содержит элементы И, причем управляющий вход коммутатора подключен к управляющему входу перво- 55 го элемента И и,через элемент НŠ— к управляющему входу второго элемента

И, первый информационный вход коммутатора соединен с информационным входом первого элемента И, второй информационный вход коммутатора подключен к выходу,.первого и к информа ционному входу второго элементов И, а выход коммутатора соединен с выхо" дом второго элемента И. 65

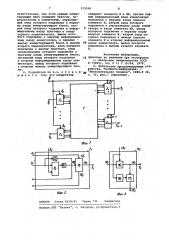

На фиг. 1 представлена структурная схема устройства; на фиг, 2 функциональная схема коммутирующего блока; на фиг. 3 — схема коммутатора.

Устройство (фиг. 1) содержит многофункциональный логический элемент

1 и и одинаковых коммутирующих блоков 2л — 2„,. Входы 3.;, 4, i-го коммутирующего блока (1 = 1 n) подключены к выходам элемента 1. Входы

5„ - 5 всех блоков 2; соединены с общим внешним выводом 6 устройства.

Каждый блок 2 „ подключен к своему внешнему выводу 7„- устройства, а оба выхода блока 2„ соединены со своими входами элемента 1 ° Коммутирующий блок 2„. (Фиг. 2) содержит триггер 8„, информационный вход которого соединен со входом 3 „ блока, т.е. с одним из выходов элемента 1. Синхронизирующий вход триггера 8 ° подключен

1 ко входу 5„блока, а его выход, через переключатель 9„- — к информационному входу 10„ коммутатора 11

Вход 10 коммутатора 11„, через переключатель 12„ связан также со входом 3 „ блока, и,непосредственно соединен с первым выходом блока, т.е. с одним их входов элемента 1. Управляющий вход 13; коммутатора 11 подключен ко входу 4- коммутирующего блока

2, т.е. к одному из выходов элемента 1. Вход 14 коммутатора 11,; соединен с внешним выводом 7> устройства,а выход 15„ - co вторым вйходом блока, т.е. с одним из входов элемента 1, Коммутатор 11 . (Фиг. 3) содержит первый 16„ и второй 17„- элементы И, причем управляющий вход 13„ коычутатора подключен к управляющему входу первого 16 и, через элемент НЕ 18„— к управляющему входу второго 17„ элементов И. Информационный вход 10». и выход 15„ коммутатора ll „ соединены, соответственно, с информационным входом первого 16„ и выходом второго 17„. элементов И, а информационный вход 14 „ коммутатора подключен к выходу первого 16 и к информационному входу второго 17„ элементов

И, Устройство работает следующим образом.

Для реализации некоторой комбинационной или последовательностной схемы на основе данного устройства, последнее подвергается предварительной настройке путем настройки многофункционального элемента 1. Каждый внешний вывод 7 . устройства, соедийенный с выходом коммутирующего блока

2(, может использоваться s любом из трех режимовг "Вход устройства", "Выход элемента 1 или "Выход триггера ",.

При этом в процессе работы устройства допускается динамическая смена режима "Вход устройства" на режим

"Выход элемента 1 ", или режима "Вход

972500

Формула изобретения

1. Программируемое логическое устройство, содержащее многофункциональный логический элемент, о т л и ч аю щ е е с я тем, что, с целью расширения области применения за счет перераспределения функций внешних выводов, содержит коммутирующие бло-, ки, первый и второй входы каждого иэ которых подключены к информационным выходам многофункционального логического элемента соответственно, третий вход каждого коммутирующего блока подключен к входу синхронизации устройства, четвертый вход каждого коммутирующего блока подключен к внеш.нему выводу устройства, первый и вто» рой выходы каждого коммутирующего блока соединены с входами многофункционального логического элемента соустройства " на режим "Выход триггера".

Выбор пары динамически сменяемых режимов осуществляется на этапе ггрограммирования устройства установкой переключателей 9„ и 12„, которые могут представлять собой, например, 5 выплавляемые перемычки.

Если размыкаются переключатели

9„, а переключатель 12. остается в замкнутом состоянии, вйход триггера

8„ отключается от информационного входа 10„. коммутатора 11„ и к этому входу оказывается подключенным выход элемента 1, соединенный со входом

3„ коммутирующего блока 2 . При этом сйгнал с указанного выхода элемента 15

1 поступает через переключатель 12; на вход элемента 1, подключенный к первому выходу коммутирующего блока

2.. Тем самым в устройстве обеспечивается обратная связь, необходимая, например, при реализации переключательных функций в скобочной форме.

Если при этом на управляющий вход

13 коммутатора 11„ с выхода элемен1 та 1, подключенного по входу 4„- блока

2;, поступает единичный сигнал, выход элемента 2, соедйненный со входом 3; блока 2,подключается коммутатором 22 к внешнему выводу 7 устройства.В этом случае вывод 7„ используется в режиме "Выход элемента 1 <. 30 Если на управляющий вход 13 коммутатора 11; поступает нулевой сигнал, выход элемента 1, соединен- ный со входом 3„ блока 2 °, отключа1У ется коммутатором ll „. от внешнего вывода 7„ устройства, вывод 7„ подключается ко входу элемента 1, соединенному со вторым выходом блока

2, и используется в режиме "Вход устройства". При этом обратная связь 46 через переключатель 12. в элементе 1

1 сохран яется.

Если на этапе програмирования устройства размыкается переключатель

12;, а переключатель 9„. остается в замкнутом состоянии, вйход элемента

1, соединенный со входом 3; блока

2„, отключается от информационного входа 10; коммутатора 11 и к нему оказывается подключенным выход триг- щ гера 8 . При этом сигнал с выхода триггера 8 - поступает такжеи на вход элемента 1, соединенный с первым выходом коммутирующего блока 2.. Тем самым обеспечивается обратная связь, необходимая при реализации последовательностных схем. Вывод 7„ устройства используется при этом либо в режиме

"Выход триггера" либо в режиме

1ю

Вход устройства. Порядок смены этих

fi режимов в процессе работы устройства аналогичен описанному порядку смены режимов "Выход элемента 1 — "Вход устройства ", В ходе .смены режимов коммутатор

11; работает следующим образом. 6$

Если на его управляющий вход 13; поступает единичный сигнал, первым элементом И обеспечивается передача сигнала от входа 10 коммутатора к его входу 24„ . При этом подачей нулевого сигнала с выхода элемента И 26 на управляющий вход второго элемента И

17„, выход последнего переводится в высокоимпеданс ое состояние,что равно. сильно отключению его от выхода 15.

1 коммутатора.

При подаче на вход 13; нулевого сигнала элементы И- 16;, 17; срабатывают в обратном порядке: выход элемента И 16„ отключается от входа коммутатора 14„., а вторым элементом

И 17„, обеспечивается передача сигнала от входа 14 „ коммутатора к его выходу 15„-.

Таким образом, в отличие от известного устройства все внешние выводы данного устройства, за исключением служебных (питание, синхронизация и т ° п.), являются равнозначными.

Их конкретное назначение задается на этапе программирования устройства и может, кроме того, меняться в динамчке его работы., На основе такого устройства можно реализовать комбинационную схему с отношением числа входов к числу -выходов от 1/ (n-1) до (и-1)/1, или последовательностную . схему с числом элементов памяти от

1 до (n-1) и с суммарным числом входов и выходов, не превышающим И а также различные комбинации таких схем с возможностью их динамической реконфигурации. Введение в устройство коммутирующих блоков обеспечивает многорежнмное использование его внешних выводов, позволяет, в частности, применять устройство в системах с двунаправленными шинами и расширяет его облас7ь применения по сравнению с известными устройствами.

972500

Puz. Ю

ВНИИПИ Заказ 6518/41 Тираж 731

Подписное

Филиал ППП "Патент"., r. Ужгород, ул.Проектная,4 ответственно, при этом каждый комму- тирующий блох содержит триггер, переключатели и коммутатор, управляющий вход которого подключен к первому входу коммутирующего блока, второй вход которого подключен к информационному,входу триггера и входу первого переключателя, выход кото-; рого подключен к первому информации" ному входу коммутатора, к первому - . выходу коммутирующего блока и выходу ,,второго-переключателя-вход которого подключен к выходу триггера, вход синхронизации которого подключен к третьему входу коммутирующего блока, четвертый вход которого подключен к второму информационному входу коммутатора, выход которого подключен к второму выходу коммутирующего бло3CB °

2. Устройство по п,1, о т л и ч а,ю щ е е с я тем, что коммутатор

К содержит элементы И и НЕ, причем первый информационный вход коммутатора подключен к первому входу первого элемента И, второй вход которого подключен к управляющему входу комья" татора и входу элемента HE выход которого подключен к первому входу второго элемента И, второй вход которого подключен к выходу первого элемента И и второму информационному

t0 входу коммутатора, выход которого подключен к выходу второго элемента

И.

Источники информации, д принятые во внимание при экспертиве

1. Авторское свидетельство СССР

Р 739651, кл. G 11 С 15/04 1979.

2 ° Логические программируемые уст-. ройства. Экспресс-информация..@ "Вычислительная техника q 1980,9 30, с. 16< рис.7 (прототип).