Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социапистических

Республик

9?2590 (61) Дополнительное к авт. свнд-ву— (22) Заявлено 130481 (21) 3271168/18-24 с присоединением заявки М (23) Приоритет—

Опубликовано 07.11,82. бюллетень Ко 41

Р М Кп з

G 11 С 11/00

Государственный комитет

СССР оо делам изобретений я отпрмтяй (53) УДК 681.327 (088.8) Дата опубликования описания 071182

В. К. Конопелько . 1:СЬ,,т °

/ I

У 1 И4 T ;>" / г» „, „))

Минский радиотехнический инстит

Щд (72) Авторы иэобретенн» (71) Заявитель (54) ЗАПОИИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминаю.

1щим устройствам и может быть использонано при создании систем памяти на базе интегральных запоминающих устройств .

Известно устройство, содержащее накопитель, схемы логики обрамления и коррекции, в котором при нераэрушающем считывании информации необходимо повторно инвертировать слово и производить его запись в накопитель 1).

Недостатком этого устройства является низкое быстродействие.

Наиболее близким техническим решением к изобретению является запоминающее устройство, содержащее накопитель, одни входы которого соединены с выходами адресного блока, выходы накопителя соединены с входами регистра кодового слова, нходами блока коррекции информации и первыми входами сумматоров по модулю два, вторыми входами соединениях с первыми выходами блока коррекции информации, вторые выходы которого соединены с входами блока определения допустимого числа ошибок, выходом соединенного с входом триггера, одни выходы сумматоров по модулю два соединены с пернычи входами выходного регистра, вторым

/ входом соединенного с соотнетстнуи& щим выходом сумматора по модулю дна, входной регистр, первые нходы кото5 рого соединены с шинами записи информации, шиной записи нуля и входами блока кодирования, вторые входы нходного регистра соединены с выходами блока лодирования(2). щ Недостатком этого устройства является то, что в нем в режиме записи производится контрольное считывание независимо от наличия и допустимого числа ошибок, что снижает его быстро-. действие °

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель, одни иэ входон которого соединены с выходами адресноно блока, а выходы подключены ко входам буферного регистра, входам блока коррекции информации и первым входам суьиаторов по модулю дна, блок кодирования информации, счетчик ошибок, триггер, входной и выходной регистры, причем вторые входы сумматоров по модулю дна соединены с одними иэ выходов блока коррекции информа97 2590 ции, другие выходы которого подключены ко входам счетчика ошибок, выход которого соединен с входом триггера, информационные входы выходного регистра подключены к выходам перного, второго и третьего сумматоров по модулю дна, а управляющий вход выход;ного регистра соединен с выходом четвертого сумматора по .модулю два, одни из входов и выходы блока кодирования информации подключены к од- 10 ним из выходов и входов входного

Регистра. другие входы которого соединены с другими входами блока ко. диронания информации и являются входами устройства, введен мультиплексор, одни из входов которого подключены соответственно к инверсным выходам буферного регистра и к выходу триггера, а другие входы — к другим ныходам входного регистра, выходы мультиплексора соединены с другими входами накопителя.

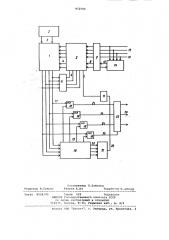

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит накопитель 1 со входами 2, адресный блок 3, входы 4, мультиплексор 5 со входами

6-8, входной регистр 9, буферный регистр 10, триггер 11, входы 12 и вход 13, предназначенные ссответстненно для записи информации и нулевого сигнала, блок 14 кодирования. с выходами 15, блок 16 коррекции информации со входами 17, первый 18.1, второй 18.2, третий 18.3 35 и четвертый 18.4.сумматоры по модулю два, выходы 19 и 20 блока коррекции информации, счетчик 21 ошибок с выходом 22, выходной регистр

23 с информационными 24 и управляю- 40 щим 25 входами и выходами 26.

Устройство работает следующим образом.

В режи.ле записи информации устройство работает обычным образом . Дан- 45 ные, поступающие по входам 12, дополненные нулевым символом на входе 13, поступают на входы регистра 9 и блока 14. Блок 14 вычисляет значения проверочных разрядов, которые; одновременно с информацией, поступающей по входам 12 и 13, помещаются н регистр 9 и далее н накопитель 1 по адресу, вычисленному блоком 3. При эФом на выходе 7 триггера 11 — нулевой сигнал. 55

В режиме считывания информации из "ячейки накопителя 1 перезаписывается в регистр 10 и одновременно поступает в блок 16. При этом возможны следующйе случаи: в слове нет 60 ошибок, имеется доПустимое число ошибок или больше допустимого числа.

Если в слове нет ошибок, т.е. вычисленный блоком 16 и поступающий на выходы 20 код равен нулю (S=O) g в 65 этом случае в триггер 11 запишется нулевой сигнал и на выходах 19 блока 16 также будут нулевые сигналы.

Считываемое слово через сумматоры

i8 1-18.4 и регистр 23 поступает без изменения на выходы 26 устройства.

Если в слове имеется допустимое число ошибок, тогда на выходах 20 код не равен нулю, но на выходе 22 блока 21 вновь нуленой сигнал, который запишется в триггер 11. На выходах 19 блока 16 поянится сигнал, кото рый исправит на сумматорах 18 ошибочно считыва емую информацию на прав ильв ную. При этом на выходе 25 четвертого сумматора 18. 4 будет нулевой сигнал и слово без изменения поступит на выходы 26 устройства.

Если в считываемом слове ошибок больше, чем их допустимое, но обнаруживаемое кодом число, тогда на выходах 20 код не равен нулю и на выходе 22 блока 21 появится единичный сигнал, который запишется в триггер

11 и разрешит повторную запись н накопитель 1 инвертированного кодового слова из регистра 10. При повторном считывании инверсного слова блок 16 вычислит значение кода S на выходах 20. Если при этом SQO и на ныходе 2 2 блока 21 будет в нов ь еди нич— ный сигнал, то это означает, что произошла некорректируемая ошибка.

Если же ЯФО и на выходе 22 блока 21 будет нулевой сигнал, то считываемое инверсное слово корректируется сигналами с выходов 19 блока 16. При этом на выходе 25 сумматора 18.4 появится единичный сигнал. Этот сигнал произведет инвертирование считываемого слова в регистре 23 и тем самым слово поступит на выходы 26 устройства правильным. На этом цикл считывания окончен. При повторном обращении к данному слову через какой-то промежуток времени при считывании по значению сигнала на ныходе 25 сумматора 18.4 можно определить, каким хранится слово: инвертиpoBBHHblM или нет. (Для того, чтобы инверсное слово также было кодовьм, необходимо, чтобы используемый код содержал слово, состоящее из одних единиц или в порождающей матри-це кода в приведенно-ступенчатом виде все столбцы имели нечетное число едийиц

Поясним сказанное примером с использованием удлиненного кода Хемминга с кодовым расстоянием Й, равньвл четырем, и проверочной матрицей Н!

0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0

0 1 1 1 0 0 0 1 1 1 1 0 1 0 0 0

Н = 1 9 .1 1 0 1 1 0 0 1 1 0 0 1 0 0

1 1 0 1 1 О. 1 0 1 0 1 0 0 0 1 0

1 1 1 0 1 1 0 1 0 0 1 0 0 0 0 14

972590

10

Формула изобретения

50

Применение данного кода в устройстве позволяет исправить один отказ, один сбой элементов памяти или два отказа элементов памяти. При появлении одной ошибки S Î и имеет нечетный вес, при появлении двойной ошибки 0 и имеет четный вес, что определяется блоксм 21, который выдает на вмход 22 в первом. случае нулевой сигнал, во втором случае единичный. При этом в считываемом слове либо нет ошибок, либо есть одна ошибка, либо появилось две ошибки.

Рассмотрим случай, когда появилось две ошибки.

Пусть они вызваны отказами элементов памяти. Тогда в триггер 11 запишется единичный сигнал и инверсное слово с регистра 10 запишется повторно в накопитель 1. При пов— торном считывании код инверсного слова равен нулю (SAO), так как несогласованная с состоянием отказавших элементов памяти информация стала согласованной. Однако на выходе 25 сумматора 18.4 появится единичный сигнал, который произведет инвертированиее инверсного считываемого слова в регистре 23, и исправ— ленное слово поступит правильным на, выходе 26 устройства.

Пусть ошибки вызваны одним отказом и одним сбоем элементов памяти.

В этом случае в триггер 11 запишется единичный сигнал и инверсное слово с выходов 6 регистра 10 запишется в накопитель 1. При повторном счйтыва нии код инверсного слова не равен нулю (5 0), но на выходе блока 21 будет нулевой сигнал, обозначающий наличие одной ошибки в слове,так как несогласованная с состоянием отказавшего элемента памяти информация стала согласованной, а инвертирование разряда с ошибкой из-за сбоя элемента памяти, не позволило сделать информацию согласованной, поскольку элемент памяти исправен.

Тогда на сумматорах 18.1-18.4 произойдет исправление ошибки из-за сбоя элемента памяти сигналами с выходов 19 блока 16. При этом на выходе 25 сумматора 18.4 будет единичный сигнал, который проинвертирует инверсное считываемое слово в регистре 23. С выходов 26 регистра 23 будет считываться исправленное слово.

Таким образом, в случаях, когда ошибок нет или число ошибок меньше или равно их допустимому числу, не производится контрольного считывания в режиме записи, как в известнсм уст ройстве, а слово поступает на выход скорректированным и время записи считывания информации из y«ñòðîéñòва уменьшено на один цикл контрольного считывания информации.

Технико-экономический эффект предлбженного устройства заключается в его более высоком быстродействии по сравнению с известкьм.

Запоминающее устройство, содержа— щее накопитель, одни из входов которого соединены с выходами адресного блока, а выходы подключены к входам буферного регистра, входам блока коррекции информации и первым входам сумматоров по модулю два, б.". < кодирования информации, счет:>ик ошибок, триггер, входной и выходкой регистр.i1, причем вторые входы сумматоро«в ио модулю два соединены с одними из гыхos«>в блока коррекции информации, другие выходы которого под.<лю <екы к входам счетчика ошибок, выход oторог0 соединен с входом триггера,. икформациок— ные входы выходного регистра подключены к выходам первого, второгo и третьего сумматоров по моду«.â два, а управляющий вход выходного регистра соединен с выходом четверто:o с -.клав тора по модулю два, одки «3 iõîäoè к выходы блока кодировакия информации подключены к одним из в.-входов и входов входного регистра, другие входы которого соединены с друг «<и их адами блока кодирования икфор мацки ляются входами устройства, о т .: и— ч а ю щ е е с я тем«что«е кель:.з повышения быстродействи —. у»тра ) =тва, в него введен мультиплексор, олк: из входов которого подкля««евы c(3c T ветственно к икверскым выхацам буферного регистра и к в,-:..:оду триггера, а другие входы — к др,гкм вых;— дам входного регистра,:-ыходы i

Источники информации, принятые so внимание при «<сперти::е

1. Самофалов К. Г., Ксркейчук П. И,Городний А.Б. Структурки-логиче<:кие

;летоды повышения надежности зап<ж <нающих устройств. М., "Г1ашикостре»ние", 1976, с.51-63.

2. Авторское свиде=ельство СССР по заявке Р 2926461/18-24, кл. G 11 С 11 00, 03. 03. 81 (кротов тип) .

972590

Составитель Т.Зайиева

Текр A.Alg Корректор М.немчик

Редактор Н.Гунько

Тираж 622 Подписное

ВНИНПИ Государственного комитета СССР по делам изобретений и открытий

1130 35, москва, Ж-35, Раушскан наб °, д ° 4/5

Заказ 8526/45

Филиал ППП "Патент", г. Ужгород, ул, Проектная, 4