Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

<11972598 (61) ???????????????????????????? ?? ??????. ????????-???? (22) ????????????????15 04 81> (21) 3275294/18-24

51 М Кл з

G 11 С 29/00 с присоединением заявки ¹

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано07.11.82. Бюллетень ¹ 41 (53) УДК 681. . 327 (088. 8) Дата опубликования описания 07. 11.82 (72) Автор изобретения

Л.О.Беспалов (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ

КОНТРОЛЕМ

Изобретение относится к запоминающим устройствам и может быть исполь . зовано в составе специализированных цифровых вычислительных машин (СПВМ) или систем обработки и передачи цифровых данных.

Известно запоминающее устройство с автономным контролем, содержащее два поля памяти, одно из которых 10 служит для хранения информации, а в другом расположено содержимое адреса ячейки Зу, к которой в настоящий момент происходит обращение, а также содержит адресный блок, включающий регистр адреса и дешифратор адресов, выходной ..регистр и схему сраннения текущего адреса с содержимым, хранящимся в дополнительной части ячейки поля памяти, выбираемой по этому адресу (1).

Недостатком этого устройства является отсутствие в его составе средств контроля информационной части, а также тракта дешифратора и накопителя, что снижает его надежность. 25

Наиболее близким техническим решением к изобретению являешься запоминающее устройство е антономным . контролем содержащее регистр адре« са, ныход которого через дешифратор З0 адресов подключен ко входу накопителя, соединенного соответствующими выходами со входами регистра, причем любая ячейка памяти наряду с информационной частью имеет дополнительные разряды. в которых хранятся контрольные признаки свертки (например, по модулю 2 или 3), относящиеся как к коду числа, так и к коду адреса, по которому выбирается данная ячейка (2) .

Недостатком известного устройства является низкая разрешающая способность автоматического определения места неисправности, что снижает его надежность.

Белью изобретения является II0Bbi шение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее регистр адреса, выходы которого соединены .с первым входом дешифратора адреса и входами перного блока свертки по модулю два, выход которого подключен к первому входу первой схемы сравнения, накопитель, входы которого соединены с выходами дешифратора адреса, а выходы — c входами регистра числа, информационные

972598

Формула изобретения выходы которого являются информационными выходами; устройства и подключены к входам второго блока свертки по модулю два, выход которого соединен с первым входом второй схемы сравнения, контрольные выходы ре- э гистра числа подключены соответственно к втоРым входам схем сравнения, выходы которых являются контрольными выходами устройства, Введены триггер, элементы ИЛИ, элемент задержки и эле- Ц мент И, причем входы первого элемен" та ИЛИ соединены с выходами накопителя, а выход подключен к входу элемента задержки, выход которого соединен

C первым входом второго элемента ИЛИ, g выход которого подключен к нулевому входу триггера, единичный вход которого соединен с выходом элемента И и вторым входом дешифратора адреса, выход триггера является индикаторным выходом устройства и подключен к первому входу элемента И, второй вход которого является входом опроса устройства, установочным входом которого является второй вход второго элемента ИЛИ.

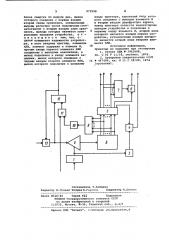

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит регистр 1 адреса, дешифратор 2 адреса, первый блок 3 свертки по модулю два, первую схему 4 сравнения, регистр 5 числа, вторую схему б сравнения, второй блок

7 свертки по модулю два, накопитель

8, первый элемент ИЛИ 9, элемент 10 задержки, второй элемент ИЛИ 11, 35 триггер 12 и элемент И 13.

Предложенное запоминающее устройство (ЗУ) работает следующим образом.

На вход элемента И 13 подается 4О сигнал опроса,, а на вход регистра

1 — код адреса, который свертывает-. ся при помощи блока 3. Далее результаты свертки подаются на один из входов схемы 4 сравнения. Сигнал оп.роса, пройдя через элемент И 13,производит установку триггера 12 в единичное состояние (соответствующее неисправности) и поступает на вход дешифратора 2, управляемого регистром

1. При наличии сигнала опроса на входе дешифратора 2 на одном иэ его выходов появляется сигнал при помощи, которого выбирается информация из соответствующей ячейки накопителя 8.

0 выхода накопителя 8 считанная информация поступает на вход регистра

5 и на вход элемента ИЛИ 9, с выхода которого через элемент 10 задержки обобщенный сигнал подается на нулевой вход триггера 12 и производит @ его установку в состояние, соответст-. вующее исправности устройства. При этом предполагается наличие в инФормационной или контрольной частях накопителя 8 хотя бы одной единицы. 65

С выхода регистра 5 информация считывается иэ ЗУ. Информационная ее часть при помощи блока 7 сверты вается по заложенным контрольным . признакам. Результаты свертки сравниваются с контрольным (контрольны,ми) признаком схемой б сравнения.

:Контрольный признак адреса с первого выхода регистра 5 поступает на вход схемы 4 сравнения. B случае правильности результатов на схемах 4 и 6, а также установки триггера 12 в нулевое состояние на выходах схем 4 и б и триггера 12 присутствуют сигналы исправности ЗУ.

В случае обрыва цепей дешифратора

2 выбор ячейки по этому адресу не ° производится и информация из накопителя 8 не считывается . Триггер

12 остаемся в состоянии неисправности. При этом неисправность типа

"обрыв " в информационной части накопителя 8 обнаруживается при помощи схемы 6 сравнения. При неисправности типа 1 обрыв < в частях контрольных разрядов накопителя 8 неисправность проявляется аналогично обрыву цепей дешифратора 2, Для осуществления повторного опроса и отнесения проявленной неисправности либо к неисправностям типа

"случайный сбой, либо отказ " в состав ЗУ введен элемент ИЛИ 11, при помощи которого осуществляется извне устройства гашение триггера 12 и установка его в состояние исправности ЗУ.

Таким образом, использование новых элементов — триггера, элементов

И, ИЛИ и элемента задержки с их связями позволяет охватить оперативным контролем тракты прохождения сигнала опроса через дешифратор 2 и накопитель 8, в результате чего повышается разрешающая способность средств встроенной диагностики и, следовательно, надежность устройства.

Технико-экономическое преимущаст" во предложенного устройства заключа ется в его болев высокой надежности по сравнению с известным.

Запоминающее устройство с автономным контролем, содержащее регистр адреса, выходы которого соединены с первым входом дешифратора адреса и входами первого блока свертки по модулю два, выход которого подключен к первому входу первой схемы сравнения, накопитель, входы которого соединены с выходами дешифратора адреса, а выходы — с входами регистра числа, информационные выходы которого являются информационными выходами устрой" ства и подключены к входам второго

972598

Составитель Т.Зайцева

Редактор H.Ãóíüêo Техред М.Гергель Корректор М.Демчик

Заказ 8526/45 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", г.ужгород ул.Проектная,4 блока свертки по модулю два, выход которого соединен с первым входом ,второй схемы сравнения, контрольные выходы регистра числа подключены соответственно к вторым входам схем срав нения, выходы которых янляются контрольными выходами устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены триггер, элементы

ИЛИ, элемент задержки и элемент И, 0 причем входы перного элемента ИЛИ соединены с выходами накопителя, а выход подключен к входу элемента sa»» дерзки, ныход которого соединен с первым входом второго элемента ИЛИ, 15 ныход которого подключен к нулевому

I входу триггера, единичный вход которого соединен с выходом элемента И и вторым входом дешифратора адреса, выход триггера является индикаторным выходом устройства и подключен к первому входу элемента И, второй вход которого является входом опроса устройства, установочным входом которого является второй вход второго элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1. Патент США Ю 3963908, кл. G 06 F ll/10, опублик. 1975.

2. Авторское свидетельство СССР

В 467409, кл. G 11 С 29/00, 1974 (прототип). !