Микропроцессор

Иллюстрации

Показать всеРеферат

Союз Советск их

Социалистичесиик

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свид-ву— (22) Заявлено06.05,81. (21) 3272801/18-24 с присоединением заявки М— (23) Приоритет—

Опубликовано 15.11.82. Бюллетень М 42 (51)М. Кл.

G 06 F 15/ОО

@еударетвенный квинтет

СССР во делаи нза4ретеннй н открытий (53) УД К681.325 (088. 8) Дата опубликования описания 15.11.82

А. К. Баумс, Г.Э. Васариньш, В. Т. Ермолов А. А. Чипа, A. К. Берзиньш, П. О. Видениекс и В. Э. Пекаревич (1 (72) Авторы изобретения

Институт электроники и вычислительной техникн АН-Латвийской ССР, и Рижское производственное обьединение ВЭФ йм." В . И.. Ленина. (71) Заявители (54) МИКРОП POIIEÑÑÎÐ

1

Изобретение относится к вычислительной технике.

Извес тен микропроцессор, содержащий блок управления, арифметический блок, память блок регистров, генератор, счетчик, триггеры, коммутатор регистры f1) . 5

Недостатком известного устройства является большой обьем обрудования и недостаточное быстродействие.

Наиболее близким к предлагаемому является микропроцессор, содержащий блок управления, арифметический блок, блок регистров, логический коммутатор, буферные регистры адресов и данных, счетчик, дешифраторы, регистр вектора прерываний, управляющую память, груп; пу регистров, буферный регистр (2) Известное устройство характеризуется недостаточной эффективностью из-за потребности специального комплекта больших интегральных схем и большого количества вспомогательных интегральных схем.

11елью изобретения является повыш ние коэффициента использования оборудования.

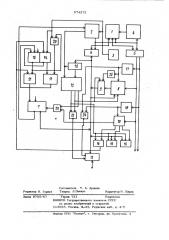

Поставленная цель достигается тем, что в микропроцессор, содержащий генерагор, выход которого соединен с первыав ми входами блока управления и синхронизации и первых элемента И и триггера, выходы которых через счетчик соединены с первым входом второго триггера, выход которого соединен с вторым входом первого элемента И и первым входом второго элемента И, выход которого соединен с первым входом регистра вектора прерываний, второй вход которого Соединен с входом микропроцессора, первый выход регистра вектора прерываний соединен с вто-. рым входом блока управления и синхронизации, первый выход которого соединен с первыья входами арифметического бло» ка, блока регистров, буферного регистра адресов и буферного регистра данных, выход которого и блока регистров соединены с вторым и третьим входами арифметичес3 4 ров, буферный регистр 5 адресов, буферный регистр 6 данних, регистр 7 вектора прерываний, управляющую память 8, буферный регистр 9, регистр 10 управляющего слова, счетчик 11, логический коммутатор 12, двунаправленный коммутатор

13, триггеры 14 и 15, регистры 16 группы, дешифраторы 17 — 19, элементы

И 20-22, элементы И-НЕ 23 и 24, элемент НЕ 25.

Устройство работает следующим образом.

По сигналам с генератора 3 арифметический блок 1 выдает в буферный реги-стр 5 текущий адрес команд или данных, хранимый в блоке 4, а,блок 2 вырабатывает управляющее словс, которое через регистр 6 передается в регистр 10 и, трансформируясь через логический коммутатор 12, определяет направление потока информации. В выборе направления потока информации участвуют также старшие разряды регистра 5 и содержимое управляющей памяти 8, согласно которому управляются соответствующие регистры 16.

Буферный регистр 9 перадает информацию от .управляющей памяти 8 в буферный ре гистр 6 по сигналу с элемента HE u сигналу с логического коммутатора 12 при срабативании дешифратора 17. Это позволяет исключить одновременную работу арифметического блока 1 с регистром 9 и с одним .из регистров 16.

При наличии указанного слова в управляющей памяти 8 и срабатывании дешифраторов 18 и 19 по сигналу с логичес— кого коммутатора 12 через элемент И

22 устанавливается в соответствующее состояние- регистр 7, Обмен управляющей блока 2 с помощью двунаправленного коммутатора 13, регистров 1 6 и элемента

И-НЕ 23 и 24.

Обслуживание затребованных прерыва. ний осуществляется с помощью одного из регистров 16, сигнал с которого устанав-ливает триггер 14 в единичное состояние и разрешает работу счетчика 11.

При этом триггер 15 устанавливается в нулевое состояние и через элемент И

20 пропускает импульсы счета на счетчик 11. По окончании счета выходной сигнал со счетчика 11 устанавливает триггер 15 в единичное состояние и просмотр (обработка прерываний ) заканчивается, о чем сигнализирует регистр 7 в бпок 2.

Изобретение позволяет сократить количество применяемых интегральных схем и повысить эффективность использования оборудования.

3 19 743 7 кого блока, соединенного двусторонней связью с буферным регистром адресов, первый выход которого соединен с входами первого и второго дешифраторов и первым выходом микропроцессора, второй выход которого соединен с вторым выходом буферного регистра адресов и первыми входами памяти и третьего дешифратора, выход которого соединен с первым входом третьего элемента И, выход кото- l0 рого соединен с третьим входом регистра вектора прерываний, группа выходов тр тьего дешифратора соединена с первыми входами группы регистров, второй выход блока управления и синхронизации и вы- д ходы регистра управляющего слова соединены с входами логического коммутатора, первый выход которого соединен с,,вторым входом третьего элементэ. И, второй выход логического коммутатора соединен с вторым входом управлякецей памяти и первым входом буферного дешифраdopa соединен с третьим входом управляю-. щей памяти, выход которой соединен с вторым входом буферного регистра, двуна=правленный коммутатор, соединенный шиной связи с входами буферного регистра данных, регистра управляющего слова, с

-. четвертым входом управляющей памяти, вторыми входами регистров группы, выходом буферного регистра и вторым выходом вектора прерываний, выход второго дешифратора соединен с вторым входом третьего дешифратора, выходы регистров группы соединены с группой выходов микропроцессора, введены два элемента

И-НЕ, элемент НЕ, причем, третий выход логического коммутатора соединен с третьими входами регистров группы и с первым входом первого элемента И-НЕ, вто40 рой вход и выход которого соединены соответственно с вторым выходом логического коммутатора и с первым входом двунаправленного коммутатора, второй вход которого соединен с выходом второго элемента И-НЕ, входы которого соедине4S ны с выходами первого и второго дешифраторов, выход первого дешифратора через элемент HE соединен с третьим входом буферного регистра, выход одного из регистров группы соединен с входами второ- 0 го элемента И и первого триггера, один из выходов которого соединен с вторым входом второго триггера.

На чертеже приведена блок-схема микSS роп роцесс ора.

Mmponponeccop содержит арифметический опок 1, олок 2 управления и синхронизации, генератор 3, блок 4 регист5 9743

Формула изобретения

Микропроцессор, содержаший генератор,. выход которого соединен с первым входом блока управления и синхронизации и первых у элемента И и триггера, выходы которых через счетчик соединены с первым входом второго триггера, выход которого соединен с вторым входом первого элемента И и первым входом второго элемента И; вы-1р ход которого соединен с первым входом регистра вектора прерываний, второй вход которого соединен с входом микропроцессора, первый выход регистра вектора пре-. рываний соединен с вторым входом блока 1 управления и синхронизации, первый выход которого соединен с первыми входами арифметического блока, блока регистров, буферного регистра адресов и буферного регистра данных, выход которого и блока регистров соединены с вторым и третьим входами арифметического блока, соединенного двусторонней связью с буферным регистром адресов, первый выход которого соединен с входами первого и втрого дешифраторов и первым выходом микропроцессора, второй выход которого соединен с вторым выходом буферного регистра адресов и первыми входами управляюшей памяти и третьего дешифратора, выход которого соединен с первым входом .третьего элемента И, выход которого соединен с- третьим входом,регистра вектора прерываний, группа выходов третьего дешифратора соединена с первыми входами . группы регистров выход блока управления и синхронизации и выходы регистра управляклцего слова соединены с входами логического коммутаторе, первый выход кото рого соединен с вторым входом третьего элемента И, второй выход логического

° 9 коммутатора соединен с вторым входом управляюшей памяти и первым входом буферного,регистра, выход первого дешиф73 ратора соединен с третьим входом управляюшей памяти, выход которой соединен с вторым входом буферного регистра, двунаправленный коммутатор, соединенный шиной связи с входами буферного регистра данных, регистра управляюшего слова, с четвертым входом управлякшей памяти, вторыми входами регистров .группы, выходом буферного регис.тра и вторым выходом регистра вектора прерываний, выход второго дешифратора, соединен с вторым входом третьего дешифратора, выходы регистров группы соединены с: группой выходов микропроцессора, - о r л и ч аю ш и и с я тем, что с целью повышения коэффициента использования оборудования, в него введены два элемента И-Hb, элемент НЕ, причем, третий выход логического коммутатора соединен с третьими входами регистров группы и с первым входом первот о элемента

И-НЕ, второй вход и выход которого соединены соответственно с вторым выходом логического коммутатора и с первым входом двунаправленного коммутатора, второй вход которого соединен с вьмодом второго элемента И-НЕ, входы которого соединены с выходами первого и второго дешифраторов, выход первого дешифраторов, выход первого дешифратора через элемент HE соединен с третьим входом буферного регистра, выход одного из регистров группы соединен,с вторыми входами второго элемента И и первого триггера, один из выходов которого соединен с вторым входом второго триггера.

Источники информации принятые во внимание при экспертизе

1. Авторское свидетельство . СССР

¹ 693377, кл. Ь 06 F 15/00, 1975.

2."EPect on>c Des + ",1979, ¹5, (прототип) ц пс ф, Па М1сго— готорн Сег Data Ио пМ .

974373

Тираж 731 П одписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 8705/67

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составител» Т. А. Арашев

Редактор Н. Горват Техред Л.Пекар» Корректор Н, Буряк