Интегрирующий преобразователь напряжения в код

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

«I>974566 (61) Дополнительное к авт, свид-ву(22) Заявлено 171180 (21) 3219755/18-21 с присоединением заявки №вЂ” (23) Приоритет— (51)М Кл з

Н 03 К 13/02

Госулярствеииый комитет

СССР ио «елам изобретений и открытий

Опубликовано 15.1182 Бюллетень ¹ 42

{ЗЗ}УДК 681.325 (088.8) Дата опубликования описания 151182 (72) Авторы изобретения

Н.П.Вашкевич и Л.Н.Панков! г г г

Пензенский политехнический институт (73) Заявитель (5 и ) ИНТЕГРИРУИЦИЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ

В КОД

Известно также устройство, содержащее первый и второй интеграторы, при этом вход первого интегратора через коммутатор соединен с входной шиной устройства, вход второго интЕгратора через коммутатор соединен с шинами источника эталонных напряжений, выходы первого и второго ин25 теграторов соединены с входами блока сравнения, выход которого соединен с входом блока управления и формирования кода, выходы последнего соединены с входами у, равления коммутатора, первого и второго интегратоЗо ров -, 1

Изобретение относится к измеритель. ной и вычислительнои технике и используется в информационно-вычислительных системах.

Известны устройство интегрирующего уравновешивания преобразуемых величин (напряжений или токов) с помощью эталонных величин (напряжений или токов1, содержащее интегратор, первый и второй входы которого через коммутатор соединены с входной шиной устройства и с шинами источника эталонных напряжений соответственно, а выход соединен с первым входом блока сравнения, второй вход которого соединен с общей шиной устройства, а выход — соединен с входом блока управления и формирования кода, выходы последнего соединены с входами управления коммутатора и интегратора 1)

Недостатком данного устройства является низкая точность преобразования.

Известно устройство интегрирующего уравновешивания с переменной длительностью тактов преобразуемых величин (напряжений или токов) с помощью эталонных величин, содержащее интегра"тор, первый, второй и третий входы которого через коммутатор соединены с входной шиной устройства и с шиной источника эталонных напряжений соответственно, выход интегратора

5 соединен с первым входом блока сравнения, второй вход которого соединен с шиной источника эталонных напряжений, а выход — с входом блока управления и формирования кода, выходы которого соединены с входами управления коммутатора и интегратора(.2)..

Недостатком данного устройства является низкая точность преобразова15

974566

Недостатками данного устройства являются низкие точность преобразования и надежность.

Цель изобретения — повышение надежности и точности преобразования устройства. 5

Поставленная цель достигается

1тем, что в интегрирующем преобразова:теле напряжения в код, содержащем первый интегратор, первый вход которого через коммутатор соединен с 10 входной шиной, второй вход — с первым выходом блока управления и формирования кода, а выход — с первым входом блока сравнения, второй вход которого соединен с выходом второго интегратора, первый вход которого соединен с первым выходом блока управления и формирования кода, второй вход через коммутатор соединен с шиной источника эталонного напряжения, первый, второй и третий управляющий входы коммутатора соединены соответственно со вторым, третьим и четвертым выходом блока управления и Формирования кода, вход которого соединен с выходом блока сравнения, третий вход первого интегратора через коммутатор соединен с шиной источника эталонного напряжения..

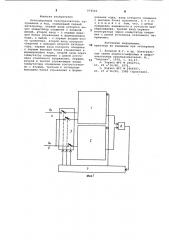

На фиг.1 представлена структурная электрическая схема устройства; на фиг 2—

4 — диаграммы изменения напряжения .

Схема содержит интеграторы 1 и 2, коммутатор 3, входную шину 4 устройства, шину 5 источника эталонного напряжения, блок 6 сравнения, блок 7 управления и формирования кода.

Первый вход интегратора 1 через коммутатор 3 соединен с входной шиной 4 устройства. Второй вход интег- 40 ратора 1 и вход интегратора 2 через коммутатор 3 соединен с шиной 5 источника эталонного напряжения. Выходы интеграторов 1 и 2 соединены с входами блока 6 сравнения, выход ко- 45 торого соединен с входом блока 7 управления и формирования кода. Выходы блока 7 управления и формирования кода соединены с входами управления коммутатора 3 и интегратора 1 и 2.

Устройство работает следующим образом.

Перед началом преобразования сигналом из блока 7 управления и формирования кода интегратор 1 и 2 обнуляются. В первом такте преобразования (фиг.2) Н еН е 0> с входной шины 4 устройства передается коммутатором 3 на первый вход интегратора 1. Эталонное напряжение 00 с шины 5 источника эталонного напряже- 60 ния коммутатором 3 передается на вход интегратора 2. В течение времени Т интеграторы 1 и 2 интегрируют напряжение с одинаковой постоянной времени. Напряжения с выходов интеграторов 1 и 2 поступают в блок

6 сравнения, где выполняется их сравнение и выработка сигналов х и х результата сравнения. Сигналй х и х используются в блоке 7 управленйя и формирования кода для управления преобразованием в следующем такте. Если 0> „<0 ??, =1),то ???? ???????????? ?????????? ???????????????????????????? ?????????????????? ???????????????????? u?? ???? ?????????????? ???????????????????? ???????????????????????? 3 ???????????????????? ???? ???????????? ???????? ?????????????????????? 1. ?????? ???????????? 0 ??„)

0 или 0 р таким образом, что

1 напряжение разности между ними уменьшается.

Аналогичным образом выполняются такты уравновешивания с интегрированием эталонного напряжения U в течение последующих интервалов времени Т- = 2 ", где - б 5 И,а q — количество разрядов. По результатам сравнения х „ и х„ блок 7 управления и формирования кода вырабатывает код преобразуемого напряжения и м=т+.х (х„-м )2. ()

11 1 1

При преобразовании знакопеременных напряжений 0 вместо эталонного напряжения 0 в йервом такте преобразования на вход интегратора 2 коммутатором 3 подается нулевое напряжение с общей шины источника эталонного напряжения. Диаграммы изменения напряжения 0 р и 0 при преобразовании положительного напряжения

U представлены на фиг.3„ а при преобразовании отрицательного напряжения О,, — на фиг.4.

Повышение точности преобразования достигается за счет применения источника однополярного эталонного напряжения, так как при этом отсутствует составляющая погрешности, обусловленная наличием второго источника эталон ного напряжения и неидентичности его напряжения с первым.

Таким образом, предлагаемое устройство обеспечивает повышение надежности и точности преобразования напряжения в код.

974566

Формула изобретения

Интегрирующий преобразователь напряжения в код, содержащий первый

:интегратор, первый вход которого через коммутатор соединен с входной шиной, второй вход — c первым выходом блока управления и формирования кода, а выход — с первым входом блока сравнения, второй вход которого соединен с выходом второго интегратора, первый вход которого соединен с первым выходом блока управления и формирования кода, второй вход через коммутатор соединен с шиной источника эталонного напряжения, первый, второй и третий управляющие входы коммутатора соединены соответственно с вторым, третьим и четвертым выходами блока управления и формирования кода, вход которого соединен с выходом блока сравнения, о т л ич а ю шийся тем, что, с целью повышения надежности и точности преобразования, третий вход первого интегратора через коммутатор соединен с шиной источника эталонного напряжения.

Источники информации, 10 принятые во внимание прн экспертизе

1. Балакай В.Г. и др. Интегральные схемы аналого-цифровых и цифроаналоговых преобразователей. М., "Энергия", 1978, с. 62,67.

2. Заявка ФРГ 9 2052753, кл. 21 а 36/00, 1971.

3. Заявка ФРГ М 2404597, кл. 21 а 36/00, 1980 (прототип).

974566

Редак тор Л. Доли нич

8734/77 Тираж 959 Подписное

В ИАПИ Государственного комитета СССР по делам изобретений и открытий

113035, Мое»ва, Ж-35, Раушская наб., д. 4/5

Заказ

Ф. лиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Фиг. 1

Фиг,Ф

Составитель А. Кузнецов

Техред Т.Маточка Корректор Н.Король