Устройство для логической обработки цифровых данных

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<>978141

Союз Советских

Социалистических

Республик с

/ (61) Дополнительное к авт. саид-ву (22) Заявлено 03.0281 (21) 3244117/18-24

1 с присоединением заявки М

Р11М К з

G 06 F 7/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

f53) УД (e81 ° 3 (088.8) Опубликовано 30.11,82. Бюллетень Мо 44

Дата опубликования описания 3(11L82.Б. "Сурков .: =.- „

-" а ( е 6 Ы (72) Авторы изобретения

A.È. Дралин, Г.И. Князев, E.H. Михайлов и

1

"Ю 1) (73) Заявитель (54) УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОЙ ОБРАБОТКИ

ЦИФРОВЫХ ДАННЫХ

Изобретение относится к вычисли- тельной технике и предназначено для обработки цифровых данных.

Известно устройство для логической обработки цифровых данных, выполненное в виде многофункционального логического модуля, содержащего элементы

И, выходы которых соединены с входами элемента ИЛИ, а входы соединены с входными шинами непосредственно и через инверторы (1).

При построении устройства с внутренней памятью для логической обработки цифровых данных (автоматов) при применении такого многофункционального логического модуля необходимо в устройство вводить элементы памяти, из-за большой избыточности реализующего оборудования устройство получается сложным.

Известны дискретные устройства— автоматы с так называемой стандартной структурой. Они состоят из части устройства с элементами памяти и комбинационной.части, в которой сосредоточены логические элементы логичес. кого преобразователя. В каждом такте работы дискретного устройства на выкодах логического преобразователя в зависимости от входных сигналов и сигналов на выходах элементов памяти вырабатываются сигналы, часть из которых является выходными сигналами дискретного устройства в данном такте работы, другая часть сигналов передается на входы элементов памяти и будет использована в следующем такте работы дискретного устройства (2).

При двоичном кодировании внутренних состояний автомата в общем случае значительно усложняется логический преобразователь, а при единичном или противогоночном кодировании внутренних состояний усложняется логический преобразователь и увеличивается количество элементов памяти. Устройство в целом отличается сложностью иэ-за большого количества элементов реализующего оборудования и связей между элементами °

Наиболее близким по технической сущности к предлагаемому является устройство для логической обработки цифровых данных на программируемых логических матрицах (ПЛМ) с логической структурой И-ИЛИ. Оно содержит триггеры, элементы И (матрицу И), элементы ИЛИ (матрицу ИЛИ), информационный вход каждого триггера соединен с выходом соответствующего элемента

978141

ИЛИ, входы которых соединены с выходами элементов И, входы синхронизации триггеров соединены с шиной временного сигнала, которая является шиной синхронизации устройства (3). недостаток такого устройства эаклю-5 чается в большой избыточности элементов И в ПЛИ, котопые не используются при реализации в конкретном устройстве, что усложняет устройство в целом., Объясняется это тем, что изготовлен- 10 ная ПЛМ до ее программирования. представляет достаточно универсальную структуру, ориентированную на одновременную реализацию возможно бОльшего числа нулевых функций, представленных в дизьюнктивной нормальной форме. После программирования ПЛИ для конкретного применения, ее перенастройка и перенастройка всего устройства на выполнение других фунКций за- 2О труднительны или невозможны.

Цель изобретения — упрощение и обеспечение многофункциональности устройства.

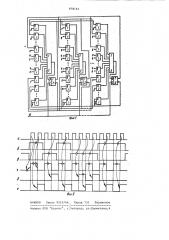

Поставленная цель достигается тем, 5 о что в устройстве для логической обработки цифровых данных, содержащем элементы И, ИЛИ,- триггеры, причем информационный вход каждого триггера соединен с вьйодом соответствующего элемента ИЛИ, входы которых соединены с выходами элементов И соответствующей группы, входы синхронизации триггеров соединены с шиной синхронизации устройства, первые входы элементов И каждой группы соединены с выхо- 35 дами триггеров и входными шинами устройства соответственно, а вторые входы соединены с шинами настройки устройства. . На фиг. 1 представлена схема пред-40 лагаемого устройства для логической обработки цифровых данных, на фиг.2 временная диаграмма работы устройства в примере настройкц на выполнение функции кодопреобразования. 45

Устройство (фиг. 1) состоит из элементов И 1, элементов ИЛИ 2, триггеров 3, входных шин 4 устройства, шин 5-9 настройки устройства и шины

10 синхронизации устройства. Информационный вход каждого триггера 3 соединен с выходом соответствующего элемента ИЛИ 2, входы которого соедине ны с выходами элементов И 1 соответ:ствующей группы. Вход синхронизации каждого из триггеров 3 соединен с ши-, ной 10 синхронизации устройства. Первые входы элементов И 1 каждой группы соединены соответственно с выходами триггеров 3 и входными шинами 4 устройства. Второй вход каждого элемента И 1 соединен с соответствующей ему одной отдельной«шиной :5,б,7,8 или 9 настройки устройства. Шина 10 синхронизации устройства предназначена для обеспечения одновременной пе- 65 редачи сигналов на триггеры 3 через элементы И 1, ИЛИ 2.от прямых, инверс,ных выходов триггеров 3 и входных шин

4 устройства в зависимости от сигна.лов на шинах 5-9 настройки устройства.

В качестве сигналов на шинах 5-9 настройки устройства могут быть как сигналы постоянного значения (разрешающие — единицы, запрещающие — нули), так и сигналы переменного значения (двоичные последовательности). Сигналами на входных шинах 4 устройства могут быть сигналы постоянного или переменного значения как независимые (внешние Но отношению к данному устройству), так и зависимые (с выходов триггеров 3). Каждый следующий сигнал на шине 10 синхронизации устройства может быть подан после завершения переходного процесса в устройстве от предыдущего сигнала на этой шине, т.е. минимальный такт должен быть больше времени срабатывания и установления сигнала в последовательной цепи йз элементов И 1, ИЛИ 2, триггера

3. Изменение сигналов. на шинах 5-9 настройки устройства и изменение независимых сигналов на входных шинах

4 устройства, приводящие к изменению сигнала на информационных входах триггеров 3, должны осуществляться вне интервала времени активного действия сигнала на шине 10 синхронизации устройства, e.å. вне действующего фрон га импульса сигнала на шине 10 синхронизации устройства для триггеров

3 с динамическими входами сйнхронизации и вне разрешающего уровня сигнала на шине 10 синхронизацИИ устройства для триггеров 3 с потенциальными входами синхронизации. Выполнение этих условий необходимо для обеспечения однозначности в работе устройства.

Совокупность состояний триггеров

3 образует внутреннее состояние устройства ° Под действием очередного сигнала на шине 10 синхронизации устройства устройство переходит в очередное внутреннее состояние, при этом выходными сигналами устройства являются сигналы на одном или нескольких выходах триггеров 3. Сигналами на входных шинах 4 устройства и на шинах:5-9 настройки устройства настраивают устройство на выполнение конкретных функций логической обработки цифровых данных.

Более подробно рассмотрим работу устройства на примере его настройки на выполнение функции синхронного кодопреобразования входных двоичных данных в известный код модифицированной фазовой модуляции. Для этого нужно на шину 5 настройки устройства.подать сигнал логической 1, на шину 8 настройки устройства подать сигнал

978141 в ходных данных (фиг. 2б), на шины 7 и

9 настройки устройства и подать логически инвертированный сигнал входных данных (фиг.2в), на все другие шины настройки устройства подать сигналы логического О, на шину 10 син-. хронизации устройства подать сигналы удвоенной частоты, по сравнению с частотой сигналов входных данных (фиг.2а). Если в качестве триггеров 3 рименить триггеры с динамическим ходом синхронизации по фронту сигна ла и принять за логическую 1 сигнал. положительного напряжения, то на прямых выходах триггеров 3 будут сигналы, показанные на фиг. 2г, д, е (2г— для триггера.3 первого слева, 2е— для триггера 3 последнего слева) .

В начале каждого такта работы устройства (начало такта. соответствует переднему фронту сигнала на шине 10 синхронизации устройства, фиг. 2а, состояние первого слева триггера 3 изменяется на противоположное; второй слева триггер 3 устанавливается в единичное состояние, если в единичном состоянии первый слева триггер 3 и на шине 7 настройки устройства сигнал единицы, в противном случае второй слева триггер 3 устанавливается в нулевое состояние, последний слева триггер 3 (его прямой выход является в данном примере выходом устрой ства ) устанавливается в единичное состояние, если сигнал на шине 9 на.стройки устройства соответствует единичному при единичном состоянии второго слева триггера 3 или сигнал на вжне .8 настройки устройства соответствует единичному при единичном состоянии первого слева триггера 3, в других случаях последний слева триг- гер 3 устанавливается в нулевое состояние. Как показано на фиг. 2, входная последовательность данных 1010011 (соответствует при удвоенной частоте стробнрования последовательности 11 00. 11 00 00 11 11 ) преобразуется .в требуемую последовательность

01000100100101 при укаэанной настройке устройства.

При необхОдимости выполнения в устройстве логической обработки цифровых данных в соответствие другой функции, достаточно изменить сигналы на входных шинах 4 устройства и на шинах 5-9 настройки устройства.

Соединение первых входов элементов И 1 каждой группы с выходами триггеров 3 и входными шинами 4 устройства соответственно, а вторых вхо-. дов элементов И 1 — с шинами 5-9 настройки устройства упрощает предлагаемое устройство в общем случае эа

15 счет значительного сокращения числа элементов И 1 при незначительном увеличении или сохранении числа триггеров 3. Наличие шин 5-9 настройки устройства. обеспечивает многофункцио

20 нальность устройства.

Формула изобретения

Устройство для логической обработки цифровых данных, содержащее

25 элементы И, ИЛИ, триггеры, причем информационный вход каждого триггера ,соединен с выходом соответствующего элемента ИЛИ, входы которых соединены с выходами элементов И соответ30:ствующей группы, входы синхронизации триггеров соединены с шиной синхронизации устройства, о т л и ч а ющ е е с я тем, что, с целью упрощения, первые входы элементов И каждой группы соединены с выходами триггеров и входными шинами устройства сс ответственно, а вторые входы соединены с шинами настройки устройства.

Источники информации, 4(принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 500525, кл. 6 06 F 7/00, 1976.

2. Лазарев В.Г. и др. Синтез управляющих автоматов. 14. Энергия, 1978, с. 18-19

45 3. Автоматика и вычислительная техника, 1980, Р 4, с. 24, рис. 2 (прототип) .