Устройство для вычисления функций @ и @

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Савоз Советских

Социалистических

Республик

Iu>978146 (61) Дополнительное к авт. свид-ву(22) Заявлено 20.10.80 (21) 3221232/18-24 с присоединением заявки М (23) Приоритет Опубликовано 30.11Â2. Бюллетень Но 44

Дата опубликования описания 30. 11. 82

Р М К з

С 06 F 7/548

Государственный комитет

СССР яо делам изобретений и открытий (53) УДК 681. 325 (088.8) В.Ф.Евдокимов, Ю.А.Плющ, 10 ° 7.Êèçèì, В.В.Мохор и В.В.Литвиненко (72) Авторы изобретения (71) Заявитель

Институт электродинамики AH Украинской CCP (5 4 ) УСТРОЙСТВО ДЛЯ В61Ч11СЛЕ Н11Я ФУ Н КЦИ Й

51NX И COAX

Изобретение относится к вычислительной технике и может быть применено при построении специализированных вычислительных устройств.

Известно устройство, содержащее два умножителя, выходы которых соединены с входами сумматора, и два блока памяти (1 1.

Функции синуса и косинуса определяются на основе соотношений

51п(х+ах) = sinx - cos д х+дх cosx сов(х+ах) = cosx + а х sinx

Значения sinx u cosx должны быть записаны как коэффициенты в блоках памяти. При этом для х, представленного и разрядами, количество хранимых коэффициентов N определяется как

2н 1

Недостатком данного устройства является необходимость использования большого объема памяти.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее регистр аргумента, блоки памяти, два умножителя, сумматор и выходной регистр (2).

Недостатком известного устройства является повышенный объем памяти,, необходимой для хранения значений функций sinx.

Цель изобретения — сокращение объема используемой памяти.

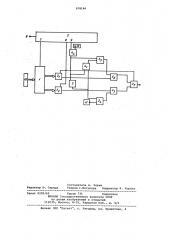

Поставленная цель достигается тем, что в устрой=тво длч вычисления функций з)пх и созх, содержащее первый и второй умножители, первый сумматор и блок памяти коэффициентов, первый и второй входы первого сумматора соединены с выходами соответственно первого и второго умножнтелей, содержит коммутатор, шифратор, четыре сумматора, блок возведения в квадрат, два регистра, третий и четвертый умножители, выход блока памяти коэффициентов соединен с информационным входом коммутатора, управляющий вход которого соединен с первым выходом шифратора, вход которого соеди- нен с входом аргумента устройства, первый и второй выходы коммутатора соединены с первыми входами соответственно второго и третьего сумматоров, вторые входы которых соединены с вторым выходом шифратора, третий выход которого соединен с первым входом третьего умножителя, второй вход которого соединен с выходом первого регистра, выход третьего ум

978146 ножителя соединен с первыми вхоцами четвертых сумматора и умножителя и через блок возведения в квадрат - с . вторым входом четвертого умножителя и первым входом пятого сумматора, второй вход которого соединен с выходом второго регистра, выход четвертого умножителя соединен с вторым входом четвертого сумматора, выходы второго и третьего сумматоров соединены c ïåðâûìè входами соответст- 10 венно первого и второго умножителей, вторые входы которых соединены с выходами соответственно четвертого и пятого сумматоров, выход первого сумматора соединен с вторыми входами второго и третьего сумматоров и выходом устройства.

На чертеже представлена блоксхема предлагаемого устройства. 20

Устройство для вычисления функций sinx u cosx содержит коммутатор

1, сумматоры 2 -2, блок 3 возведения в квадрат, умножители 4 - 44,шифратор 5, вход 6 шифратора, выходы 25

7-9 шифратора, блок 10 памяти коэффициентов, регистры 11 и 12.

Шифратор 5 содержит (и-5) преобразователей прямого кода в дополнительной, где п — разрядность представле 30 ния аргумента. Каждый последующий преобразователь, входящий в состав шифратора преобразует (К-1) разрядов предыдущего преобразователя, где К количество разрядов на выходе преды- 35 дущего преобразователя, причем К-й разряд является управляющим для последующего преобразователя. Если значение К-ro разряда О, то происходит преобразование кода в дополнительный,40 если 1, то выдается прямой код. Первым выходом шифратора является (п+1)-й разряд аргумента, определяющий режим вычисления (sinx или

cosx), второй выход шифратора — выхо-45 ды К-х разрядов преобразователей шиф. ратора, третий выход — выход (n-5)-ro преобразователя шифратора.

Устройство работает следующим образом.

Пусть необходимо вычислить sin угла 548. На вход б устройства посту. пает вдоичный код 110 110, соответствующий углу 54 . По сигналу шифратора, идущему с его выхода 7, комму- >5 татор посылает поступающие иэ блока

10 памяти константы A = 0,110000 и

A< = 0,001110 на сумматор 22, а константы A 2 = 0,011110 и A 3 =0,010111— на сумматор 2 . 60 .В .табл. приведены значения констант, подаваемых из памяти на коммутатор 1, при разрядности аргумента от 0 до 7. 64

Константы

Аъ

I ) I

0,11ОООО 0,011100 0,010111

Э 4 где А =sin 64 s i и 32

А =cos 64 sin 32

А =sin 64 cos 32

А4=cos 64 51п 32

Ъ о . ОУ

В общем случае константы выполняются сл еду ющи м о бр аз ом.

A(ïL „, 2 -" . А.(" где А; и А . — константы, определяе(п)Э (n) мые для и-разрядного представления аргумента.

В знаковые разряды сумматоров 2 и 2о поступают с шифратора 5 по выходу 8 значения "0" или "1", определяющие зчаки для констант А -А4,значение "0" определяет знак "+", "1" знак "-". Значения, определяющие знаки для констант, берутся с старшиХ разрядов, получающихся в шифраторе

5 кодовых комбинаций.

Используя знаки, в сумматоре 2 происходит сложение -0,0011104 и

+0,110000, в сумматоре 2 сложение

+0 011110 и +0,010111

Полученный в сумматоре 2 код

0,110101 поступает на первый вход умножителя 42, двоичный код 0,100010 иэ сумматора 2 о поступает на первый вход умножителя 4 .

В это же время на блок 3 и первый вход умножителя 4 с умножителя 4 поступает число й, равное 0,011111, которое получается путем умножения в умножителе 4+ постоянного числа

0,000001, поступающего с регистра 12 на значение с, поступающее с выхода

9 шифратора 5.

Таким образом, сС = 100000- сА5при x = О, о = о 5-100000 при х —— 1, где хк — значение старшего разряда.

На выходе блока 3 возведения в квадрат получаем двичный код 0,001111, который поступает на второй вход умножителя 4, на выходе которого получаем двоичный код 0,0001111, соответствующий кубу числа В.

Этот код, умноженный на постоянное для предлагаемого устройства число 0,000100 поступает на второй вход сумматора 2>, на первый вход которого поступает число 6, умноженное на постоянное для предлагаемого устройства число, равное 0,110010.

Полученный с выхода сумматора 2 двоичный код 0,010111 поступает на второй вход умножителя 4, где происходит умножение данного двоичного кода на двоичный код 0,110010, поступающий с сумматора 2 . В результа978146

Таким образом, путем введения дополнитЕльных блоков и связей в предлагаемое устройство получаем положительный эффект, позволяющий сократить 50 объем используемой памяти в сравнении с известным устройством. те умножения получается двичный код

0,010011, поступающий на первый вход сУмматора 2 .

Па второй вход сумматора поступает двоичный код 0,011110, полученный следующим образом. С выхода бло- 5 ка 3 квадрат числа, равный

0,001111 поступает с умножением на йОстоянное для устройства число

0,010010 на первый вход сумматора

2, на второй вход"которого поступа- щ0 ет число 0,111111, постоянное для ,предлагаемого устройства. Полученный в сумматоре 2 код 0,111011 умножается в умножителе 4 на поступивший с сумматора 2< код 0,001110, по .15 лученное в результате умножения число 0,011110 и будет подаваться на второй вход сумматора 2 5, в котором после присвоения шифратором 5 знаков соответствующим слагаемым произойдет сложение, и на выходе получится 1 значение 0,110001, соответствующее

sin двоичного числа 110110.

Работу устройства при вычислении

cos 54О рассмотрим также на примере.

При вычислении cos 54О по сигналу 25 шифратора 5, идущему с угравляющего выхода 7, коммуматор 1 посылает поступающие из блока 10 памяти константы A„ = 0,110000 и A4 = 0,001110 на сумматор 21,а констакты А < = 30

0,011110 и A З = 0,010111 на сумматор 2 . Шифратор 5 присваивает . по выходу 8 знаки для констант,поступающих на сумматоры 2„и 2 . В сумматоре 2 происходит сложение

А„ = 0,110000 и A = +0,001110, в

Сумматоре 2 2 сложение А —— +0,011110

И А 3 +О, 0 1 0 1 1 1 ° В дальнейшем идет процесс вычисления, аналогичный процессу вычисления синуса. При этом 40 шифратор 5 определяет знаки кодовых комбинаций, поступающих на сумматор

5 . Точность полученных результатов зависит от разрядности представления констант. 45 формула Hüîáðåòåíèÿ

Устройство для вычисления функций

sinx и cosx, содержащее первый и второй умножители, первый сумматор и бЛок памяти коэффициентов, первый и второй входы первого сумматора соединены с выходами соответственно первого и второго умножителей, о тл и ч а ю щ е е. с я тем, что, с целью сокращения объема используемой памяти, оно содержит коммутатор, шифратор, четыре сумматора, блок возведения в квадрат, два регистра,третий и четвертый умножители, выход блока памяти коэффициентов соединен с информационным входом коммутатора, управляющий вход, которого соединен с первым выходом шифратора, вход которого соединен с входом аргумента устройства, первый и второй выходы коммутатора соединены с первыми входами соответственно второго и третьего сумматоров, вторые входы которых соединены с вторым выходом шифратора, третий выход которого соединен с первым входом третьего умножителя,второй вход которого соединен с выходом первого регистра, выход третьего умножителя соединен с первыми входами четвертых сумматора и умножителя и через блок возведения в квадрат с вторым входом четвертого умножителя и первым входом пятого сумматора, второй вход которого соединен с выходом второго регистра, выход четвертого умножителя соединен с вторым входом четвертого сумматора, выходы второго и третьего сумматоров соединены с первыми входами соответственно первого и второго умножителей, вторые входы которых соединены с выходами соответственно четвертого и пятого сумматоров, выход первого сумматора соединен с вторыми входами второго и третьего сумматоров и выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Оранский A.N. Аппаратные методы в цифровой вычислительной технике ° Минск, 1977, с. 49-50.

2. Авторское свидетельство СССР

М 622090, кл. Г> 06 Г 7/548, 1977 (прототип1.

978146

Составитель A. Зорин

Редактор 10. Середа Техред С.Мигунова Корректор H Король, Заказ 9220/65 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул; Проектная, 4