Запоминающий элемент

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик а

//

=ф-.

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

G 11 С 11/40 с присоединением заявки ¹â€” (23) Приоритет—

Государственный комитет

СССР но делам изобретений и открытий (53«УДК 681.327. . 66 (088. 8) Опубликовано 30,11.82, Бюллетень М9 44

Дата опубликования описания 30.11. 82

Л.Г. Журавин, М.A. Мариненко, Е.И. Семенов-"---, н В,А, Трошкин (72) Авторы изобретения

jf

Ленинградский ордена Ленина электротехнический г институт им. В.И. Ульянова(Ленияа) (71) Заявитель (54) ЗР,ПОМИНМОЩИИ ЭЛЕМЕНТ базы транзисторов соединены соответственно с первыми выводами первого и второго делителей напряжения, введе5 ны первый и второй ключевые р-n-ртранзисторы, эмиттеры которых объединены и соединенй с шиной питания, коллекторы первого ключевого р-и-ртранзистора и первого ключевого и-р p n-транзистора объединены и соединены с выходом второго делителя напряжения, коллектора второго ключевого р-и р-транзистора и второго ключевого n — p-n-транзистора объединены и соединены с выходом первого делителя напряжения, базы первого и второго ключевых р-п-р-транзисторов соединены соответственно с вторыми выводами первого и второго делителей напряже ния.

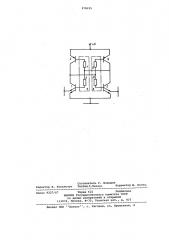

На чертеже представлена схема запоминающего элемента.

Элемент содержит и-р-п-транзисторы 1 и 2„ первые эмиттеры которых соединены со словарной шиной Ше„, вторые эмиттеры - с соответствующей разрядной шиной считывания Ш „ и записи Ш э, а коллекторы соединены с соответствующими коллекторами pln-p»Tðàíçèñòîðoâ 3 и 4, эмиттеры которых объединены и соединены с шиИзобретение относится к микроэлектронике и может быть применено при разработке микросхем памяти.

Известен запоминающий элемент, содержащий два р-и-р транзистора, два п-р-п-транзистора, два диода, и позволяющий считывать, записывать и хранить один бит информации (1).

Недостатком укаэанного элемента является сложность технологии его изготовления, поскольку он выполнен по технологии И Л.

Наиболее близким к предлагаемОму является запоминающий элемент, содержащий два двухэмиттерных транзистора п-р-и типа и два делителя напряжения. Элемент позволяет хранить один бит информации (2).

Недостатком этого элемента являетcR низкая помехоустойчивость из-за малой разницы коллекторных напряжений.

Цель изобретения — повышение помехоустойчивости элемента.

Указанная цель достигается тем, что в запоминающий элемент, содержащий первый и второй ключевые п-р-итранзисторы, первые эмиттеры которых объединены и соединены со словарной шиной, вторые эмиттеры соединены с соответствующими разрядными шинами, (61) Дополнительное к авт. саид-ву— (22) Заявлено 25. 02. 81 (21) 3250572/18-24 ($1 «М. Кд.з

978195 ной питания. Базы первого n-p-n u первого р-и-р-транзисторов соединены с соответствующими выводами первого делителя 5 напряжения, выход которого соединен с коллектором второго 2 и и-р-и транзистора. Базы второго 5 и-р-и и второго р-п-р транзисторов соединены с соответствующими вывода ми второго делителя б напряжения,выход которого соединен с коллектором

1 первогЬ п-р-п-транзистора. 10 ,Целители 5 и б напряжения могут быть выполнены на резисторах 7-10.

Устройство работает следующим образом.

В установившемся состоянии на ши- 15 не Ш „ имеется низкий потенциал И (близкий к нулю), а на разрядные шины B3I,, и Шр э, поДано более высокое напряжение И > И„.

В этом состояйии устройство представляет собой статический триггер.

На коллекторе одного из транзисторов, например, транзистора 2 потенциал близок к напряжению источника питания, так как транзистор 4 открыт, а на коллекторе транзистора 1 имеется близкое к нулю напряжение, так как в базу транзистора 1 втекает ток через резистор 8 и открытый транзистор

4; в свою очередь, базовый ток транзистора 4 течет через резистор 9 за счет открытого транзистора 1.

При считывании информации потенциал Ш возрастает до величины

И g > И > И, Устроиство IIpH BTGM работает так же, как и прототип: если до подачи импульса опроса в Шс„через транзистор 1 протекает ток, что соответствует хранению нуля, то через первый эмиттер транзистора l в словарную шину протекае1 ток, равный 40 сумме токов через резисторы 8 и 9.

Когда же напряжение на шине Ш „ возрастает до величины И >,то этот ток отводится через второй эмиттер в шину IIII>. ц, где обнаруживается включен- 45 ным в нее усилителем считывания. Когда импульс опроса на шине Ш заканчивается, то снова ток течет через первый эмиттер транзистора 1. Если запоминающий элемент находится в состоянии 1 (ток через транзистор

1 равен нулю), то при опросе в шине

Шр.сч.ток не появляется.

При записи информации процессы, происходящие в запоминающем элементе, следующие. Шина слов снова возбуждается импульсом с амплитудой И,а на разрядной, шине Шр.3.Ôoðìèðóåòñÿ импульс с амплитудой ИЗ(запись 0 ) или с амплитудой И„ (йонижение потенциала шины Ш при записи 1 ) .

В первом случае происходит запирание транзистора 2, а во втором— транзистор 2 открывается, причем новое состояние транзистора 2 сохраняется и после окончания импульсов в словарной и разрядной Ш шинах.

В результате более полного использования напряжения источника питания в предлагаемом устройстве обеспечивается высокая устойчивость к помехам, действующим на словарной и разрядных шинах.

Формула изобретения

Запоминающий элемент, содержащий первый и второй ключевые и-р-и-транзисторы, первые эмиттеры которых объединены и соединены со словарной шиной, вторые эмиттеры соединены с соответствующими разрядными шинами, бази транзисторов соединены соответственНо с первыми выводами первого и второго делителей напряжения, о т л и ч а ю шийся тем, что, с целью повышения помехоустойчивости элемента, он содержит первый и второй ключевые р-п-р-транзисторы, эмиттеры которых объединены и соединены с шиной питания, коллекторы первого ключевого р-и-р-транзистора и первого ключевого р-.n-p-транзистора. объединены и соединены с выходом второго делителя напряжения, коллекторы второго ключевого р-и-р-транзистора и

BTop0ro .ключевого и-р-п-транзистора объединены и соединены-с выходом первого делителя напряжения, базы первого и второго ключевых р-и-ртранзисторов соединены соответственно с вторыми выводами первого и второго делителей напряжения.

Источники информации, принятые во внимание при экспертизе

1. Патент США Р 3909807, кл. 340-173, опублик. 1975.

2. Огнев N.Â., Шамаев Ю.Н. Проектирование запоминающих устройств,,М., Высшая школа „ 1979, с. 37, рис. 2.11б (прототип).

978195

Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Закаэ 9227/67

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Составитель Г. Бородин

Редактор И.. Ковальчук ТехредЛ.Пекарь Корректор М. Коста,