Элемент памяти

Иллюстрации

Показать всеРеферат

О. А."Варанов

В. В. Баринов, Д. Е. Ковалдин, М. А. Корол,ев, и В. И. Шевяков (72) Авторы изобретения (71) Заявитель

Московский институт электронной техники

: (S 4) ЭЛЕМЕНТ ПАМЯТИ

Изобретение относится к цифровой вы- числительной технике и .может быть иск, пользовано в полупроводниковых запоминаюших устройстюх большой информаци онной емкости.

Известен элемент памяти, содеркаший

5 первый и второй и -p- и транзисторы, эмиттеры которых соединены с обшей шиной, а коллекторы соединены с катодами соответственно первого и второго диодов

Шоттки, аноды которых соединены через диоды с управляюшими шинами и шиной питания (1) .

Недостаткам этого элемента памяти является относительно низкая помехоустойчивость.

Известен также элемент памяти, содержаший первый и второй и-р-и транзисторы, первый и второй р- и-р транзисторы и четыре диода Шоттки, первая и 20 вторая шины управления элемента памяти соединены с аноами соответственно - первого и второго диодов Шоттки, катоды которых соединены с анодами соответст2 венно третьего и четвертого диодов Шоттки, катоды которых соединены с коллекторами соответственно первего и второго и-р- и. транзисторов, базы которых соединены с коллекторами соответственно первого и второго р-и-р транзисторов, базы которых соединены с шиной смешения, а эмиттеры и- р- и транзисторов соединены с обшей шиной tZ) .

Недостатком известного элемента памяти является относительно низкая достоверность функционирования.

1.1ель изобретения - повышение достоверности функционирования.

Поставленная цель достигается тем, что в элементе памяти, содержашем первый и второй и-р-и транзисторы, первый и второй р- и- р транзисторы и четыре диода Шоттки, первая и вторая шина управления элемента памяти соединены с анодами соответственно первого и вто рого диодов Шоттки, катоды которых соединены с анодами третьего и четвертого диодов Шоттки, катоды кото;.» х соединены

Р P

Я Й 1 3 где ерш

Ы, al„3 9783 с коллекторами первого и второго й-р-и транзисторов, базы которых соединены с коллекторами соответственно первого и и второго р-и-р транзисторов, базы которых соединены с шиной смешения, а эмиттеры A- p-и транзисторов соединены с обшей шиной, базы первого и второго и-р«п транзисторов соединены с катодами соответственно первого и второго диодов

Шоттки, а эмиттеры первого и второго 1ф р- и- р транзисторов соединены соответственно с второй и первой шинами управления.

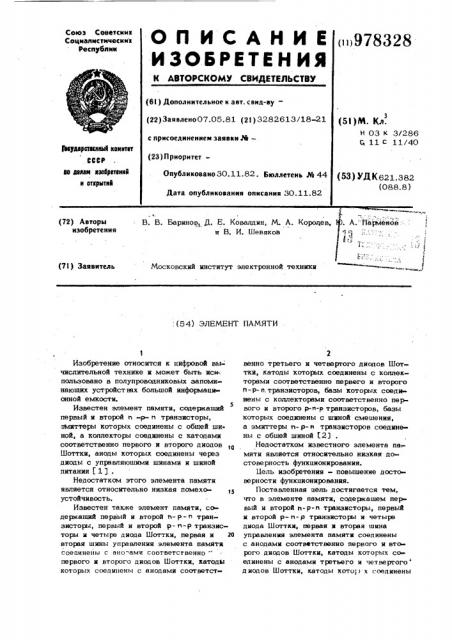

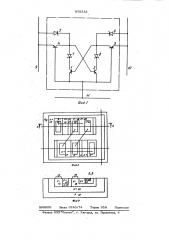

На фиг. 1 показана структурная схема элемента памяти; на фиг. 2 — тополо- )g гия элемента памяти при его реализации в виде интегральной схемы; на фиг. 3разрез А-А на фиг. 2.

Элемент памяти содержит первый 1 и второй 2 п-р- и транзисторы, первый 3 2О и второй 4 р-и-р транзисторы и четыре диода Шоттки 5 — 8, первая 9 и вторая

10 шины управления элемента памяти соединены с анодами соответственно пер- вого 5 и второго 6 диодов Шоттки, ка- 23 тоды которых соединены с анодами соответственно третьего 7 и четвертого 8 диодов Шоттки, катоды которых соединены с коллекторами соответственно первого

1 и второго 2 и- Р- п транзисторов, базы 3Q которых соединены с коллекторами соответственно первого 3 и второго 4 р-и- р транзисторов, базы которых соединены с шиной 1 1 смещения, а эмиттеры и - р- и транзисторов соединены с обшей шиной, которая соединена с шиной смешения, баэ зы первого 1 и второго 2 и-p-h транзисторов соединены с катодами соответственно первого 5 и второго 6 диодов

Шоттхи, а эмиттеры первого 3 и второго

4р- и-р транзисторов соединены соответственно с первой 9 и второй 10 шинами управления.

Выполнение шины 11 смешения в виде единого соединения с обшей шиной удобно при реализации в виде интегральной схемы, в этом случае элемент работает при нулевом смешенйи.

Элемент памяти работает следующим образом.

В режиме считывания информации равные токи считывания 1 втекают иэ шин

9 и 10 в элемент памяти. Предположим, что элемент памяти находится в состоянии, когда транзистор 3 насыщен и коллекторным тохом насыщает транзистор 1. ТОР» да транзистор 2 работает в нормальноФм активном режиме, но ток через него практически не проходит,так как напряжение

28 4 на р-и-переходе эмиттер-база этого транзистора меньше граничного напряжении отпирания р- и-перехода эмиттер-база Ч - г

3О. ГР.

Транзистор 4 также работает в нормальном активном режиме. Диод 7 открыт, а диод 8 закрыт. Ток через диод 6 практически отсутствует, так как напряжение на диоде равно напряжению между коллектором и эмиттером насыщенного транзистора 3 и меньше граничного напряжения отпирания диода Шоттки V*ù . Таким образом, практически весь ток считывания lф из шины 10 протекает через наI

° / сышенныя транзистор 3, а ток считывания

1 из шины 9 распределяется между транзистором 4, работающим в нормальном активном режиме, и открытым диодом 5.

Полезный сигнал считывания (разность потенциалов на шинах) вознихает за счет разности токов эмиттеров диодов р -и-р транзисторов и равен полезный сигнал считывания (разность потенциалов на шинах 9 и 10) темпе ратурный потенциал; нормальный коэффициент усиления.по току и-р-и транзисторов в схеме включения с обшей базой; нормальный и инверсный коэффициент усиления по току

p->-p транзисторов в схеме включения с обшей базой; ток считывания, втекаюший из шины 9 или 10 в элемент памяти;

3 — часть тока считывания 3.о, про. текающая через открытый диод 5.

Из приведенного выше выражения следует, что полезный сигнал считывания тем. больше, чем большая часть тока считывания 3 протекает через открытый диод 5. Соответственно, если весь ток разрядной шины протекает через транзистоо 4, работающий в нормальном активном режиме, то полезный сигнал считывания минимален. >

Введение шунтируюших диодов 5 и 6 позволяет увеличить полезный сигнал считывания в 5-8 раз. Диоды 7 и 8 введены для уменьшения логической разности потенциалов в триггерных узлах элемента памяти, что позволяет обеспечить высокое

Формула изобретения

5 9783 быстродействие элемента памяти. Кроме того, диоды 7 и 8 служат для согласования логических уровней в разлгтных элементах памяти при объединении их в накопителе. Сумма падений напряжения на открытых диодах Шоттки 5 и 7 должна быть примерно равна падению напряжения на открытом р-h-переходе эмитте1 база ,p- n-р транзистора.

Режим хранения информации аналогичен режиму считывания, с тем лишь отличием, что токи хранения, втекаюшие из шин 9 и 10 в элемент памяти, обычно на 2-3 порядка меньше токов считывания.

В режиме записи информации через IS одну из шин (например шину 9) в элемент памяти втекает ток записи, равный току считывания, ток в друг. и разрядной шине (в данном случае в шине 10) отключается

20 или существенно уменьшается. При этом транзистор 4 насыщается и коллекторным током переводит транзистор 2 иэ нормального активного режима в режим насыщения

Транзисторы 1 и 3 выходят иэ режима

25 насыщения и переходят в нормальный активный режим. Диоды 5 и 7 перестают проводить ток, а диоды 6 и 8 открываются.

На фиг. 2 показаны поперечное сечение интегральной структуры и эскиз топо30 логии инжекционного элемента памяти.

Область р 12 является подложкой, й+ область 13 является эмиттерами и — р — h транзисторов 1 и 2, р -область 14 явля. ется анодом диода Шоттки 5, металл 15 является катодом диода Шоттки 5, р+ область 16 является эмиттером р-п-р транзистора 4, и -область 17 является базой

Р-n-p тTрpаeнHзeиMсcтTоoр а 44, р -область 18 является анодом диода Шоттки 7, металл .19 является катодом диода Шоттки 7, р+область 20 является одновременно коллектором р-и-р транзистора 4 и базой

n-p-n транзистора 2, n oáëàcòü 21 является коллектором и --р-и транзистора 2.

Использование диодов Шоттки, шунтируюших р»п- р транзисторы, и согласующих диодов Шоттки, позволяет увеличить, полезный сигнал считывания информации и повысить помехозащищенность и быстро-Ю

28 6 действие элемента памяти. 11ричем полезный сигнал считывания и помехозащищен- . ность возрастают в 5-8 раз, а быстродействие в 1,2-2 раза, в результате чего возрастает достоверность функционирования элемента памяти.

Элемент памяти, conepêàøèé первый и второй rl -p- h транзисторы, первый и второй р-п-р,транзисторы и четыре диода Шоттки, первая и вторая шина управления элемента памяти соединены с анодами соответственно первого и второго диодов Шоттки, катоды которых соединены с анодами третьего и четвертого диодов Шоттки, катоды которых соединены с коллекторами первого и второго и-р-в транзисторов, базы которых соединены с коллекторами первого и второго транзисторов, базы которых соединены с шиной смешения, а эмиттеры n-p-u транзисторов соединены с обшей шиной, о т л и ч а ю ш и и с я тем, что, с целью повышении достоверности функционирования, базы первого и второго п-Р-h транзисторов соединены с катодами соответственно первого и второго диодов

Шоттки, а эмиттеры первого и второго

p n-ртранзисторов соединены соответственно с второй и первой шинами управления.

Источники информации, принятые во aHKMaHRe nDM экспертизе

1. Патент США М 3849675, кл. 307-292, Н 03 3/286, 1975.

2. Заявка ФРГ М 2556833, кл. G 11 t 11/40, 1980 (прототип).

Примечание: прототип изменен в связи с выявлением технического решения, более близкого к предложенному по совокупности конструктивных при-знаков.