Формирователь импульсов

Иллюстрации

Показать всеРеферат

iii978334

Союз Соаетскин

Социапис тически н

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свид-ву (5l ) M. Кл. (22) Заявлено 03.04.81 (21)3300732/18-21 с присоединением заявки J%

H 03 К 5/00

3Ъеудврстмна и намнтет ссср (23} Приоритет во делам нзайретеннй н оирмтнй

Опубликовано 30.11.82. Бюллетень № 44

Дата опубликования описания30.11.82 (53) УДК621.374 (088.8 ) Б. И. Дьяков, О. А. Дымова, А, Н, Ершов и E. И. Капустенко (72) Авторы изобретения

1 ю (7l) Заявитель (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к автоматике и вычислительной технике и предназначе но для управления работой логических схем.

Известно устройство формирования им5 пульсов, содержащее генератор опорных импульсов, стробирующие схемы, мультивибратор, схему сброса (1 ), Недостатком указанного устройства является малый диапазон изменения частоты и длительности выходных импульсов, обусловленный сложностью изменения частоты и скважности мультивибратора в больших пределах.

Наиболее близким к предлагаемому по 1 технической сущности является формирователь импульсов, содержащий генератор опорной частоты, подключенный к входу делителя частоты и к первому входу блока стробирования, выход которого соеди- 2о нен с входом счетчика импульсов, триггер и элемент ИЛИ, выход которого через триггер подключен к второму входу блока стробирования и к установочному входу счет шка импульсов, выход которого соединен с первым .входом элемента

ИЛИ, второй вход элемента,ИЛИ подключен к выходу делителя частоты (2), Недостатком известного формирователя импульсов является высокая вероятность преждевременной выдачи выходных импульсов. Это связано с наличием в схеме формирователя импульсов однократного отказа, приводящего к преждевременному появлению импульсов на выходе формирователя. Таким образом является неисправность блока стробирования, приводящая к несанкционированному прохождению импульсов с выхода генератора опорной частоты на вход счетчика импульсов, При этом преждевременно начинает функционировать счетчик. Бель изобретения - повышение надежности работы формирователя импульсов.

Поставленная цель достигается тем, что в формирователь импульсов, содержа- ° щий генератор опорной частоты, подклю3 9783 ченный к входу делителя частоты, блок

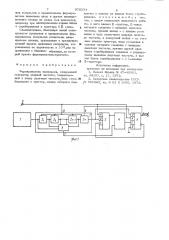

1 стробирования и триггер, выход которого подключен к одному из входов блока стробирования, введен D -триггер, D- вход которого соединен с выходом делителя частоты, прямой выход — с входом установки в нуль оконечного разряда делителя частоты, а инверсный выход — со счет ным входом триггера, вход установки в единицу которого соединен с выходом де" 10 лителя частоты, причем другой вход блока стробирования соединен с управляющим выходом делителя частоты, а выход блока с тро би ров а ни я — с С-входом D -триггера, На фиг. 1 представлена структурная электрическая схема формирователя импульсов; на фиг. 2 — временные диаграммы, поясняющие его работу.

Формирователь импульсов содержит 20 генератор 1 опорной частоты, подключенный к входу делителя 2 частоты, состоящего из последовательно соединенных разрядов 2-1...„2- и деления, где и = 1, 2, 3, ..., а также триггер 3, блок 25

4 стробирования и 2 -триггер 5. Выход генератора 1 опорной частоты, а также выходы каждого из разрядов 2, ..., 2„ .1 деления через коммутатор 6 могут быть подключены к управляющему выходу 7 де- 30 лителя 2 частоты. Выход делителя 2 частоты соединен со входом установки в единицу (-входом) триггера 3, и с информационным Q -входом триггера 5 2 -типа, Прямой выход триггера 3. соединен с одним из входов блока 4 стробирования, причем другой вход блока 4 стробирования соединен с управляющим выходом 7 делителя 2 частоты. Выход блока 4 стробирования соединен с тактовым входом gp (С-входом) D -триггера 5. Прямой выход 2 -триггера 5 является выходом формирователя импульсов и соединен со входом 8 установки в нуль оконечного разряда 2- и делителя 2 частоты, Инверсный выход I)-триггера 5 соединен со счетным входом триггера 3. Формирователь импульсов содержит шину 9 установки в исходное состояние, соединенную с входом 10 установки в исходное состояние разрядов 2-1, ..., 2- р деления делителя 2 частоты с входами установки в нуль триггера 3 и D --триггера 5, Формирователь импульсов работает следующим образом.

На формирователь импульсов подается напряжение питания, после чего по шине

9 подается сигнал (фиг, 2б) установки в исходное состояние, поступающий на вход 10 установки в исходное состояние разрядов 2, ..., 2„ деления делителя 2 частоты и на входы установки в нуль триггера 3 и D -триггера 5.

Установка в исходное состояние делителя 2 частоты, триггера 3 и D --триггера 5 необходима для устранения преждевременной выдачи выходных импульсов в момент подачи на формирователь напряжения питания, После подачи на устройство напряжения питания начинает работать генератор 1 опорной частоты и импульсы с его выхода (фиг. 2а) поступают на вход делителя 2 частоты. Делитель 2 частоты начинает функционировать. Положение коммутатора 6 выбирается в соответствии с требуемой длительностью формируемых импульсов, По мере заполнения разрядов

21 ..., 2„деления на управляющий выход 7 делителя 2 частоты начинают поступать импульсы (фиг. 2в) с заданным периодом следования. Импульсы с управляющего выхода 7 делителя 2 частоты (фиг, 2в) поступают на один из входов блока 4 стробирования, Поскольку на другом входе блока 4 стробирования присутствует потенциал логического нуля, соответствующий исходному состоянию

t триггера 3 (фиг, 2и), импульсы с управляющего выхода 7 делителя 2 частоты (фиг. 2в) не проходят на выход блока 4 стробирования, На фиг. 2r приведены импульсы на выходе разряда 2>1 делителя 2 частоты.

Положительный перепад напряжения с выхода разряда 2„ (фиг. 2г) поступает на вход оконечного разряда 2 д делителя 2 частоты и устанавливает его в состояние логической единицы (фиг. 2д), Положительный перепад напряжения с выхода делителя 2 частоты (фиг. 2n) воздействует на информационный вход(Э-вход)

3-триггера 5 и на вход установки в еди-. ницу триггера 3, вызывая его срабатывание. На выходе триггера 3 устанавливается потенциал логической единицы (фиг. 2и), которым отпирается блок 4 стробирования, При этом импульсы с управляющего выхода 7 делителя 2 частоты начинают поступать на С-вход 33 —триггера 5 (фиг, 2е). Поскольку на информационном входе триггера D -типа 5 в этот момент присутствует потенциал логической единицы с выхода делителя 2 частоты, то первый же положительный фронт импульса с выхода блока 4 стробирования (фиг. 2е) устанавливает D -триггер 5 в состояние логической единицы.

Несанкционированные импульсы с у«равляюшего выхода 7 делителя 2 частоты поступают на С-вход 9 -триггера 5.

Однако до тех пор, пока делитель 2 частоты не заполнится, на его выходе, а следовательно, и на информационном входе D -триггера 5 присутствует потенциал логического нуля. При этом импульсы, поступаюшие на С-вход Х) -триггера 5, подтверждают нулевое состояние на его прямом выходе. В момент заполнения делителя 2 частоты на его выходе, а значит, и на информационном входе D— триггера 5, появляется потенциал логической единицы, Передний фронт первого импульса, поступившего на С-вход D триггера 5 после появления потенц«ало логической еди«ицы «а его и«форма««о«ном входе, устанавливает D -rpIIIIep 5 в состояние логической ед«н«цы. При этом на прямом выходе 33 -тр«ггера 5 формируется передний фронт выходного импульса. Потенциал логической еди«ицы с прямого выхода D -триггера 5 поступает на вход 8 установки в нуль оконечного разряда 2 делителя 2 частоты, обеспечивая сброс данного разряда в состояние логического нуля. Поскольку на информационном входе D -триггера 5 «оявляется потенциал логического нуля, передний фронт следуюшего импульса, «оступаюшего íà его С-вход, обеспеч«воет установку D -триггера 5 в состояние логического нуля. При этом на прямол выходе 9 -триггера 5 формируется задний фронт выходного импульса. Поступление следуюших импульсов с управляюшего выхода 7 делителя 2 частоты «а Г-вход

2-триггера 5 не меняет его состояния, поскольку на его информацио«ном входе присутствует потенциал логического нуля.

Через период процесс формирования выходного импульса повторяется. Таким о5разом, в предлагаемом устройстве форм«рование выходного импульса происходит только при поступлении на информационный D -вход триггера 5 импульса с выхода делителя 2 частоты. Поэтому при отказе блока 4 стробирования и поступлении несанкционированных импульсов на

С-вход D -триггера 5 период повторения выходных импульсов остается равным периоду заполнения делителя 2 частоты.

Следовательно, при отказе блока 4 стробирования в предлагаемом формирователе импульсов преждевременной выдачи выходных импульсов не происходит и сохраняется нормальная работоспособность схемы. Преждевременная выдача выход5 978334 б

При этом на прямом выходе -триггера

5, а значит, и на выходе формирователя импульсов, формируется передний фронт выходного импульса (фиг. 2ж). Потенциал логической единицы с прямого выхода

0-триггера 5 (фиг. 2ж) поступает на вход 8 установки в нуль оконечного разряда 2 .делителя 2 частоты, обеспечивая сброс данного разряда в состояние логического нуля. 10

При этом на выходе делителя 2 частоты, информационном входе D -триггера 5 и входе установки в единицу триггера 3 устанавливается потенциал логического нуля (фиг. 2д). 15

После окончания импульса с выхода делителя (фиг. 2д) триггер 3 остается в состоянии логической единицы обеспе- чивая прохождение импульсов с управля- юшего выхода 7 делителя 2 частоты на 20

С-вход триггера D-типа 5, Поскольку на информационном входе D --триггера 5 в этот момент присутствует потенциал логического нуля, положительный фронт следуюшего импульса, поступающего на 25 его С-вход (фиг. 2е), устанавливает Qтриггер 5 в состояние логического нуля (фиг, 2хс).

На прямом выходе D-триггера 5, а значит, и на выходе формирователя им- ур пульсов, в этот момент формируется задний фронт выходного импульса (фиг. 2ж), На инверсном выходе 2 -триггера 5 в это т момент формируе тся положи тельный перепад напряжения (фиг. 2з), который воздействует на счетный вход триггера

3 и устанавпивает его в состояние логического нуля (фиг. 2и). Потенциал ло гического нуля (фиг. 2и) с выхода триггера 3 поступает на вход блока 4 стробирования и прекрашает прохождение имо пульсов с управляющего выхода 7 делителя 2 частоты на С-вход В -триггера 5 (фиг. 2e). На этом процесс формирования выходного импульса заканчивается. Че-4 рез период, определяемый частотой генератора 1 опорной частоты и коэффициентом деления делителя 2 частоты, процесс формирования выходного импульса повторяется. Частота, длительность, а, следовательно, и скважность выходных импульсов, могут меняться в широких пределах путем изменения коэффициента делителя

2 частоты и периода следования импульсов, поступаюших на управляюший выход

7 делителя 2 частоты.

В случае отказа блока стробирования формирователь импульсов работает сле дуюшим образом.

7 9783 ных импульсов в предлагаемом формирователе возможна лишь в случае одновременного отказа не менее 2-х элементов, например при одновременном отказе блока

4 стробирования и триггера 5 2 -тица.

Следовательно, благодаря новой совокупности признаков в предлагаемом формирователе импульсов исключены однократные отказы, приводящие к преждевременной выдаче выходных импульсов, что 10 уменьшило ее вероятность в 10 раз по

Ъ сРавнению с базовым образццм, за кото- . рый принят формирователь-прототип. ,15

Формула изобретения

Формирователь импульсов, содержащий генератор опорной частоты, подключенный к входу делителя частоты блок стро- 20

J бирования и триггер, выход которого под34 8 ключен к одному из входов блока стробирования, о т л и ч а ю ш и и с я тем, что, с целью повышения надежности работы, в него введен D -триггер, D -вход которого соединен с выходом делителя частоты, прямой выход — с входом установки в нуль оконечного разряда делителя частоты, а инверсный выход — co счетным входом триггера, вход установки в единицу которого соединен с выходом делителя частоты, причем другой ахоп блока стробирования соединен с управляюшим выходом делителя частоты, а выход блока стробирования — с С-входом

D -триггера.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии % 47-40501, кл. 98(5), с. 11, 1972, 2. Авторское свидетельство СССР М 552685, кл. Н 03 К 5/00, 1975.

978334

Составитель Л. Колосков

Редактор А. Власенко Техред ИГайду Корректор.В. Прохненко

Заказ 9240/74 Тираж 959 Подписное

ВНИИПИ Государтсвенного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная 4