Четырехквадрантный умножитель сигналов постоянного тока

Иллюстрации

Показать всеРеферат

О. Б. Милюков, Л. В. Лизина, А. В. Тюрев и A.. H. Шаров/

/.

t (72) Авторы изобретения

I .(7I ) Заявитель, (54) ЧЕТЫРЕХКВАДРАНТНЫЙ УМНОЖИТЕЛЬ

СИГНАЛОВ ПОСТОЯННОГО ТОКА

Изобретение относится к аналоговой вычислительной технике и может быть ис:пользовано при построении аналоговых и гибридных вычислительных устройств.

Известны четырехквадрантные умноха тели сигналов постоянного тока, исполь5 эуюшие промежуточное логарифмирование и содержащие стандартные блоки умножения (типа 525 ПС1), масштабные резисторы, ключи (1) .

Эти умножители отличаются высоким быстродействием, но низкой точностью.

Более высокую точность обеспечивают время-импульсные устройства перемножения.

Наиболее близким техническим решением к предлагаемому является четырехквадрантный умножитель, содержащий интегратор, инвертор, первый, второй и третий масштабные резисторы, соединенные между собой одним из выводов, компаратор, ключ, управляющий вход которого соединен с выходом компаратора, а информационный вход - с выходом инверто2 ра и вторым выводом третьего масштабного резистора, второй вывод первого масштабного резистора соединен с входом инвертора и является первым входом умножителя, второй вывод второго масштабного резистора соединен с выходом интегратора и является выходом умножителя, а первый и, второй выходы иомпаратора являются вторым и третьим входами умножителя. Умножитель позволяет по-. лучить высокую точность перемножения . сигналов постоянного тока 1 2 . .Однако он имеет малое быстродействие при необходимости получения низкого уровня пульсаций выходного напряжении, что является большим недостатком при построении быстродействующих вычислитель ных устройств.

Цель изобретения - повышение быстродейс твия.

Поставленная цель достигается тем, что в известный четырехквадрантный умно» житель сигналов постоянного тока, содержащий инвертор, вход которого является.3 980 1 первым информационным входом умножителя, первый ключ, информапионный вход которого подключен к выходу инвертора, компаратор, входы которого являются соответственно вторым информационным и тактовым входами умножителя, а выход подключен к управляющему входу первого ключа, интегратор, выход которого является входом умнэжителя и три масштабных резистора; первые выводы которых 1О объединены, второй вывод первого масштаб. ного резистора подключен к входу инвертора, второй вывод второго масштабного резистора подключен к выходу интегратора, а второй вывод третьего масштабного резистора подключен к выходу первого ключа, введены последовательно соединенные формирователь импульсов и триггер управления, четвертый и пятый масштабные резисторы, второй, третий, четвертый и пятый ключи и запбминающий конденсатор, вход формирователя импульсов подключен ко второму входу компаратора, первый выход триггера управления подключен к управляющим входам второго и пятого ключей, а второй выход триггера управления подключен к управляющим входам третьего и четвертого ключей, информационные входы второго и четвертого ключей объединены и подключены к первому выводу третьего масштабного резистора, выход второго ключа и Информационный вход третьего ключа объединены и через запоминающий конденсатор подключены к шине нулевого потенциала, первый вывод

ЗЯ четвертого масштабного резистора подключен к вьц оду третьего ключа, а первый вывод пятого масштабного резистора подключен к информационному входу пятого ключа, вторые выводы четвертого и пятого масштабных резисторов объединены и подключены к входу интегратора, выходы четвертого и пятого ключей подключены к шине нулевого потенциала.

4Я

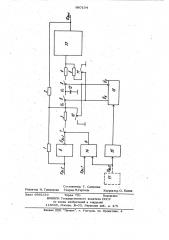

На чертеже приведена функциональная схема четырехквадрантного умножителя сигналов постоянного тока.

Четырехквадрантный умножитель содержит масштабные резисторы 1 — 5, инвертор 6, ключи 7 — 11, запомианющий кон.денсатор 12, интегратор 13, компаратор

14, формирователь 15 импульсов,, триггер 16 управления, генератор треугольных импульсов.

ЯЯ

Четырехквадрантный умножитель сигналов постоянного тока работает следующим образом.

04: 4

На третий вход умножителя от генера» тора 17 импульсов подаются импульсы, например треугольные. Следовательно, на выходе компаратора 14 формируются прямоугольные импульсы, относительная длительность кбторых пропорциональна сигналу постоянного тока ЦМ „, т. е. 6 =

=К ОйХ + 0,5, причем коэффициент К вы4 бирается таким, чтобы 0 Q 1. Частота прямоугольных импульсов на выходе триггера 16 управления, подаваемых на уп- равляющие входы ключей 8 - 11, вдвое ниже частоты импульсов, поступающих от генератора 17., Длительность замкнуто- го состояния ключа 7 задается величиной & .

Рассмотрим процессы в установившемся режиме. Предположим, что в первом такте работы ключи 8 и 11 замкнуты, ключи 9 и 10 разомкнуты, а напряжение в начале такта на запоминающем конденсаторе 12 равно нулю. До размыкания ключа 7, которое происходит внутри такта, напряжение О на конденсаторе 12 изменяется под действием трех напряжений

"ЬХ2 ВХ "ьь1Х " И . ВХР

В момент размыканкя ключа 7 напряжение 0< достиагает значения, которое приближено можно определить по формуле

О =Ц(о =9(Оь ? к ? 0ы(къ-Оьь )(к4)

К концу первого такта запоминающий конденсатор разряжается до нуля под действием 0@ и 0 > l>, так как ключ 7 разомкнут

U =U 0 010 (ЮК0 2КБ UsblxK.4)

Подставляя значение 0< в уравнение для О+ и решая уравнение относительно

06 и ) К -К „Кя

lbbi ЬХ К к5

При условии „=-0,5, что сок -к -к ответствует соотношению К р, =g„(g p ) получаем ц «g 4Кя х4 . Х1 5Х 1 где коэффициенты К -К определяются параметрами схемы.

Во втором такте замыкаются ключи 9 и 10 и размыкаются ключи 8 и 11. Поскольку напряжение на запоминающем конденсаторе 12 равно нулю, то выходное <

5 980 1 напряжение интегратора 13 не изменяетcs. Таким образом, в установившемся режиме пульсации на выходе напряжения отсутствуют. Ключи 10 и 11 исключают влияние конечного сопротивления ключей

8 и 9 на процесс в схеме, улучшая ее работу. В частности, в каждом такте обеспечивается постоянное входное сопротивление интегратора. В переходном режиме умножитель представляется колебательным 1р звеном, в котором коэффициент колебательности и постоянная времени определяются номиналами резисторов и конденсаторов. Выбором номиналов резисторов и конденсаторов достаточно просто при заданной точности выбрать минимальное время переходного процесса, которое может составлять величину, соизмеримую с временем такта.

Технико-экономическая эффективнос ть ?0 предлагаемого технического решения заключается в повышении быстродействия выполнения операции умножения в101000 раэ в зависимости от требуемой точности и независимо от скважности 25 входных сигналов. Это определяется тем, что в предлагаемом умножителе время .переходного процесса может быть достигнуто 2 — 6 периодов ШИМ сигнала при практически нулевой пульсации выходного Зф напряжения. В известных умножителях величина пульсаций зависит от постоянной времени фильтра. Для достижения пульсации 1% выходного напряжения в прототиге, работаюшем с точностью 1%, постоянная времени фипьтра Тф должка .быть равна 100 периодов ШИМ сигнала, тогда время переходного процесса при скачкообразном входном сигнале равно 600 периодов ШИМ сигнала, т. е; 100 - е

3000 раз и выше чем в предлагаемом умножителе. При необходимости получить уровень пульсаций 0,1% и точность 0,1% быстродействие снижается еше более, чем на порядок. Таким образом, чем точнее необходимо реализовать устройство умножения и чем ниже нужно получить уровень пульсаций выходного напряжения тем выше эффективность применения предлагаемого устройства.

50 формула изобретения

Четырехквадрантный . умножитель сигналов постоянного тока, содержашнй инвер- 55

04 6 тор, вход которого является первым информационным входом умножителя, первый ключ, информационный вход которого подключен к выходу инвертора, компаратор, входы которого являются соответственно вторым информационным и тактовым входами умножителя, а выход подключен к управляющему входу первого ключа, интегратор, выход которого является выходом умножителя и три масштабных резистора, первые выводы которых объединены,, второй вывод первого масштабного резистора подключен к входу инвертора, второй вывод второго масштабного резистора подключен к выходу интегратора, а второй вывод третьего масштабного резистора подключен к выходу первого ключа, о. тл и ч а ю ш и и с я тем, что, с целью повышения его быстродействия, в него введены последовательно соединенные формирователь импульсов и триггер управления, четвертый и патый масштабные резисторы, второй, третий; четвертый и пятый ключи и запоминающий конденсатор, вход формирователя импульсов подключен к второму входу компаратора. первый выход триггера управления подключен к управлякецим входам второго и пятого ключей, а второй выход триггера управления подключен к управляющим входам третьего и четвертого ключей, информационные входы второго и четвертого ключей объединены и подключены к первому выводу третьего масштабного рж истора, выход второго ключа и ииформащионный вход третьего ключа объединены и через эапоминакмций конденсатор, подключены к шине нулевого потенциала, первый вывод четвертого масштабного резистора подключен к выходу третьего клича, а первый вывод пятого масштабного резистора подключен к информационному входу пятого ключа, вторые выводы четвертого и пятого масштабных резисторов объединены и подключены к входу интегратора, выходы четвертого и пятого ключей подключены к шине нулевого потенциала.

Источники информации, принятые во внимание при экспертизе

1. Аналоговые и цифровые интегральные схемы. Под ред. В. С. Якубовского, N., Сов. радио, 1979, с. 238 - 239.

2. Грэм Дж. Проектирование и применение операционных усилителей. М., Мир", 1974, с. 196 - 298 (прототип).

980 104

r»

1 !

L з

Составитель Т. Сапунова /

Техред М,Гергепь Корректор О. Билак

Редактор H. Гришанова

Филиал ППП Патент", r. Ужгород, ул. Проектная, 4

Заказ 9361/39 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5